存储系统

总的浏览

一.存储器概述

首先扯一会无聊的概念

按计算机作用(层次)

- 主存(内存):存放计算机运行期间所需的的程序和数据 【Cpu直接随机进行访问】

- 辅存(外存):存放暂时不用的程序和数据及需要永久性保存的信息【需要调入主存才被Cpu访问】

- cache:主存和Cpu之间

按存储介质

- 磁表面存储器(磁带)

- 磁芯存储器

- 半导体存储器(MOS)

- 光存储器(光盘)

按信息可保存性

断电后 存储信息是否消失

- 易失性存储器:RAM

- 非易失性存储器:ROM

按存取方式

- 随机存储器:RAM

- 只读存储器:ROM

- 串行访问存储器:顺序存取(磁带) 直接存取(磁盘 光盘)

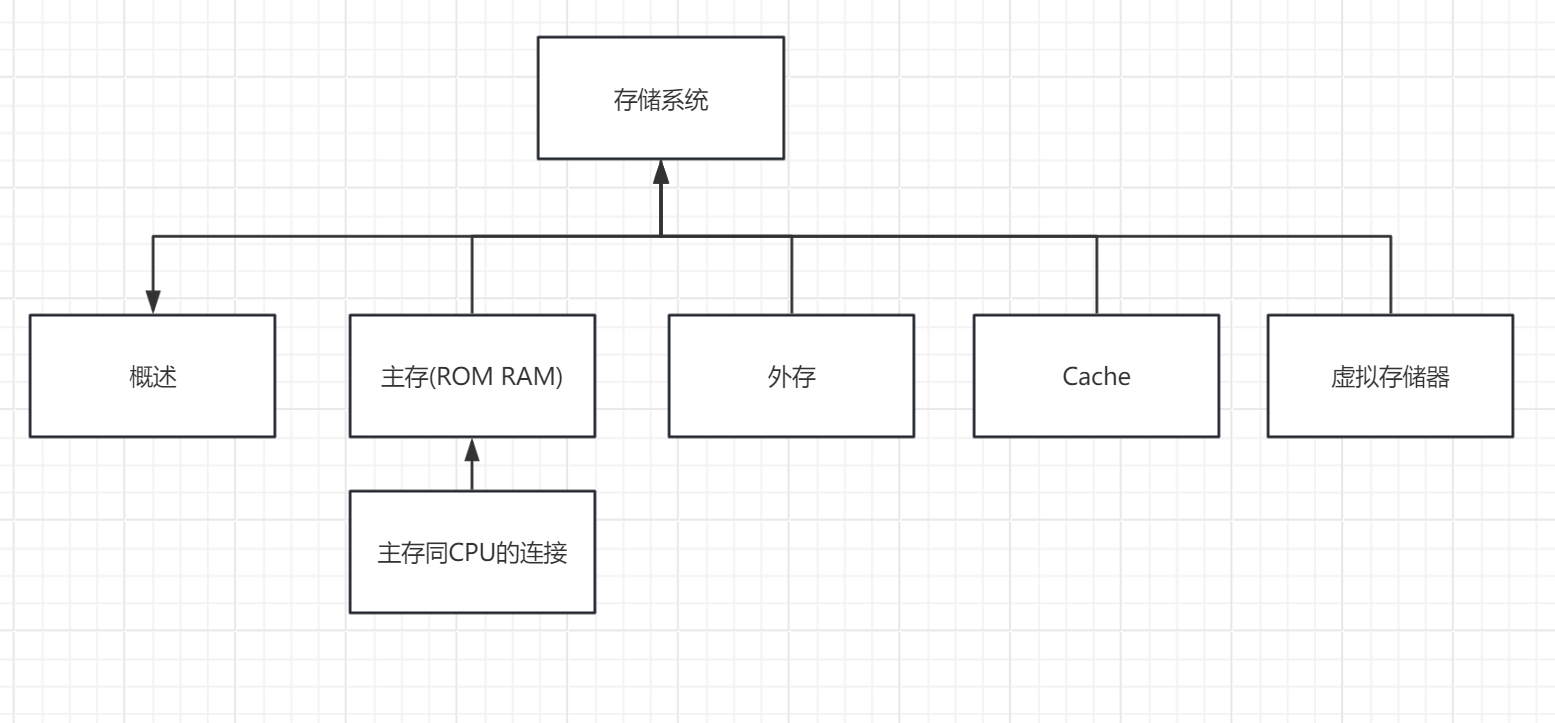

多级层次存储系统

核心:上一层的存储器作为低一层存储器的高速缓存

cache和内存可以直接和CPU交换信息

主存-cache 对所有程序员透明 解决速度问题

主存-辅存 对应用程序员透明 解决容量问题

然后看比较重要的东西

存储器的性能指标

- 存储容量

- 单位成本

- 存储速度

主要计算为 存储容量的计算 和 存储速度计算

公式:

存储容量=存储字数 X 字长

如:MB=M X B(8bit位)

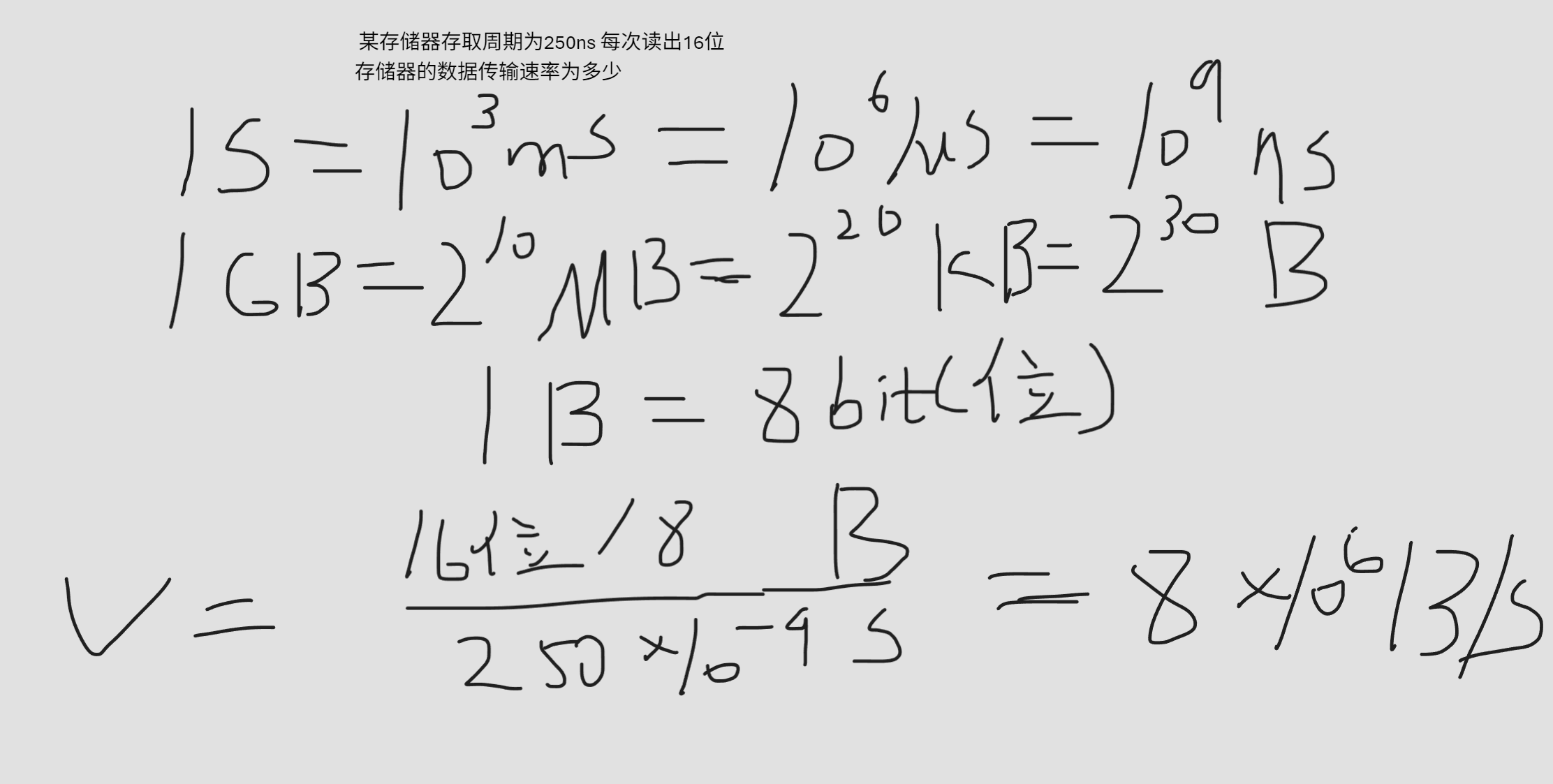

数据传输速率= 数据宽度/存取周期

(每秒传送信息的位数) B/s bit/s

通常存取周期>存取时间 (两者不相等概念)

看题看题:

某存储器存取周期为250ns 每次读出16位 存储器的数据传输速率为多少

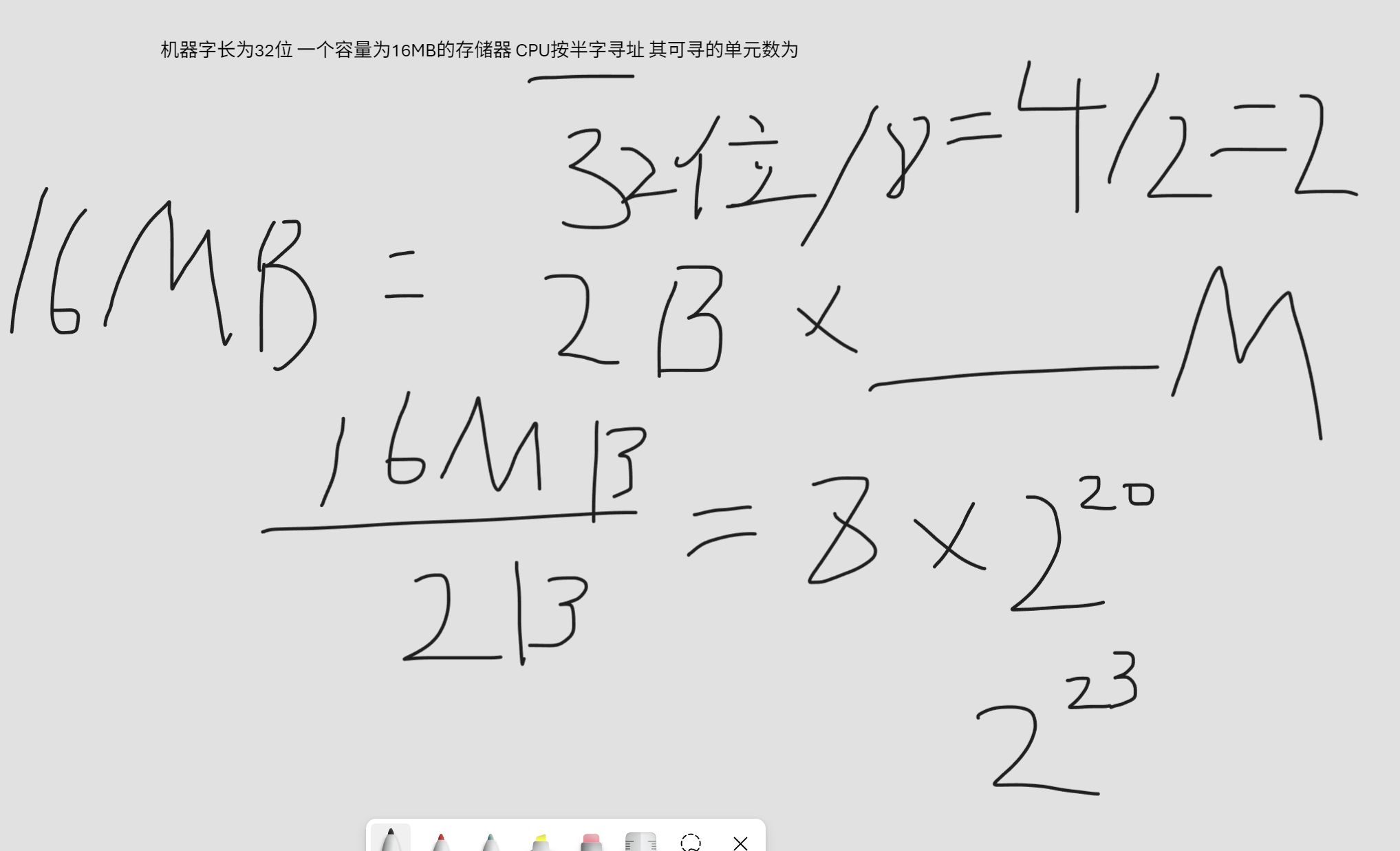

机器字长为32位 一个容量为16MB的存储器 CPU按半字寻址 其可寻的单元数为

CD-ROM 光盘存储器 采用串行存取 ROM和RAM都是随机存取

二.主存

其实主要就是ROM和RAM

ROM 只读存储器 非易失性

介绍几个ROM

- MROM 掩模式只读存储器

- PROM 一次可编程只读存储器

- EPROM 可擦除可编程只读存储器

- Flash存储器 (U盘 SD卡) V写>V读

- SSD 固态硬盘

大概没啥可重要的 因为它是固定不变的

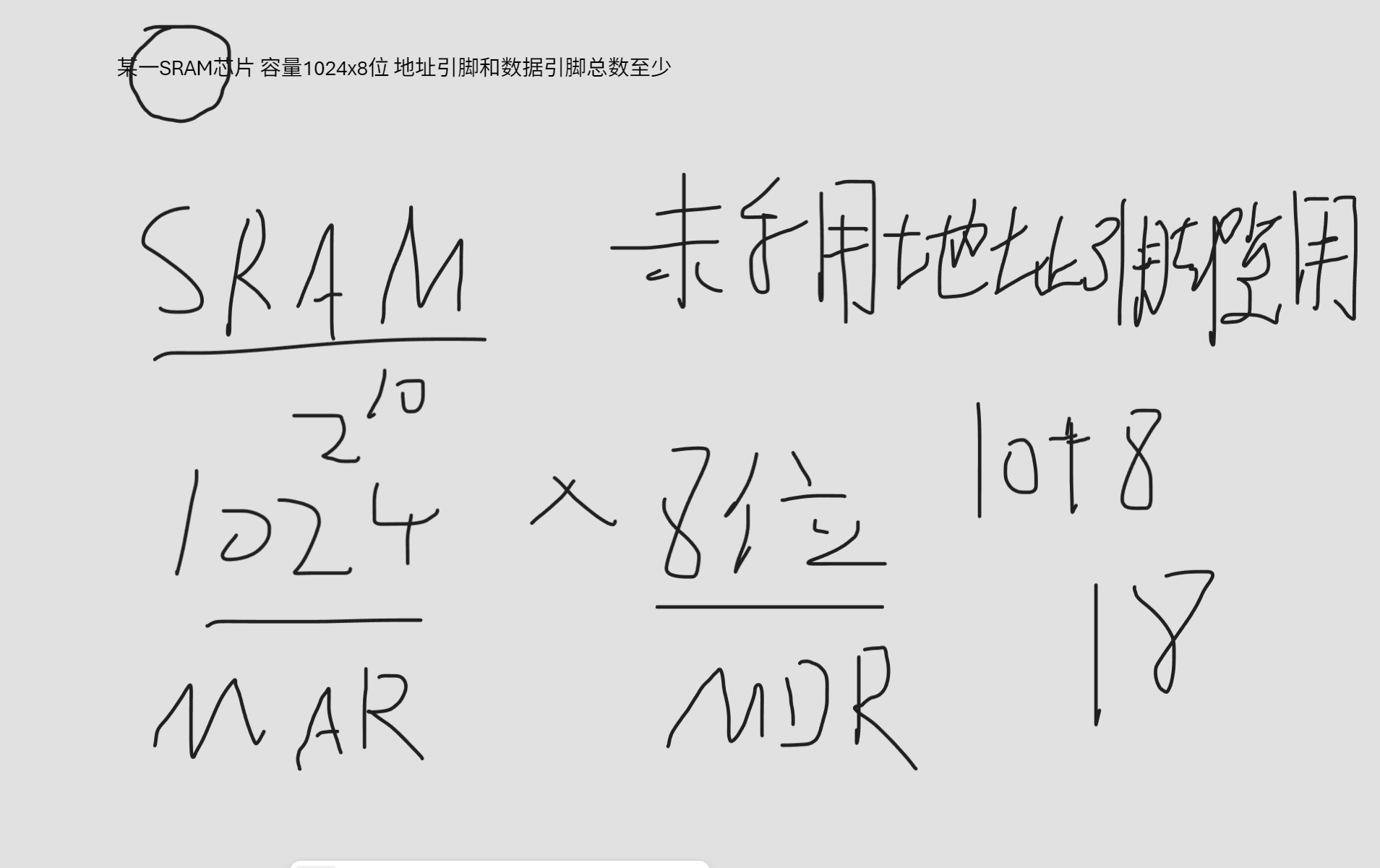

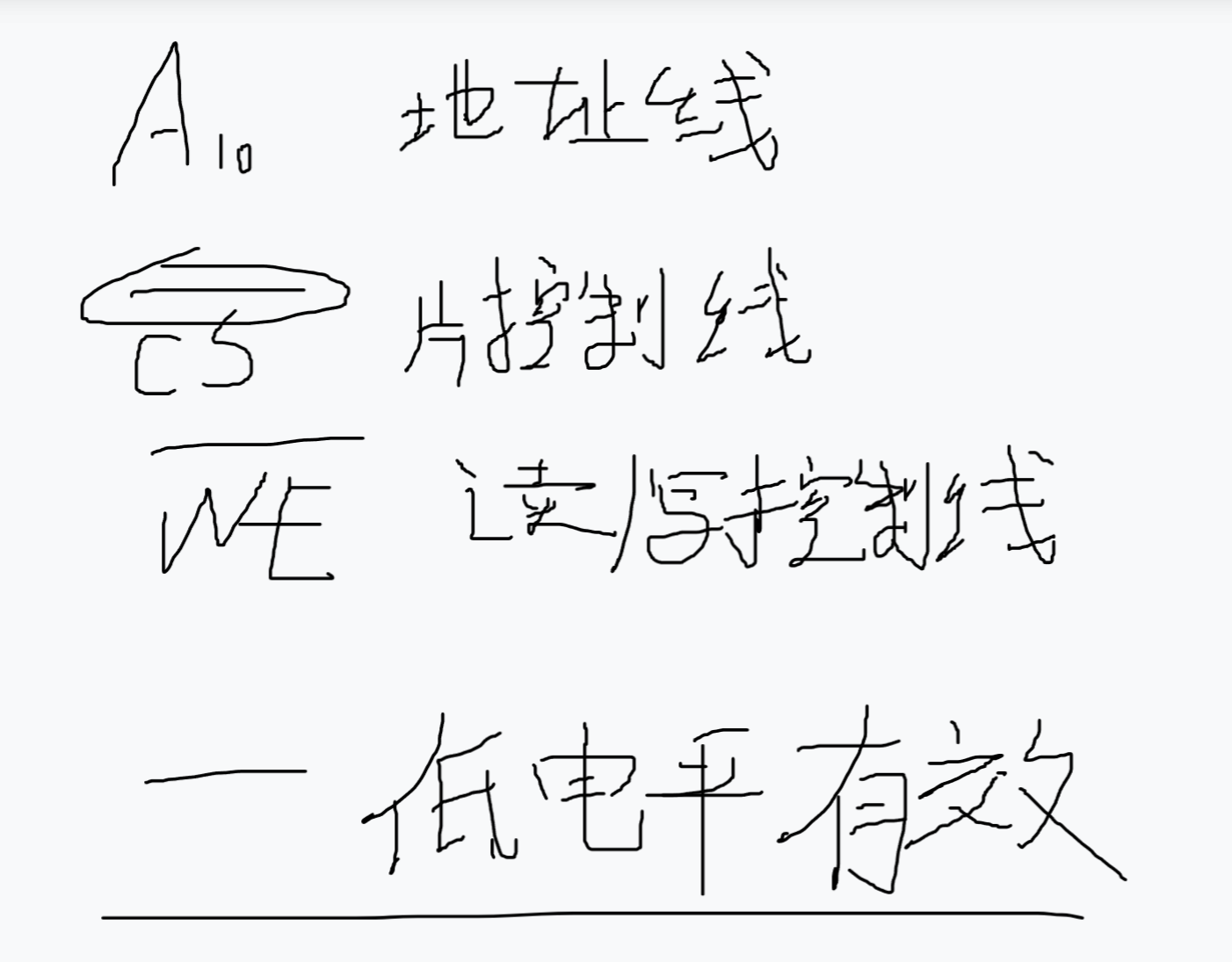

MDR(存储器地址数据器)位数=数据线位数

MAR(存储器地址寄存器)位数=地址线位数

地址线位数决定了主存地址空间的最大可寻址范围

RAM 随机存储器 易失性

- SRAM(静态随机存储器) cache 非破坏性读出

- DRAM(动态随机存储器) 集成度高

当然静态死的没啥好研究的

1.DRAM需要刷新:

- 集中刷新:有死区

- 分散刷新:工作周期两个(读/写) 无死区

- 异步刷新:死区分布性

DRAM:

刷新对CPU透明

刷新单位是行

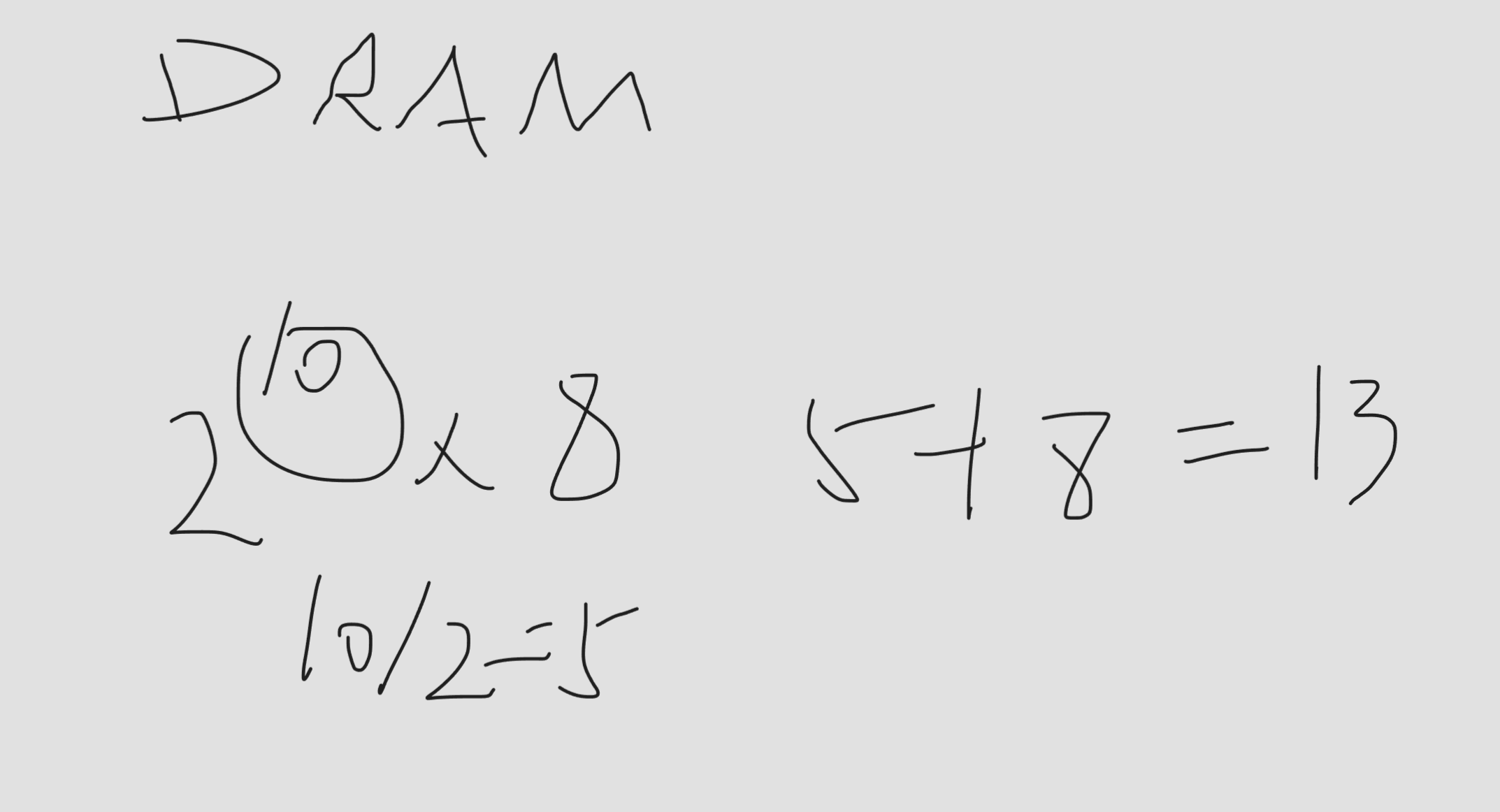

地址引脚复用技术:地址引脚数减半

行数r 列数c 2的n次方=rxc

为减少刷新开销 r<=c 行数较少

DRAM和SRAM区别

然后再介绍个多模块存储器

核心:利用空间并行技术

多体并行存储器:每个模块相同容量和存取速度 独立又可交叉工作

上面扯太多概念 直接用题目来说明这内容的考点

某一SRAM芯片 容量1024x8位 地址引脚和数据引脚总数至少

注意是SRAM 如果是DRAM的话 就要采用地址引脚复用技术

某一DRAM芯片 采用地址复用技术 容量为1024x8位 地址引脚和数据引脚总数至少

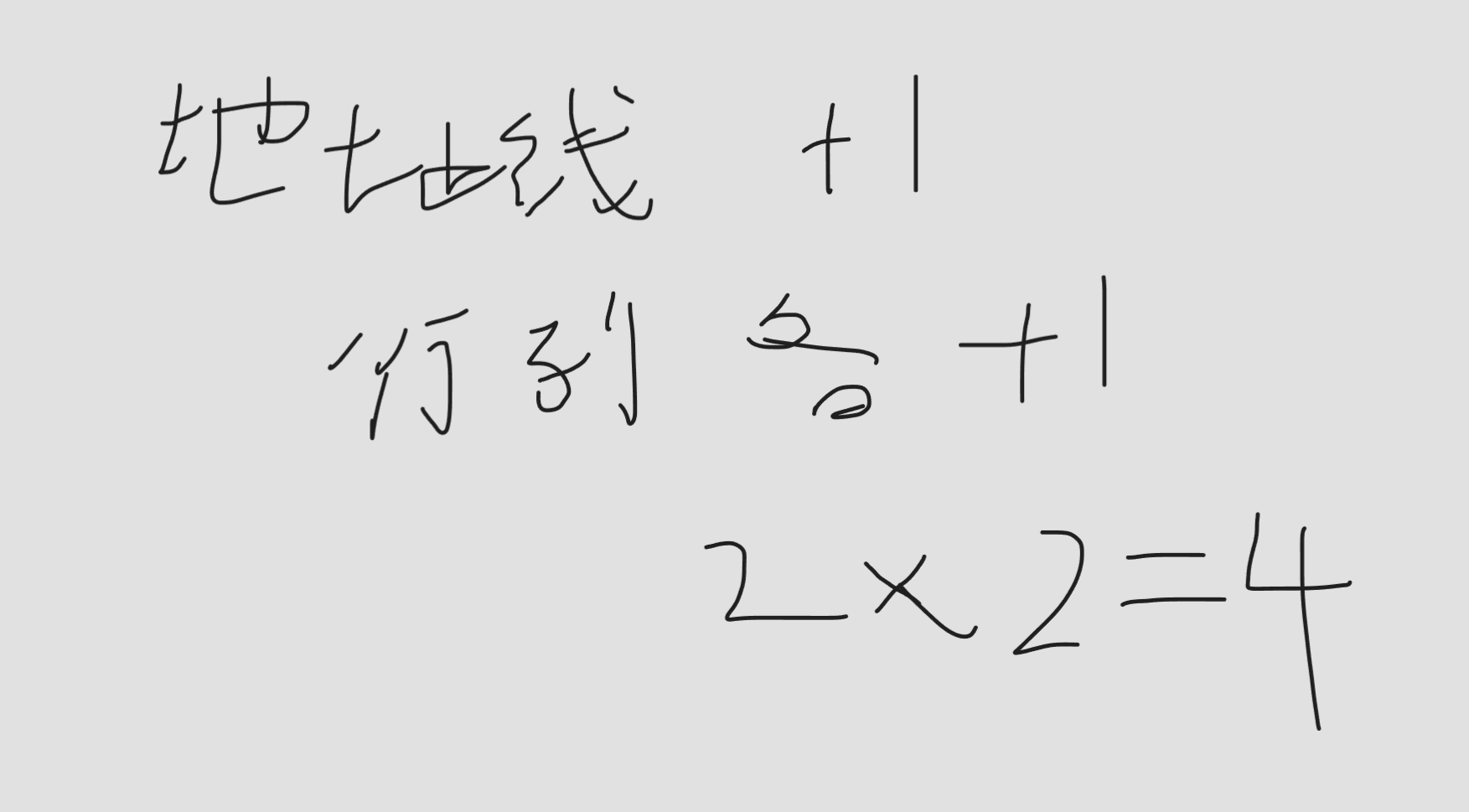

新一代DRAM芯片 地址线至少增加1根 则容量至少提高到原来的多少倍

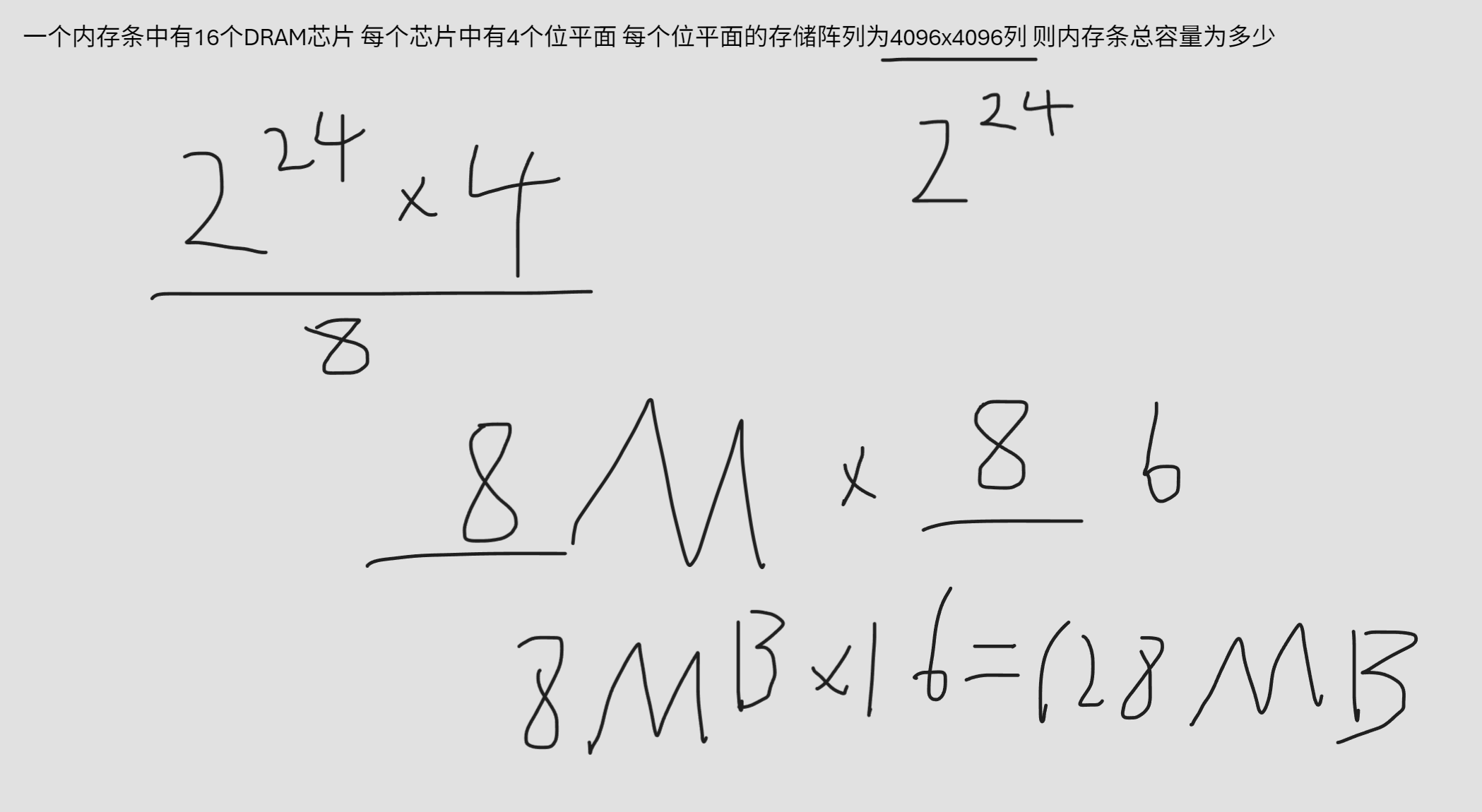

一个内存条中有16个DRAM芯片 每个芯片中有4个位平面 每个位平面的存储阵列为4096x4096列 则内存条总容量为多少

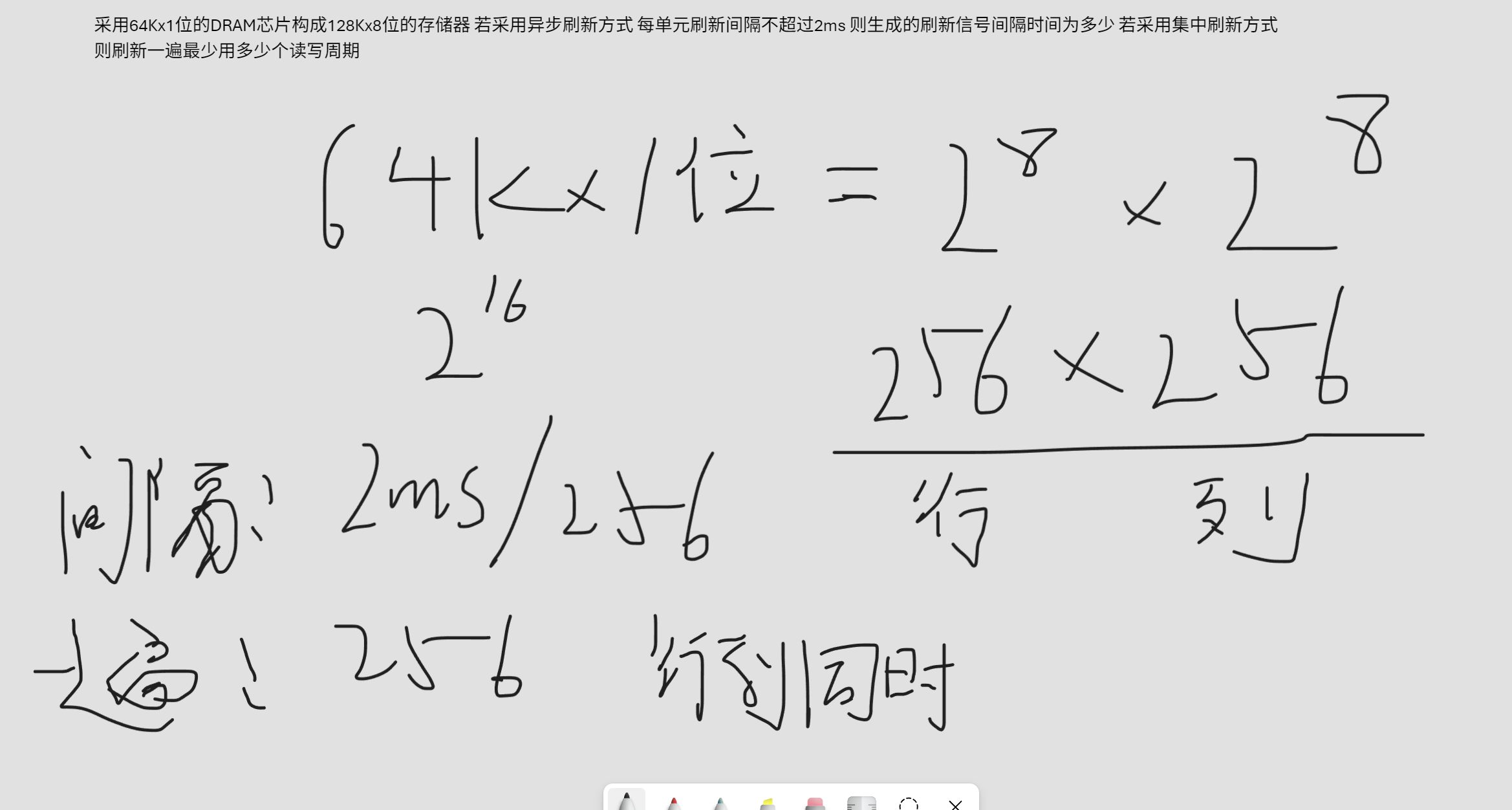

采用64Kx1位的DRAM芯片构成128Kx8位的存储器 若采用异步刷新方式 每单元刷新间隔不超过2ms 则生成的刷新信号间隔时间为多少 若采用集中刷新方式 则刷新一遍最少用多少个读写周期

一个四体并行低位交叉存储器 每个模块的容量是64Kx32位 存取周期位200ns 总线周期为50ns 在200ns内 存储器可以向CPU提供多少位二进制信息

一个存储周期: 32x4=128位

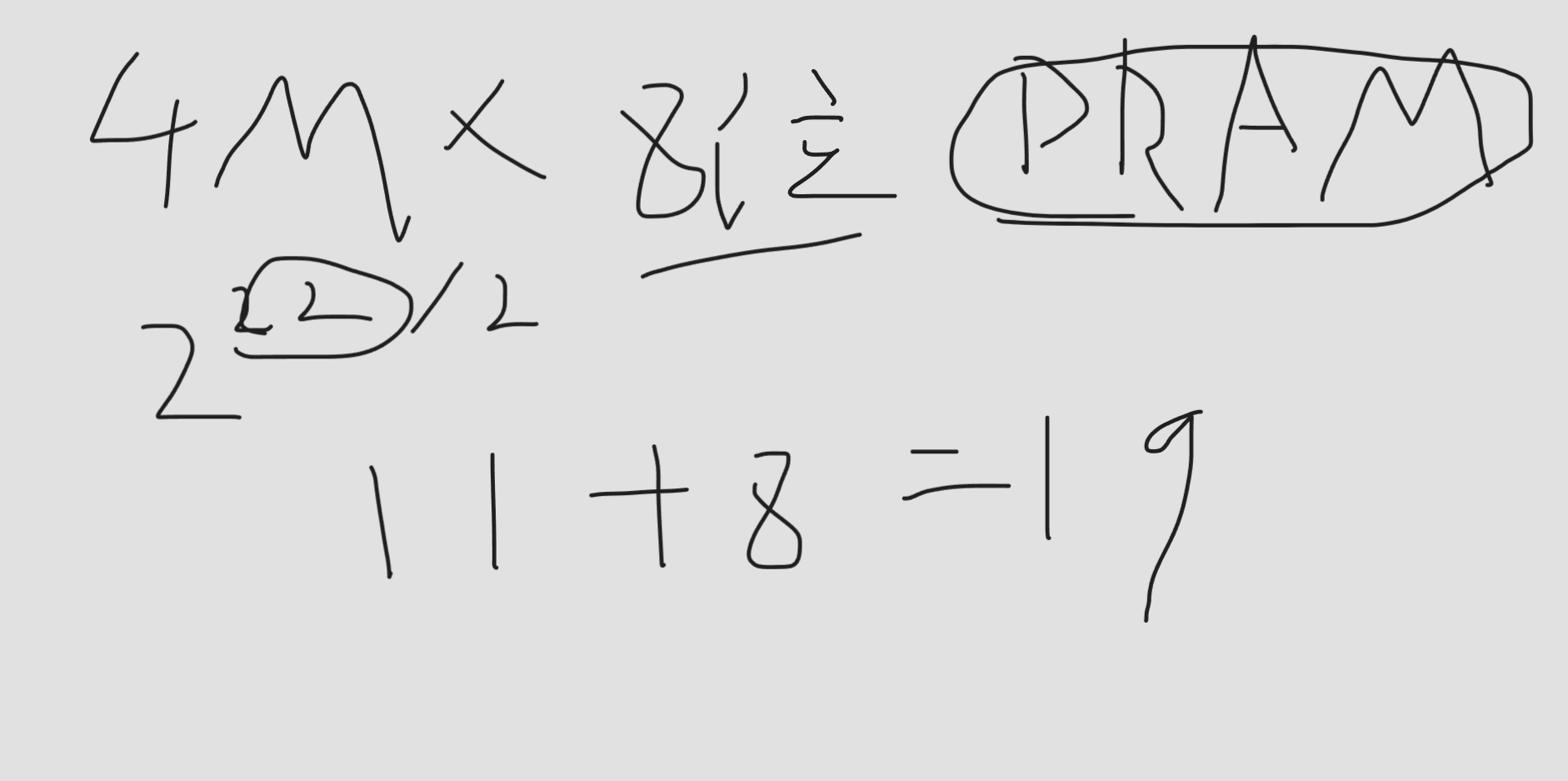

2014 某容量256MB的存储器由若干4Mx8位的DRAM芯片构成 该DRAM芯片的地址引脚和数据引脚总数

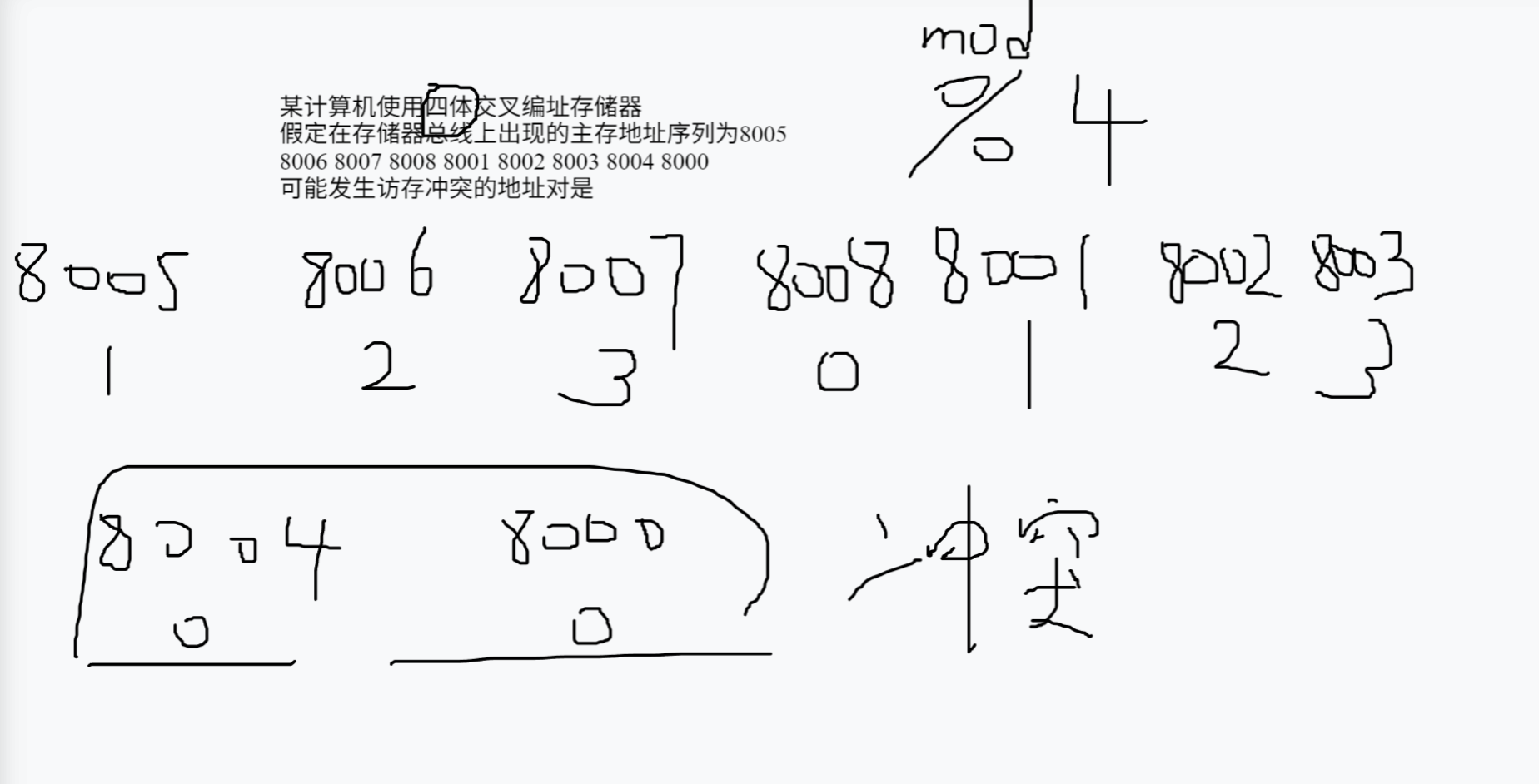

某计算机使用四体交叉编址存储器 假定在存储器总线上出现的主存地址序列为8005 8006 8007 8008 8001 8002 8003 8004 8000 可能发生访存冲突的地址对是

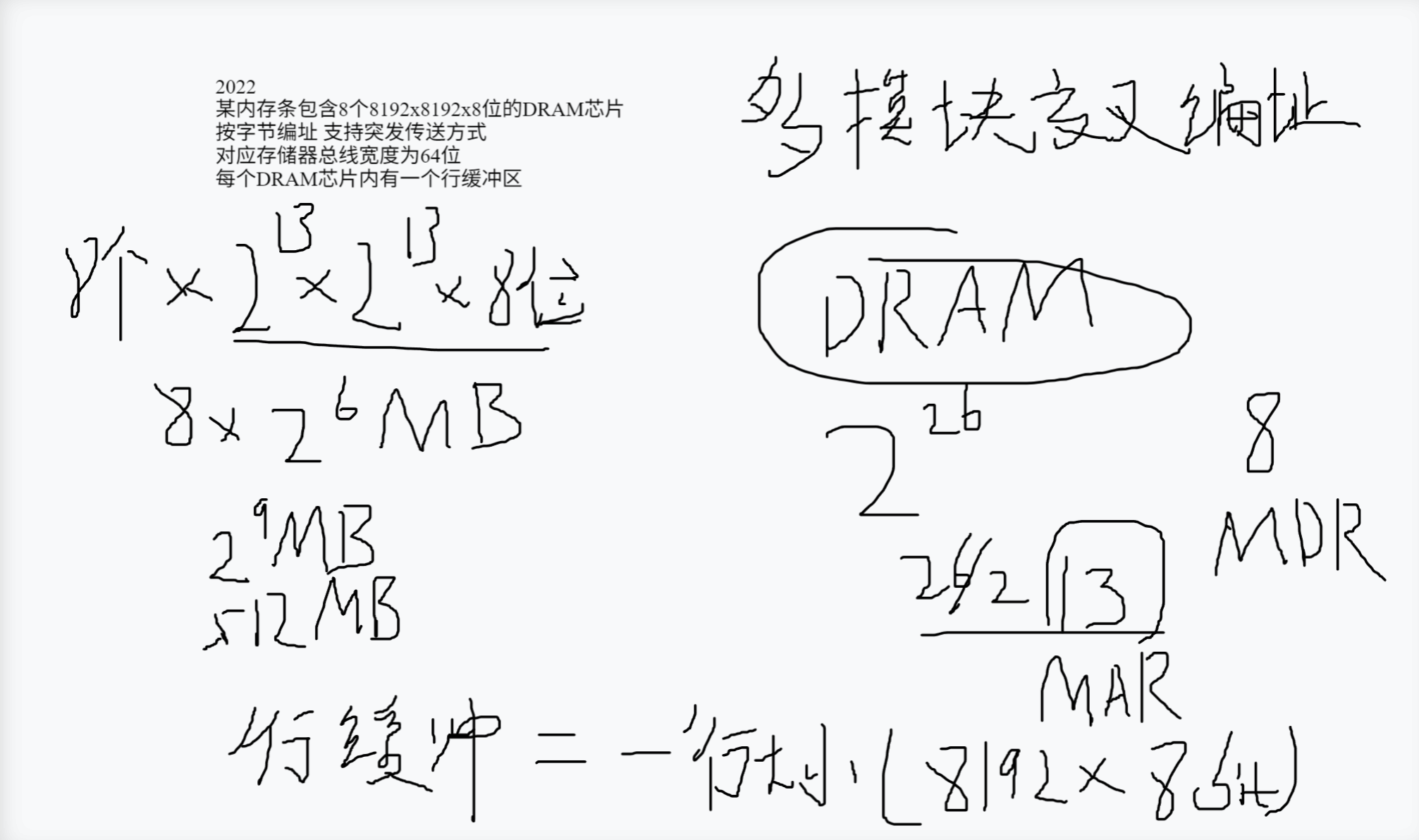

2022 某内存条包含8个8192x8192x8位的DRAM芯片 按字节编址 支持突发传送方式 对应存储器总线宽度为64位 每个DRAM芯片内有一个行缓冲区

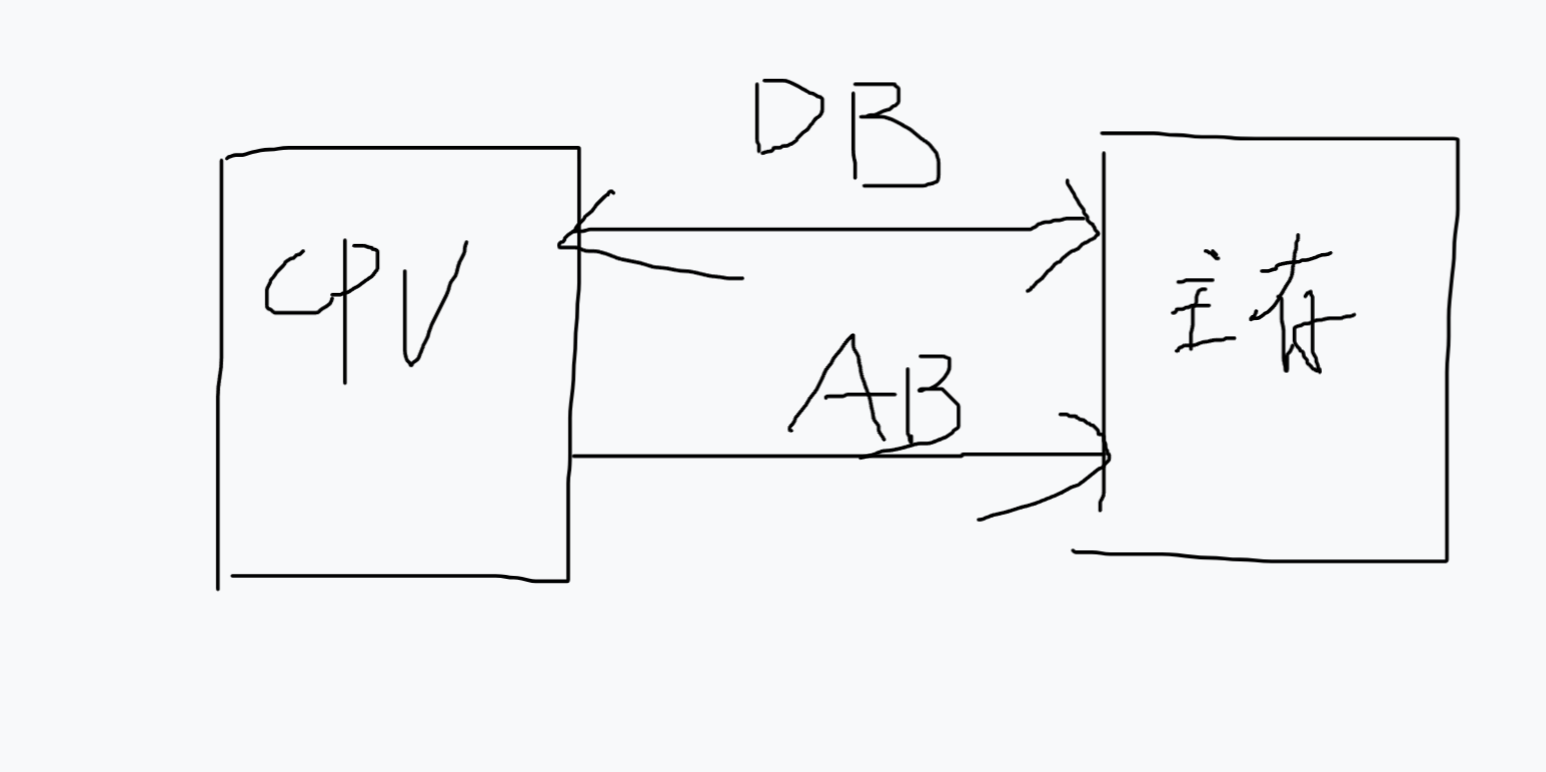

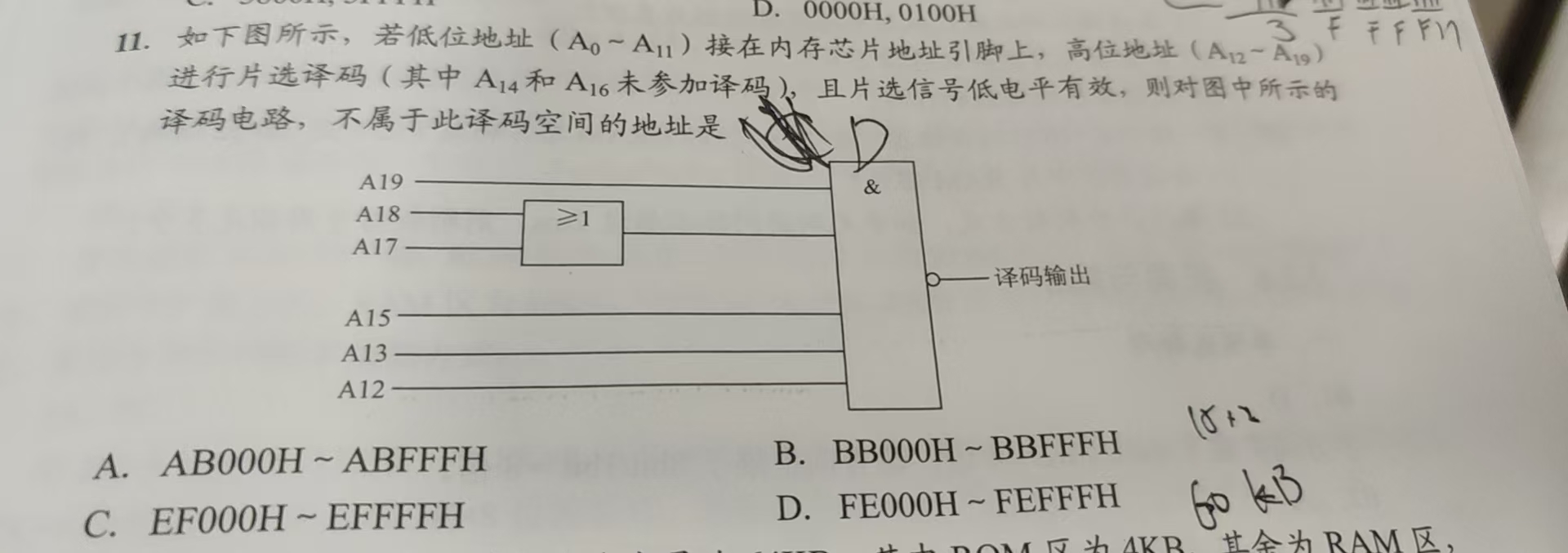

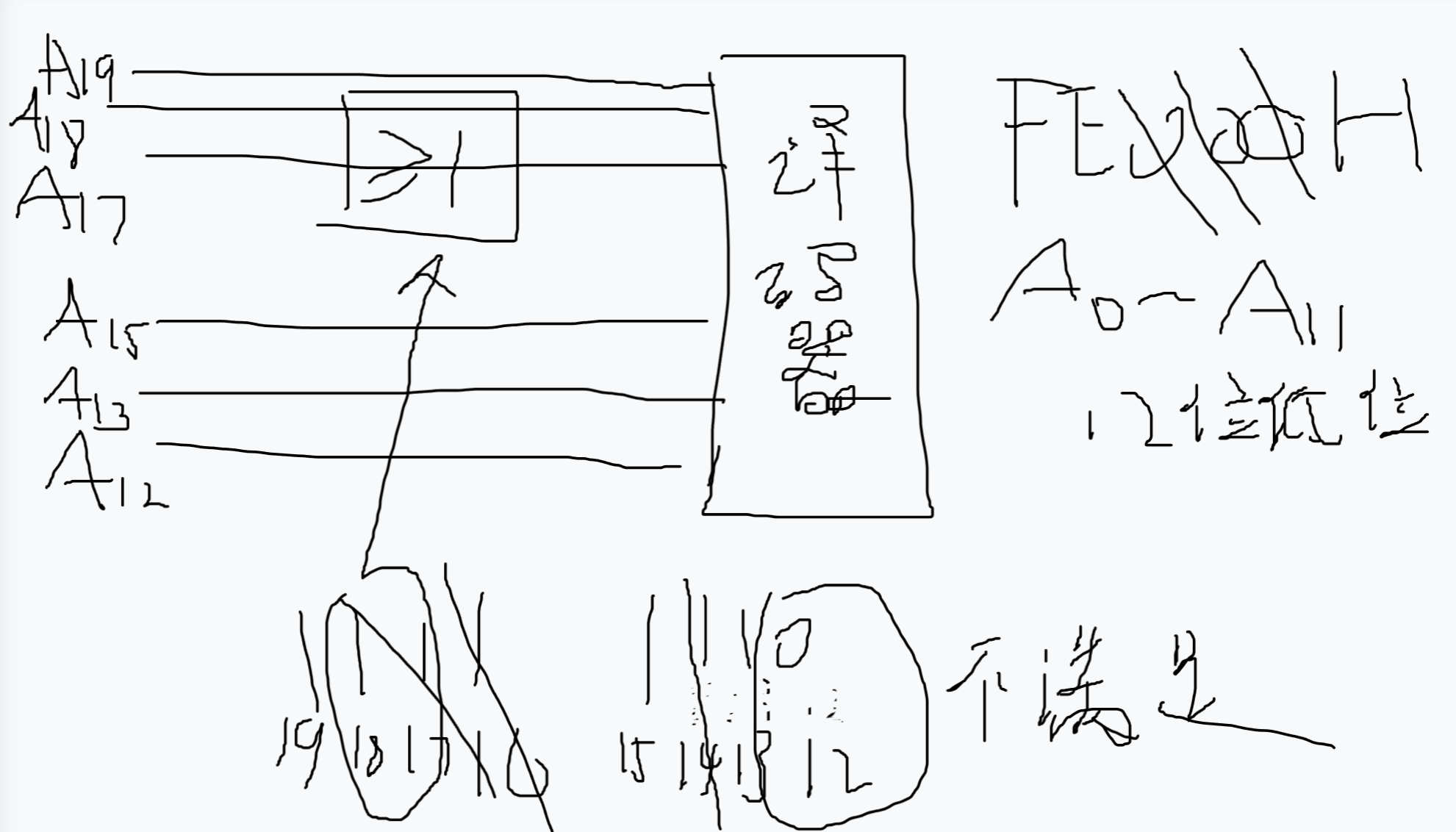

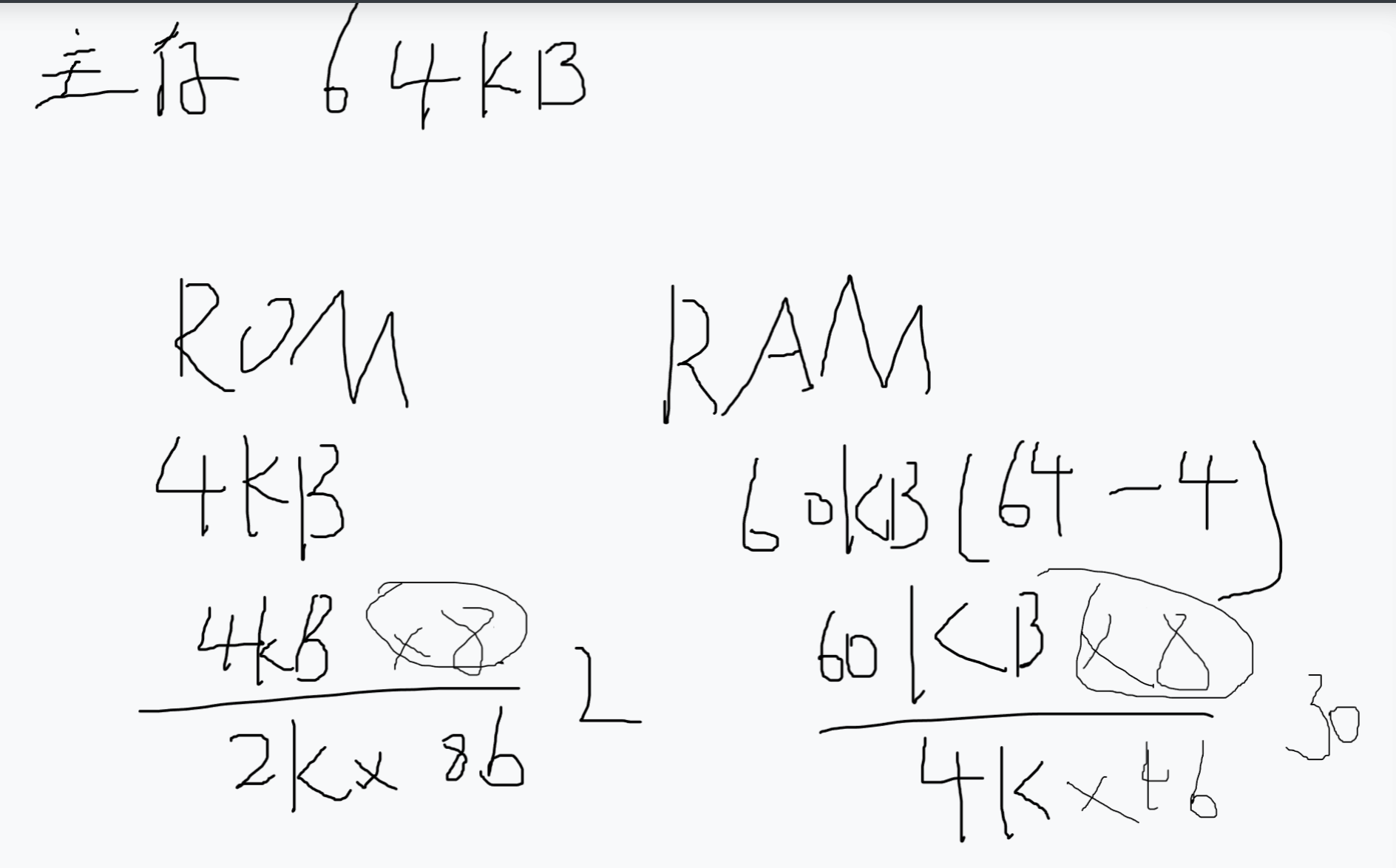

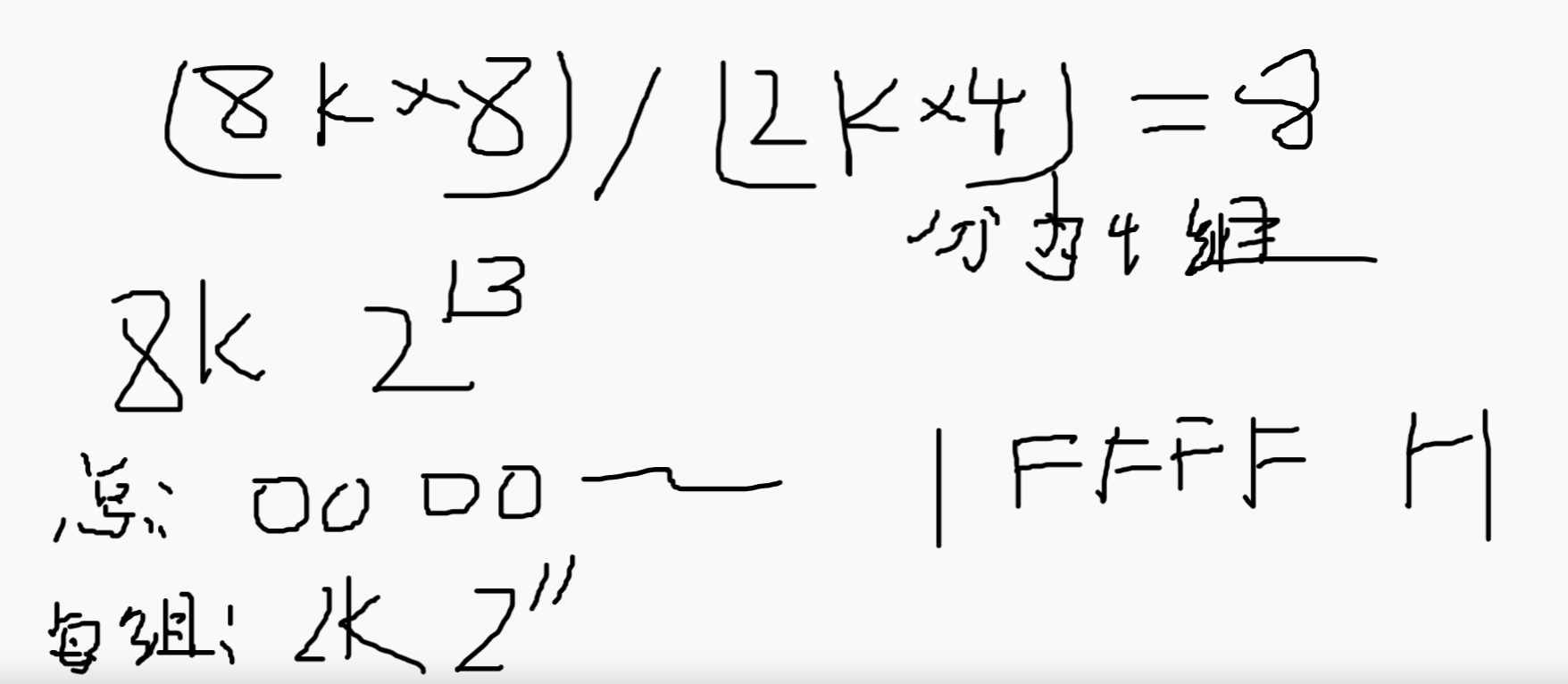

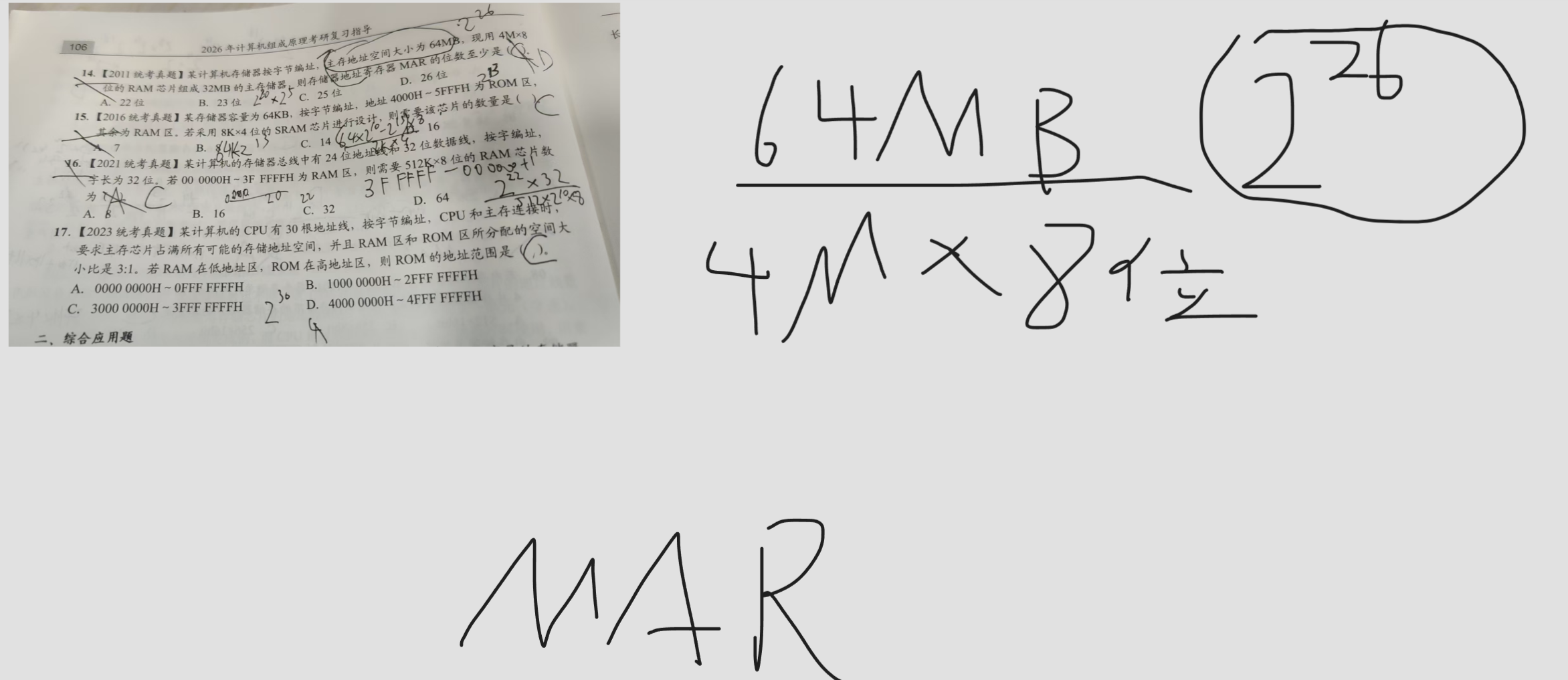

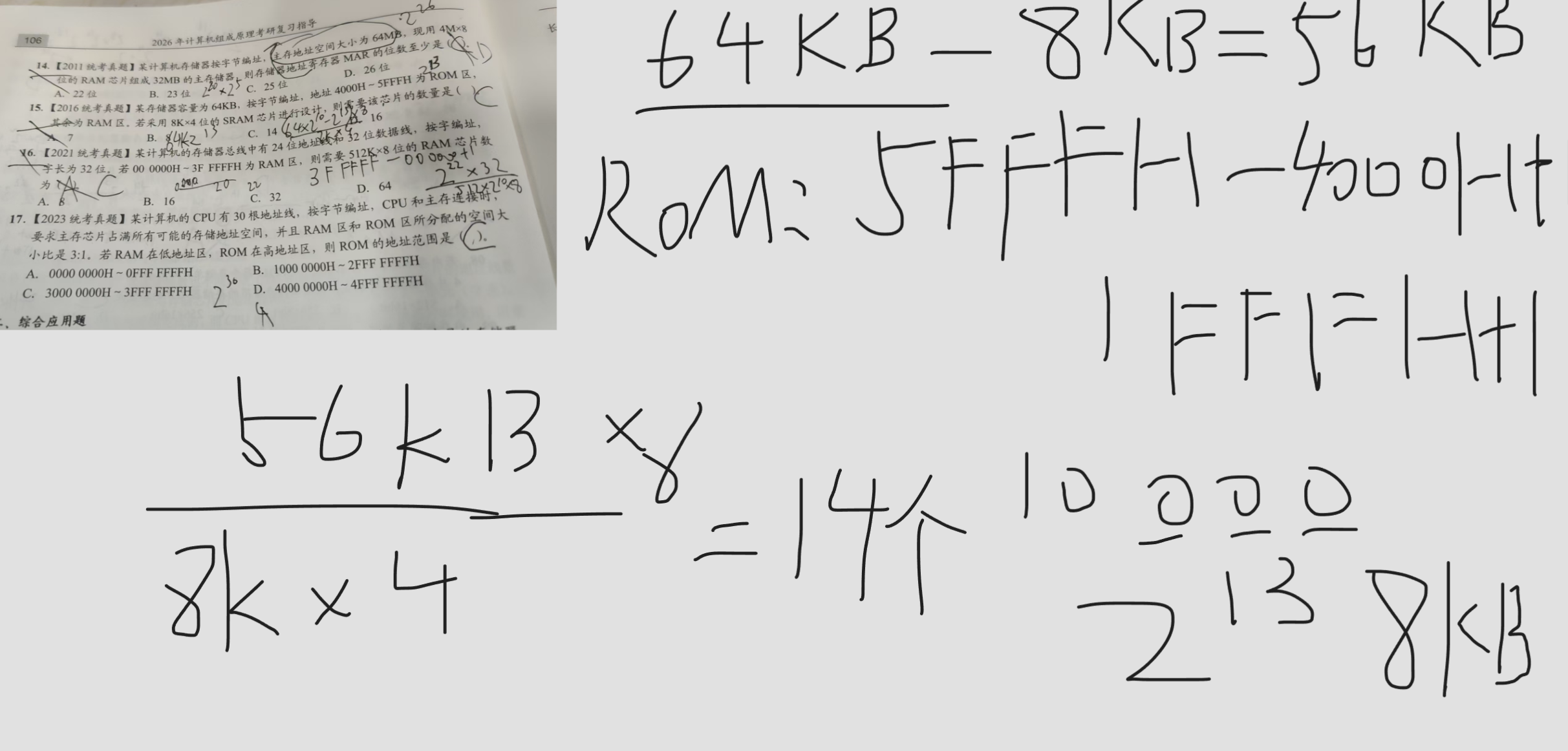

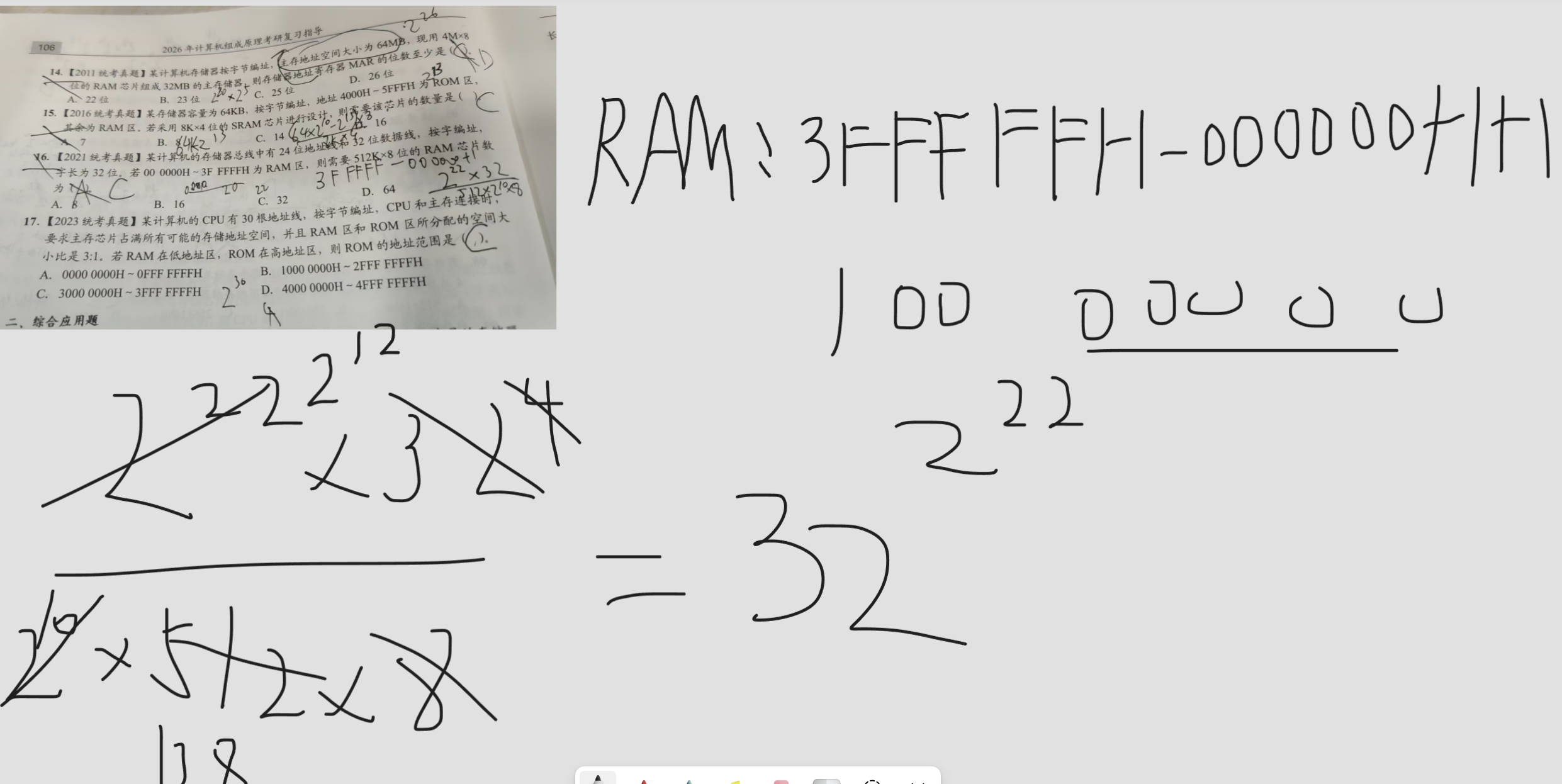

三.主存同CPU的连接

这内容同后面的外存简单

所谓连接就是:主存和CPU之间通过数据总线 地址总线 控制总线连接

主要的是主存容量的扩展

- 位扩展法

- 字扩展法

- 字位扩展法

位扩展法:

系统数据线数>存储芯片字长 需要增加存储字长 扩展位

字扩展法:

系统地址线位数>存储芯片地址线位数 扩展存储子数量 扩展字

字位同时扩展法:

既扩展位 同时扩展字

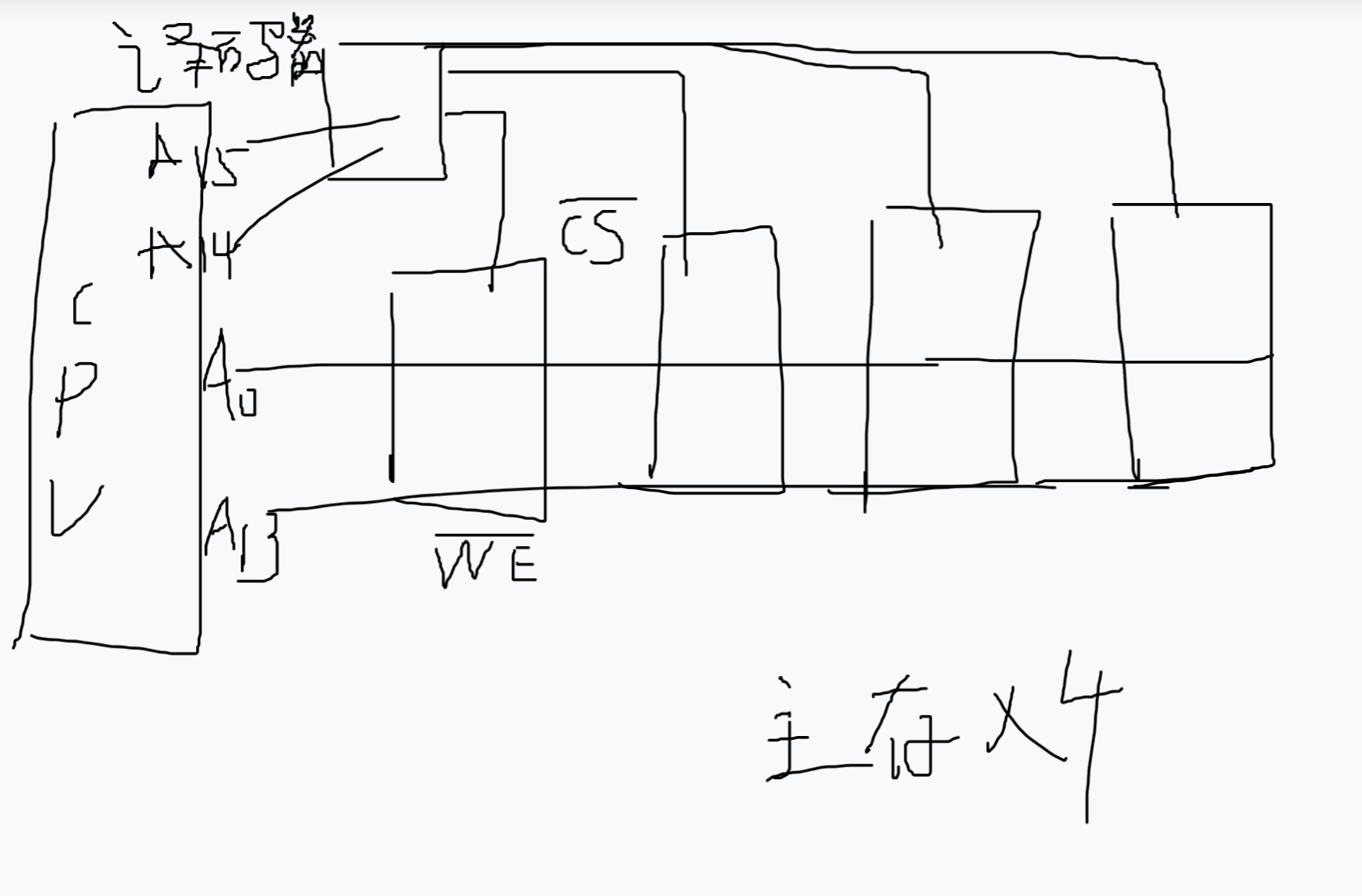

随后来介绍下实物模拟图

首先需要弄清几个东西

具体是个怎样的如下:

我不画了 全文字叙述:

会有一个译码器 连接两个地址线 解析成四个 如传过来01 则对应十进制数 1

然后取反变成0 CS上面有横线 低电平有效 传递给2号

上述采用的就是线选法:片选地址线每次寻址时只能有一位有效

其他实在没啥好总结的 涉及不到考察内容 所以直接看题来理解

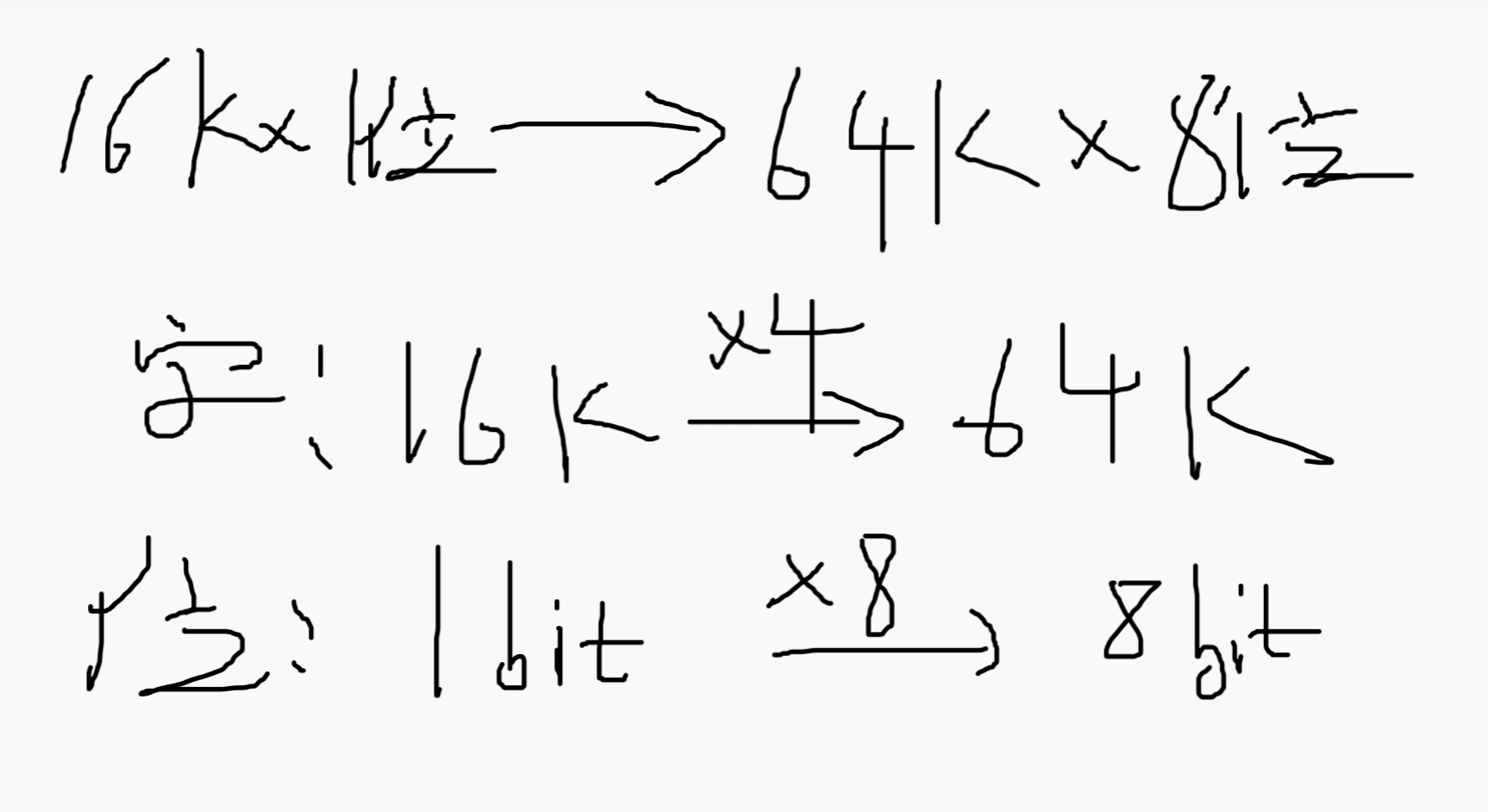

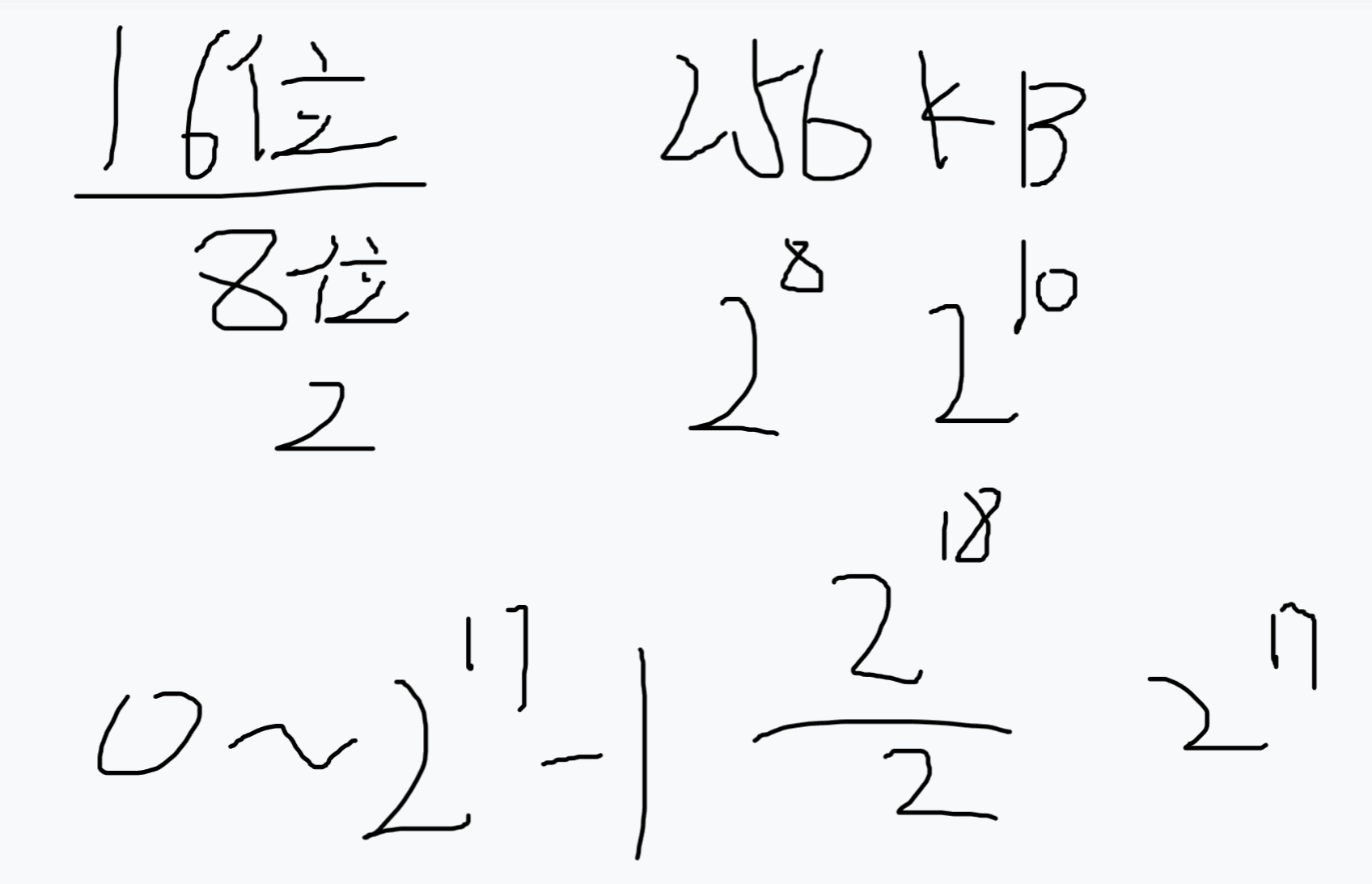

用存储容量位16Kx1位的存储器芯片来组成一个64Kx8位的存储器 则在字方向和位方向分别扩展了多少倍

某计算机字长位16位 存储器容量为256KB CPU按字寻址 其寻址范围是

地址线的位数决定了最大可寻址范围

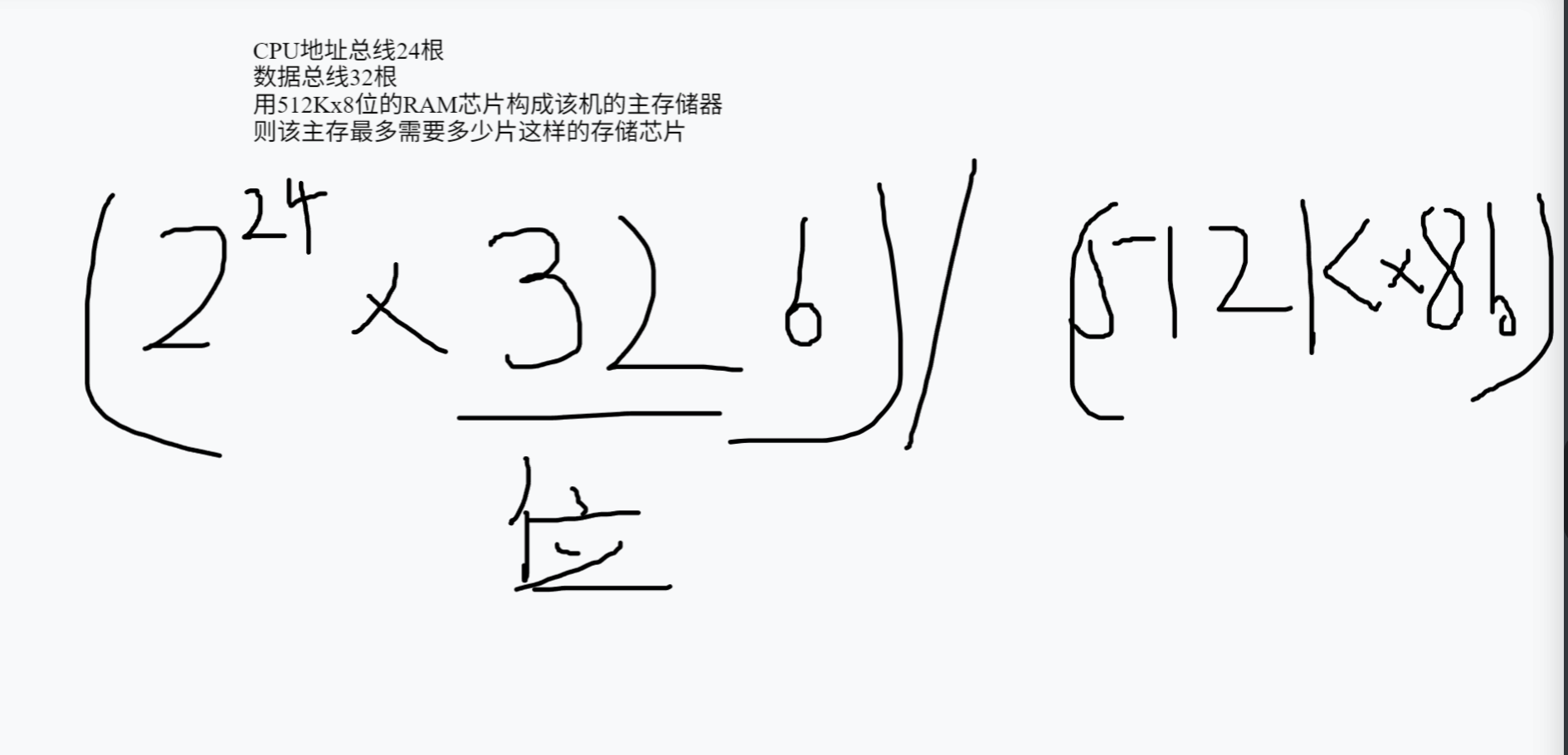

CPU地址总线24根 数据总线32根 用512Kx8位的RAM芯片构成该机的主存储器 则该主存最多需要多少片这样的存储芯片

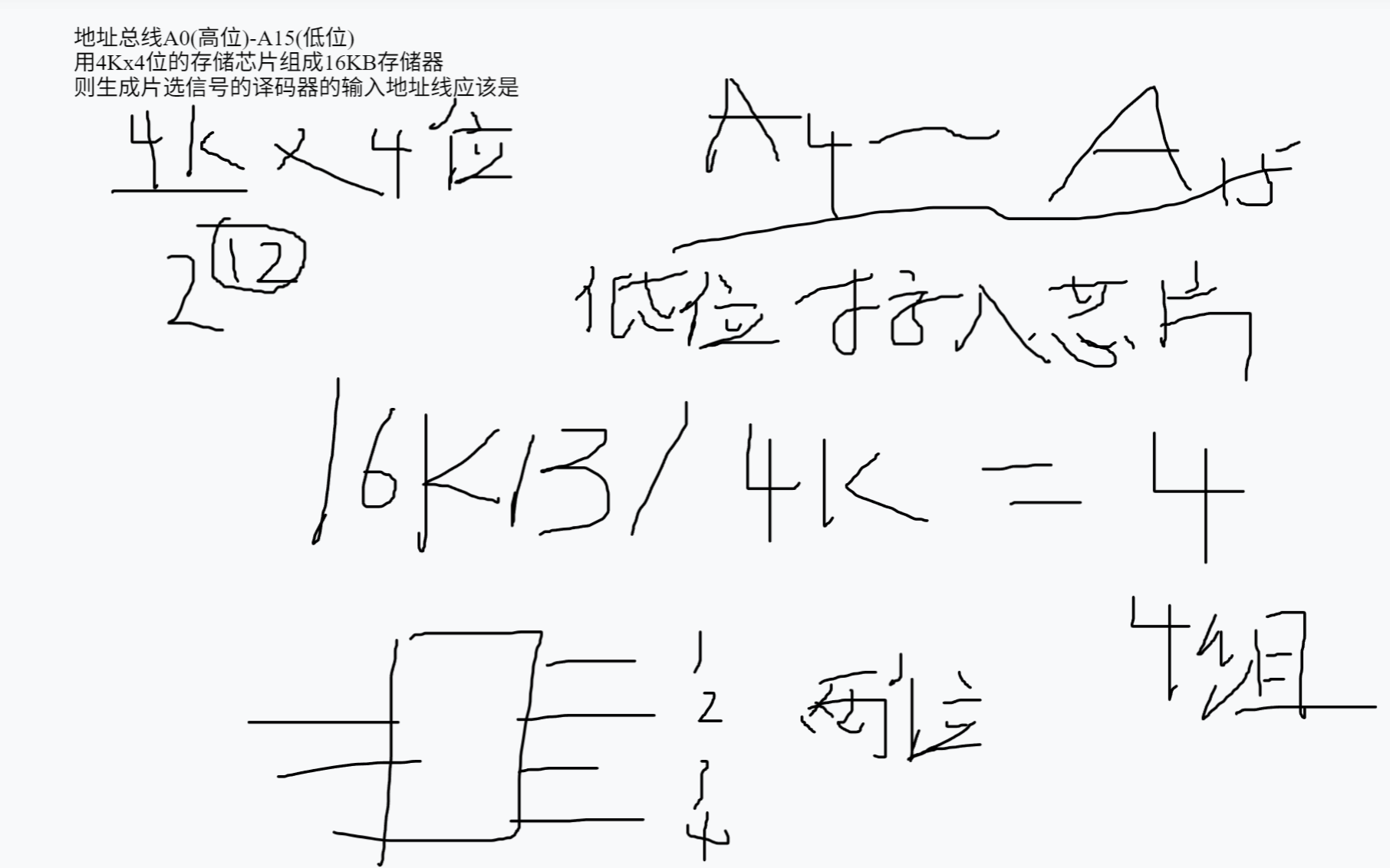

地址总线A0(高位)-A15(低位) 用4Kx4位的存储芯片组成16KB存储器 则生成片选信号的译码器的输入地址线应该是

这道题不能糊弄 首先确定地址线数 低位开始数够接入芯片 然后看需要几个这样的存储芯片 2个输入就能产生2的2次方 4个信号

内存按字节编址 地址从90000H到CFFFFH 若用存储容量为16Kx8位的芯片构成该内存 至少需要的芯片数是多少

接下来都是类型题 先求出地址线数 默认数据线为8位 然后知道内存多大 然后再去除

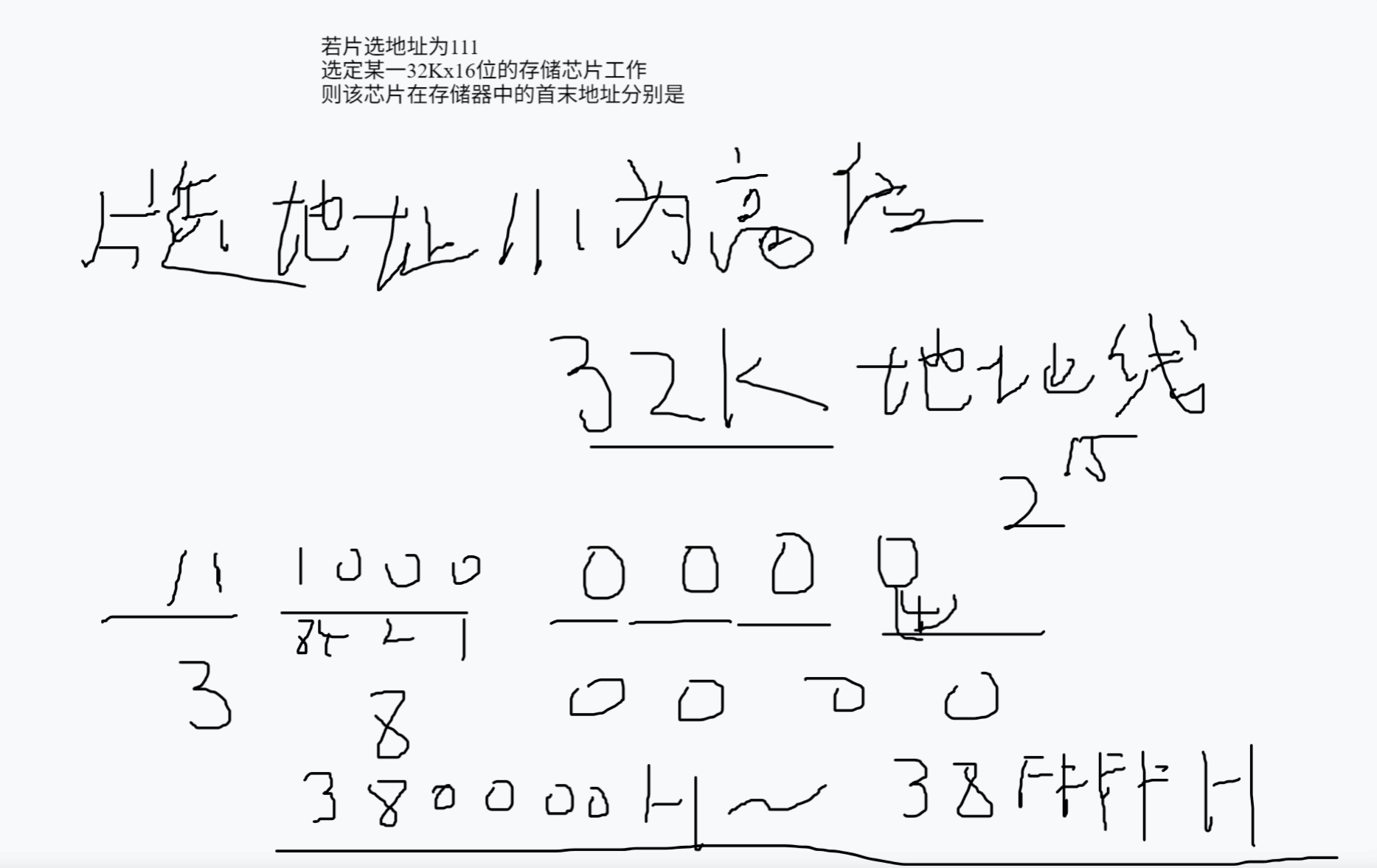

若片选地址为111 选定某一32Kx16位的存储芯片工作 则该芯片在存储器中的首末地址分别是

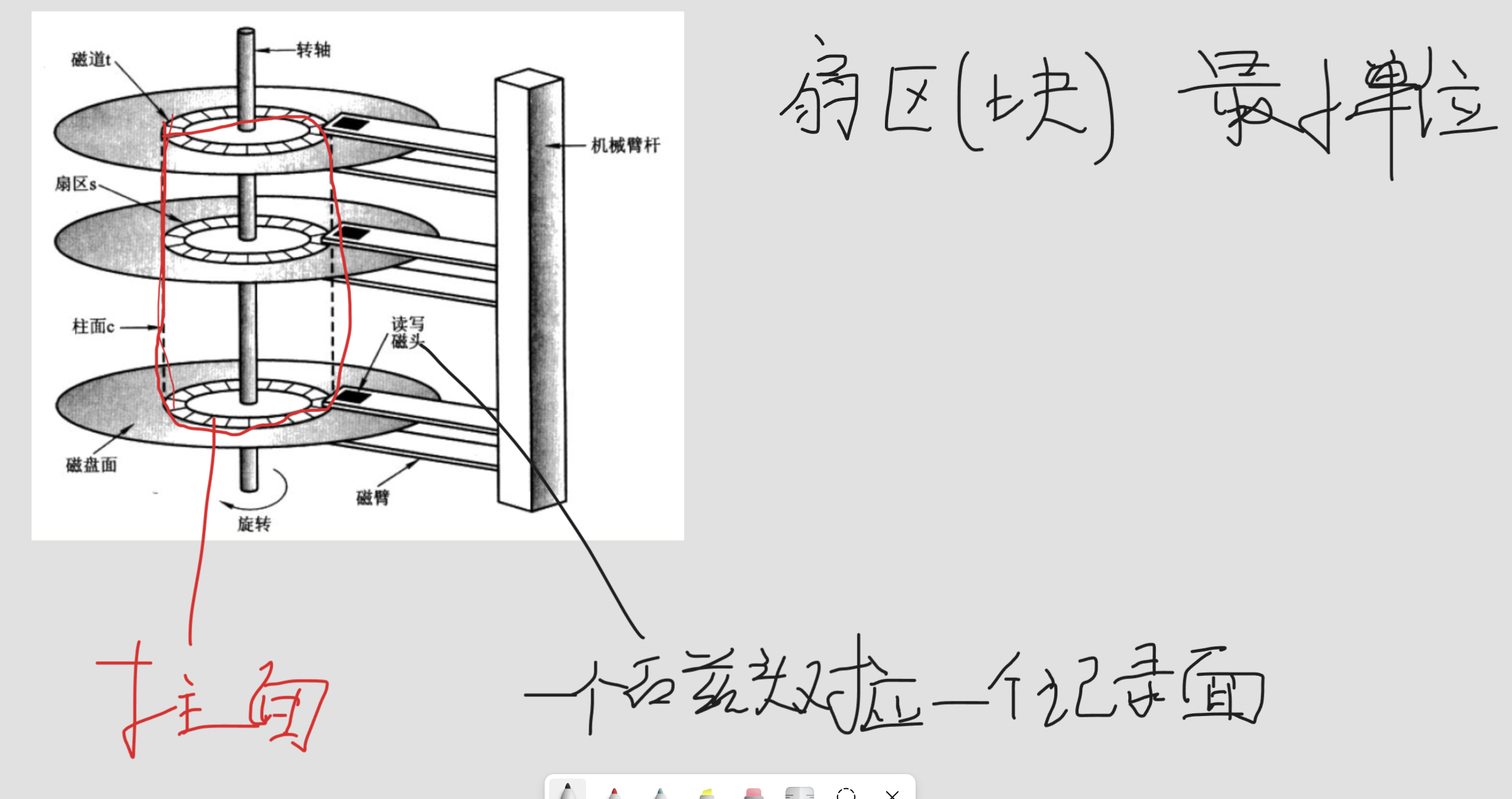

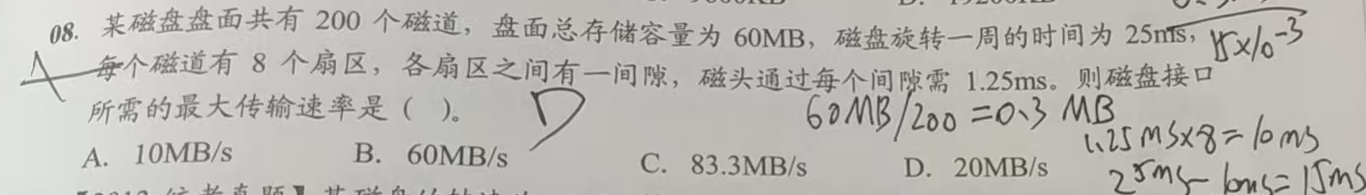

四.外存

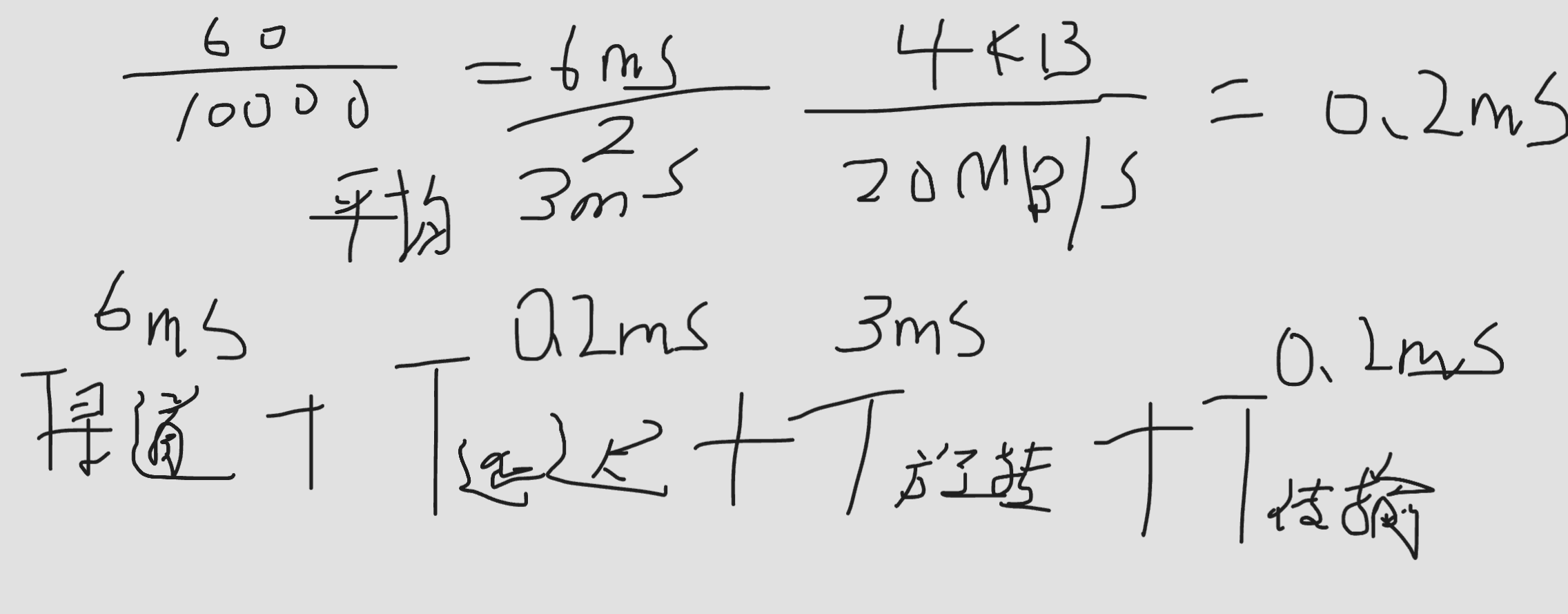

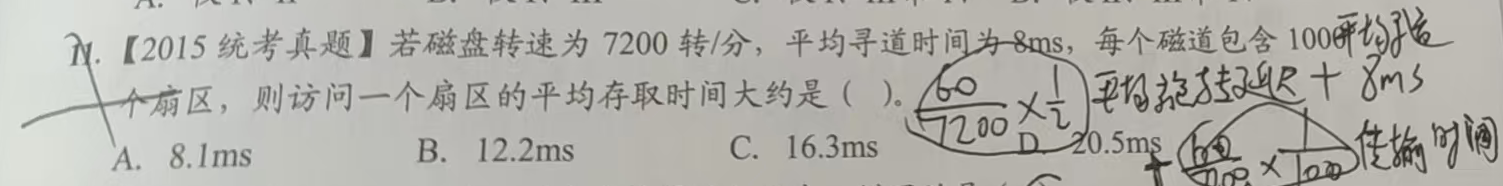

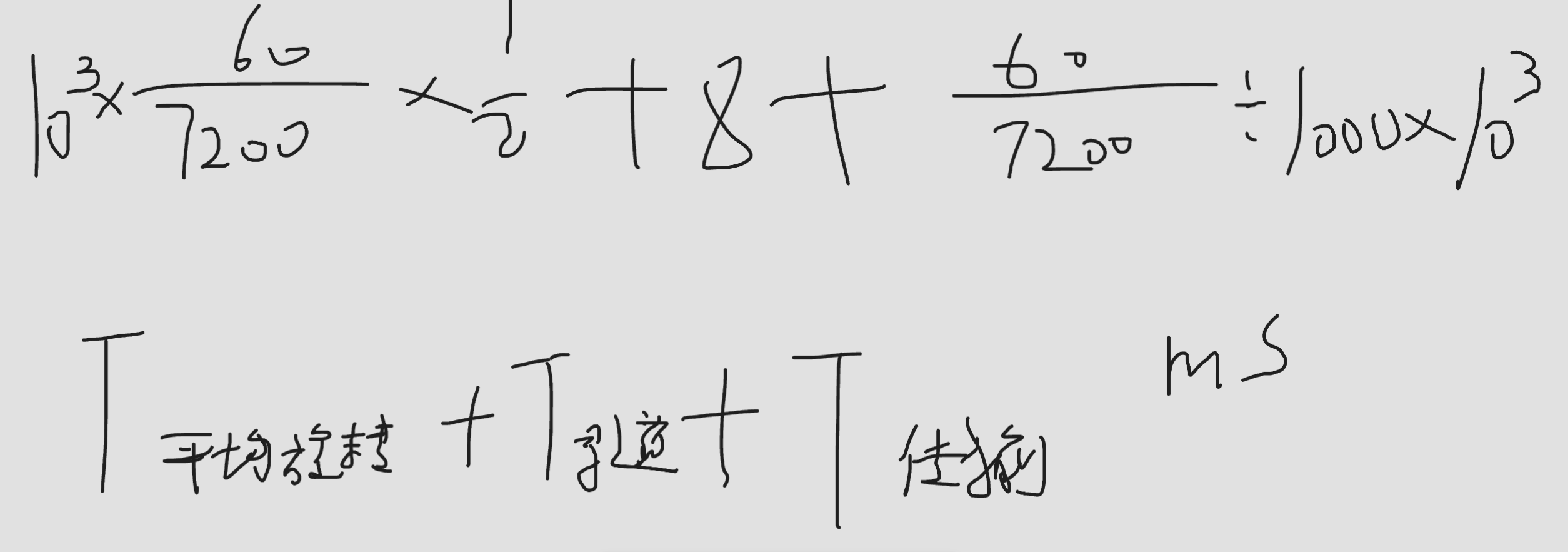

主要考察为磁盘的传输速率还有存取时间的计算

磁盘存储器

传统的机械硬盘属于磁盘存储器

特点就是价格便宜 存储容量大 缺点就是速度问题

磁盘容量:

非格式化容量(磁记录表面可利用的磁化单元总数) =记录面数x柱面数x每条磁道的磁化单元数

格式化容量(按照某种特定的记录格式所能存储信息的总量) =记录面数x柱面数x每道扇区数x每个扇区的容量

数据传输速率:

单位时间内传送数据的字节数

D=rN r:磁盘转数r转/秒 每条磁道容量N字节

存取时间:

寻道时间+旋转延迟时间+传输时间

磁盘阵列:

RAID(独立冗余磁盘阵列)将多个独立的物理磁盘组成一个独立的逻辑盘

总之其使用多个磁盘 提高了传输速率 通过镜像功能提高了安全可靠性 通过数据校验 提供容错能力

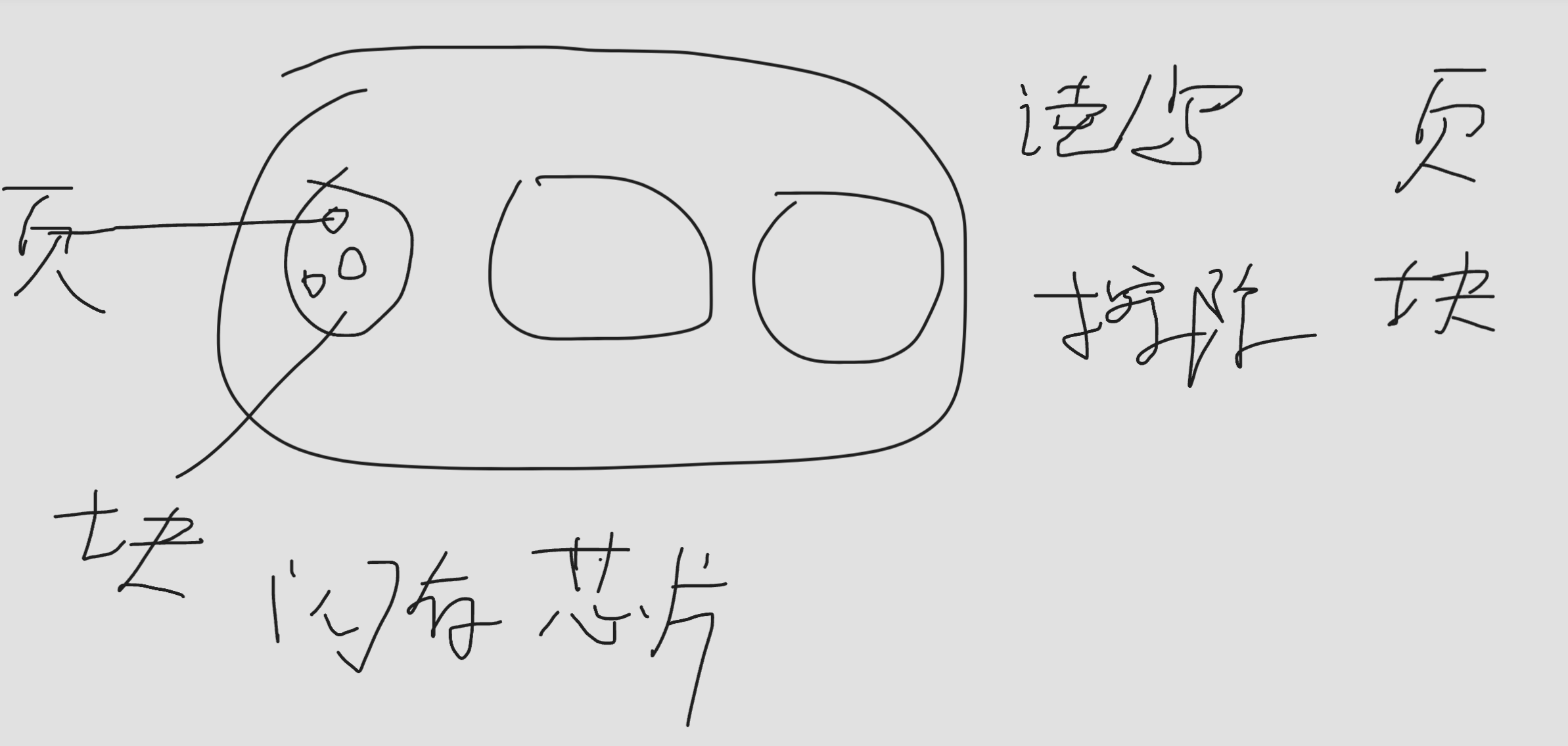

固态硬盘(SSD)

核心:基于闪存技术

如图现在大多采用SSD 最佳特点就是速度快 缺点则是价格成本高 随机写慢

看题:

若磁盘的转速提高一倍 存取速度不一定提高一倍 取决于所有步骤总共

以一条磁道为研究对象 求一条磁道容量/磁道访问所需时间

注意传输速率以十进制计算 所以上述MB=1000KB 还有就是平均旋转延迟 需要除以2

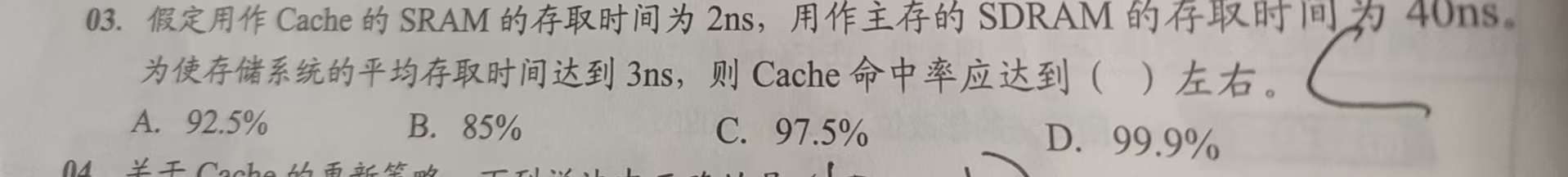

五.Cache(高速缓冲存储器)

我理解的一句话:就是介于主存和cpu之间的一个东西 然后把常用的放在cache中 cpu直接调用cache 而不再去主存调用 提高速率

原理:程序访问的局部性 时间局部性和空间局部性

时间局部性:一个内存位置被重复引用

空间局部性:一个内存位置被引用 附件的位置很快也被引用

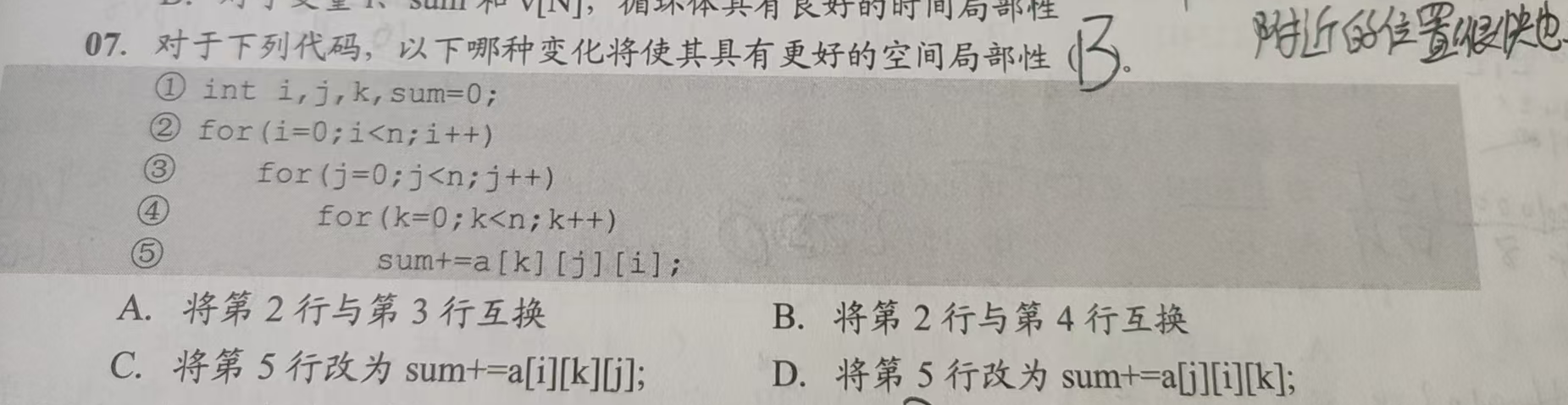

如:

比如i j k被重复引用所以具有时间局部性

而为了有更好的空间局部性 则代码中数组sum应该这样

有点脑子应该能看懂

CPU与Cache之间数据交换以字为单位

Cache与主存之间的数据交换以Cache块为单位

N1:cache总命中次数

N2:访问主存总次数

t1:命中cache访问时间

t2:缺失访问时间 (t1+访问主存时间)

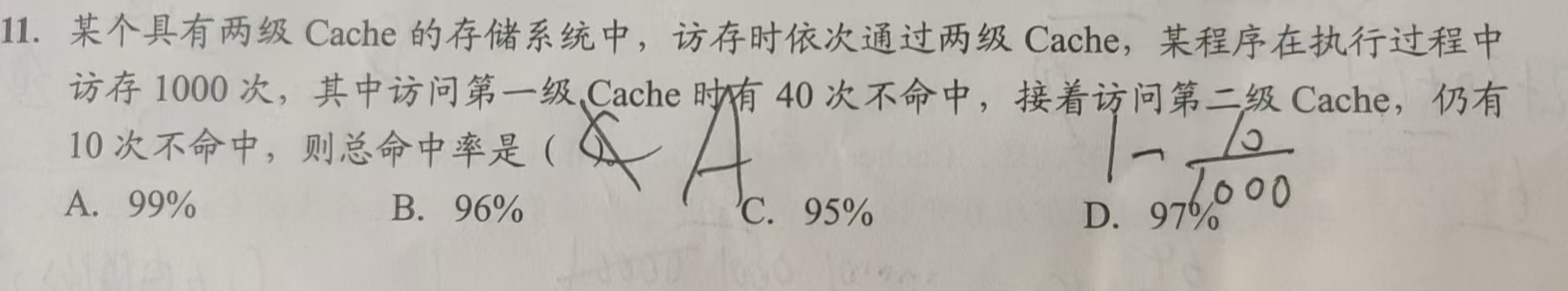

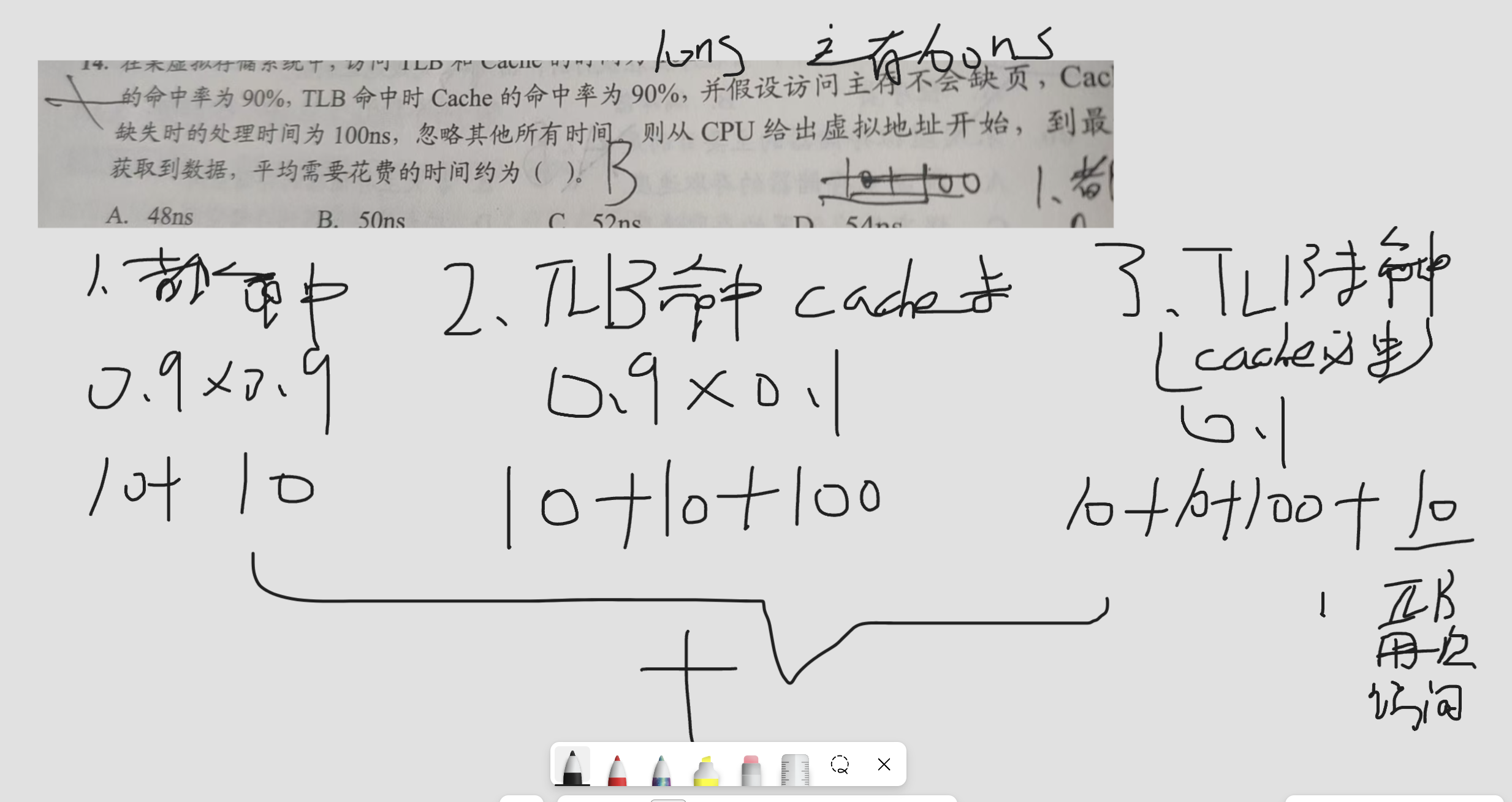

命中率:H=N1/(N1+N2)

平均访问时间:T=Ht1+(1-H)t2

利用上述公式求解H

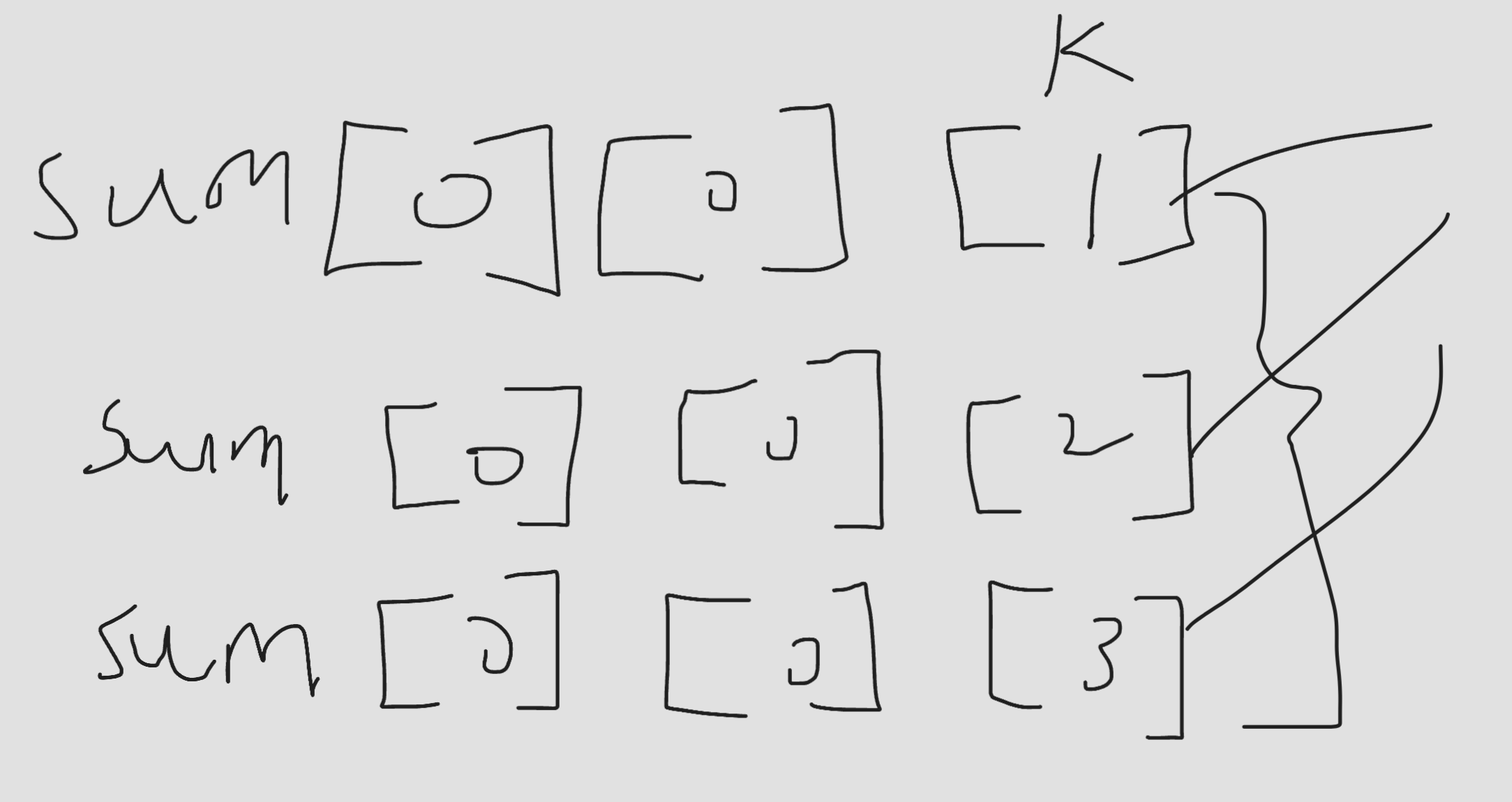

解决上述问题需要了解 cache之所以强大 使用为有大量堆积缓存

容量越大 则速度越快 这就是amd的x3d芯片打网游厉害的原因 当然cache容量决定价格高

以第二级为即 1-10/1000

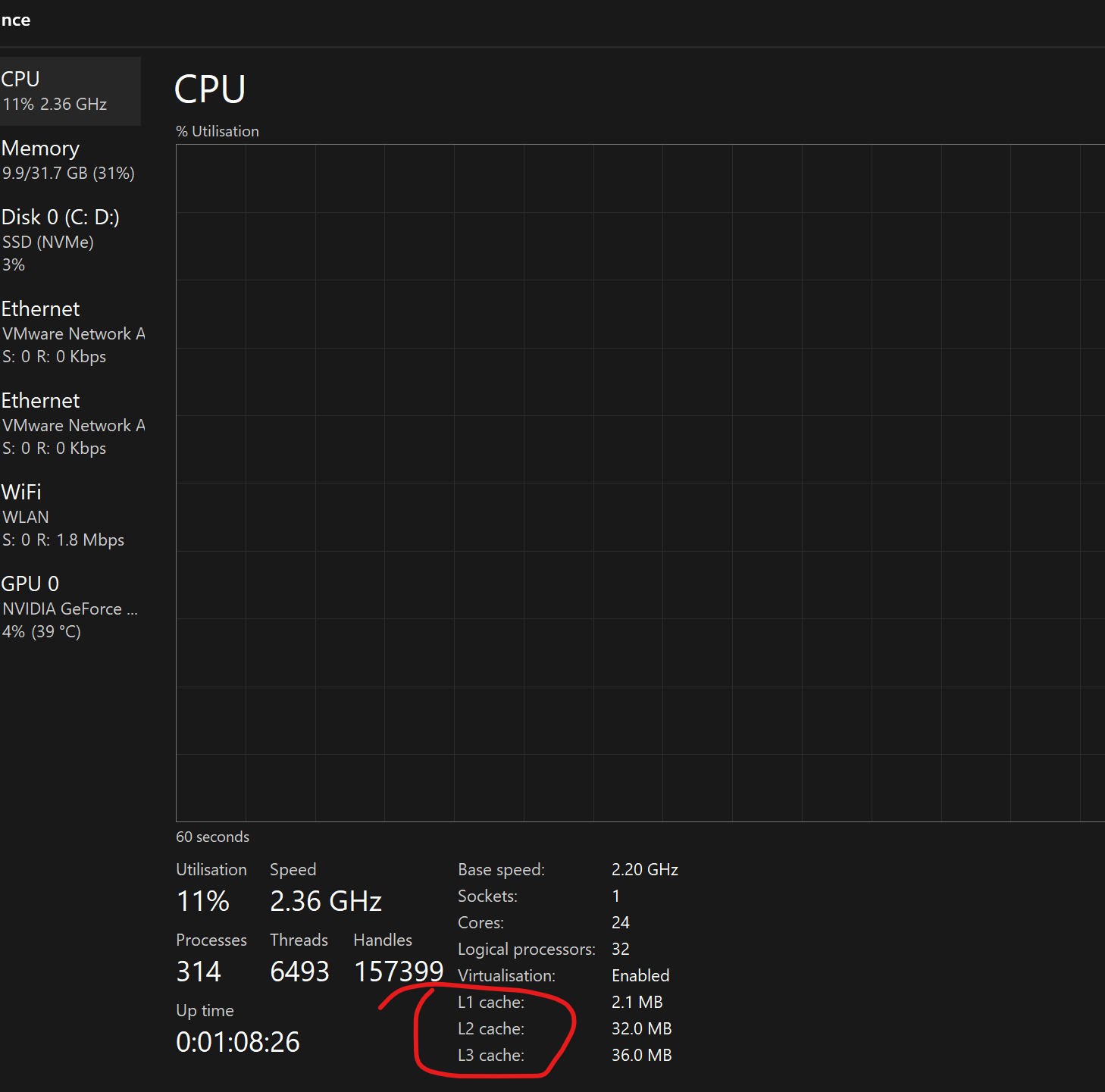

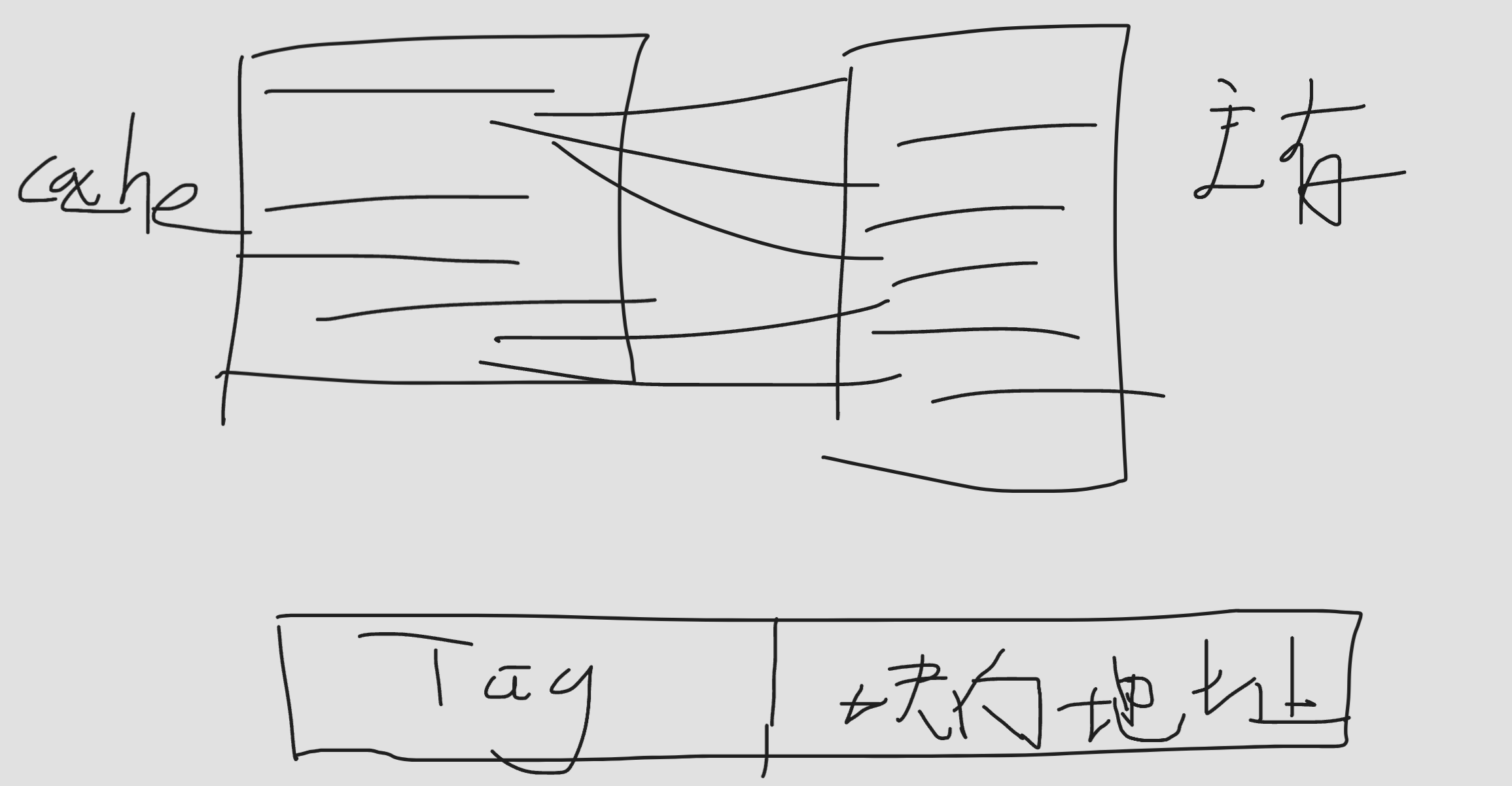

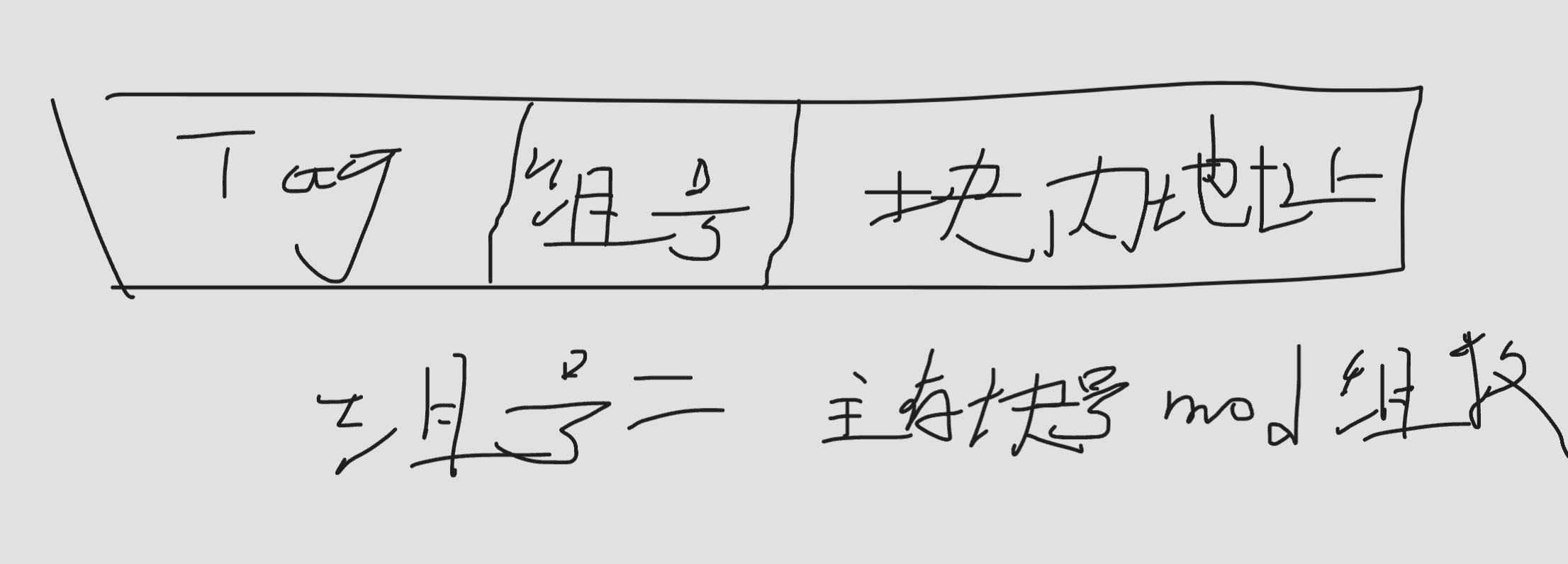

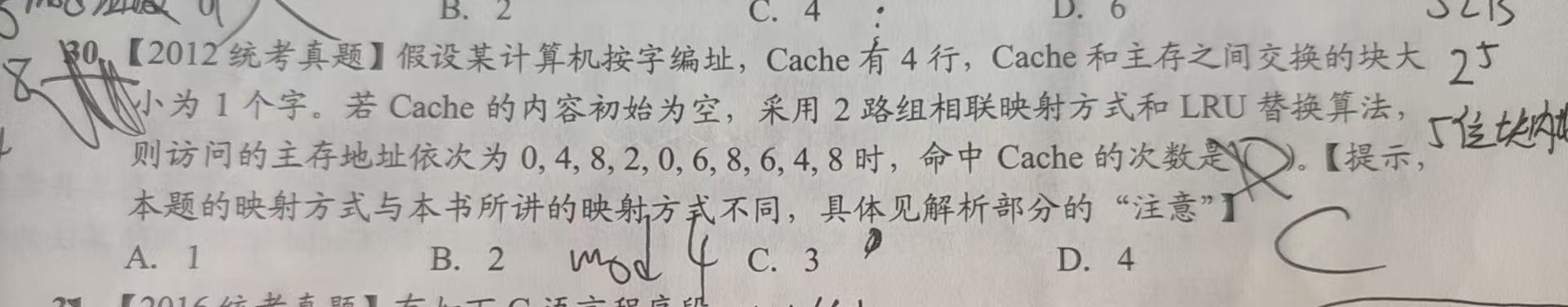

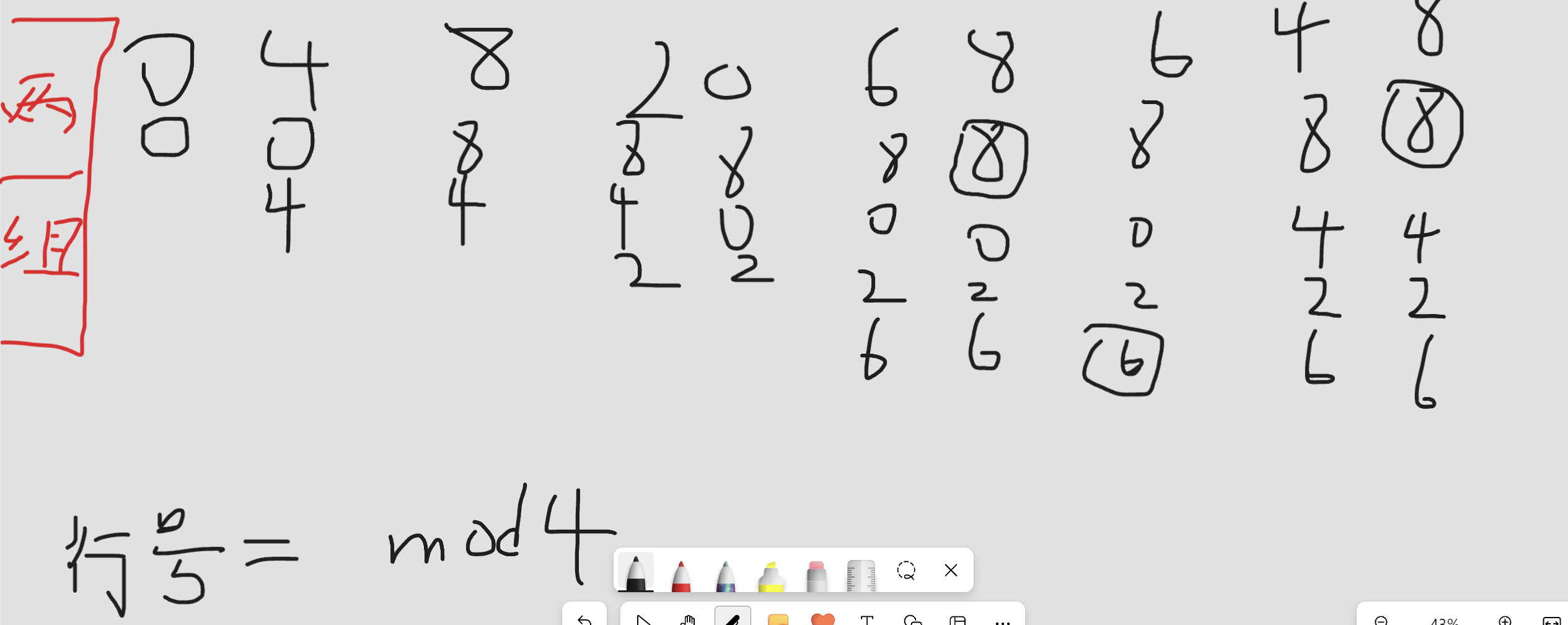

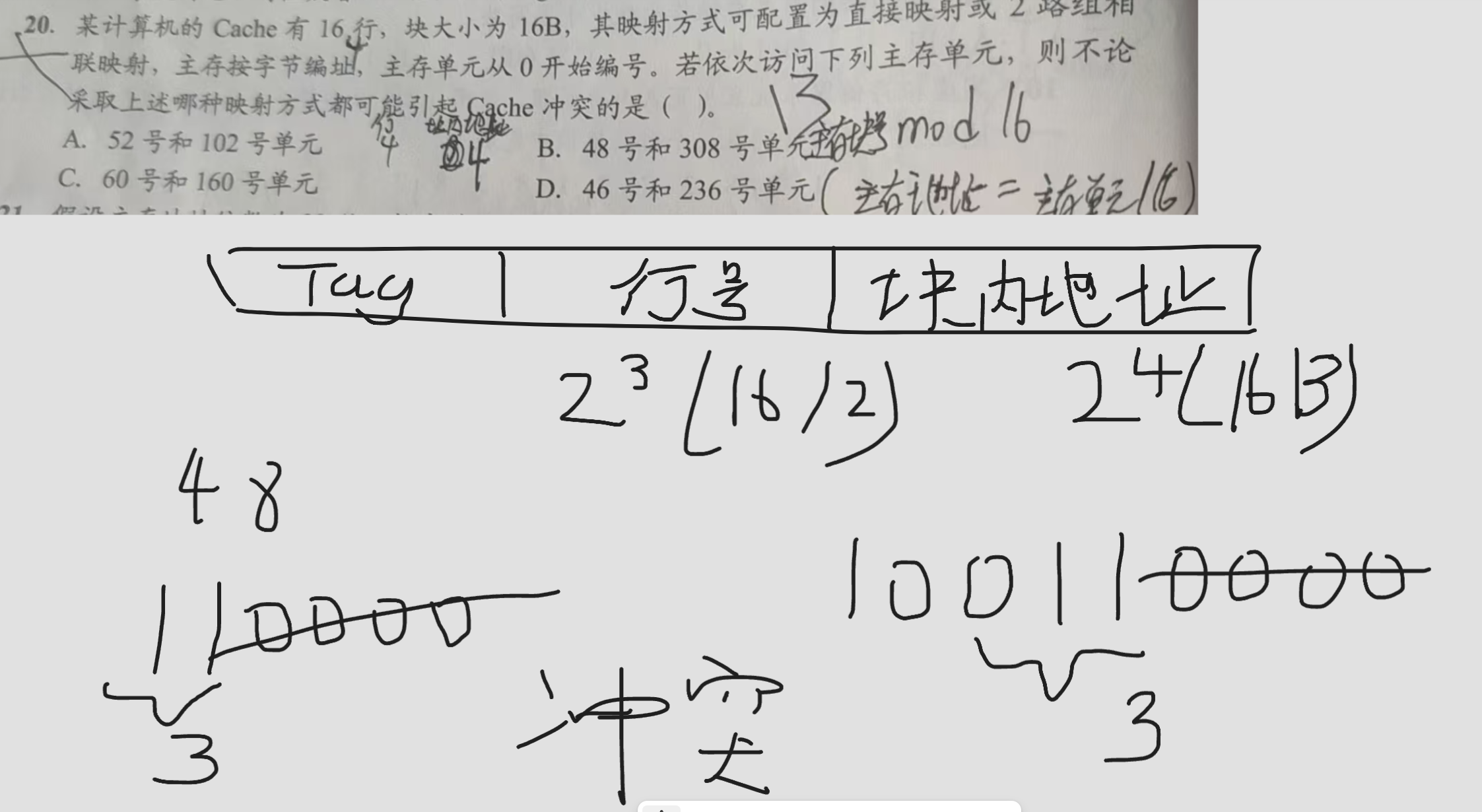

cache和主存的映射方式

灰常重要!!!

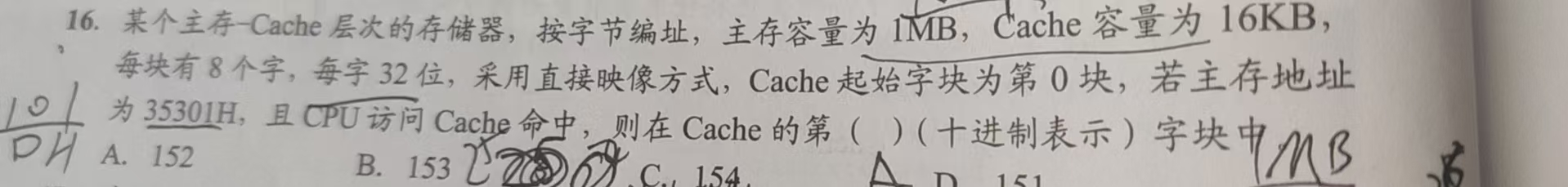

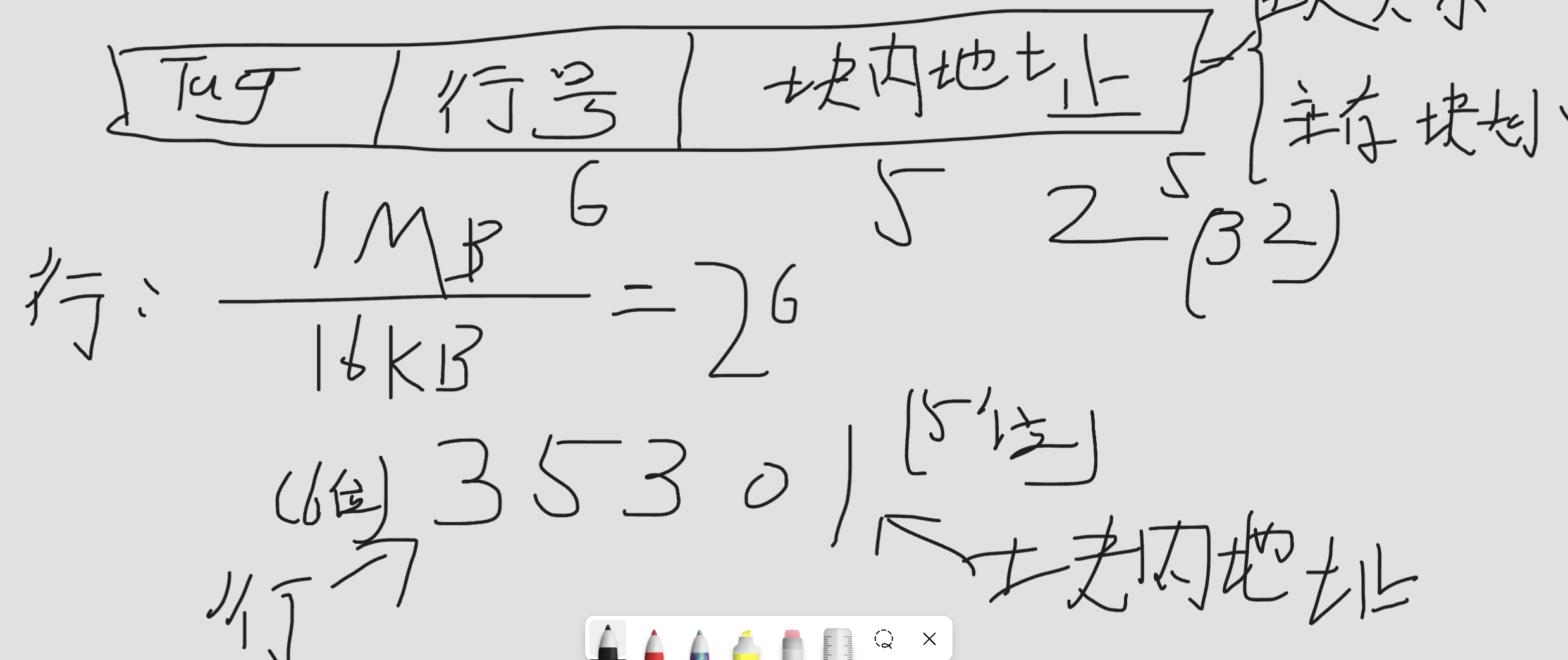

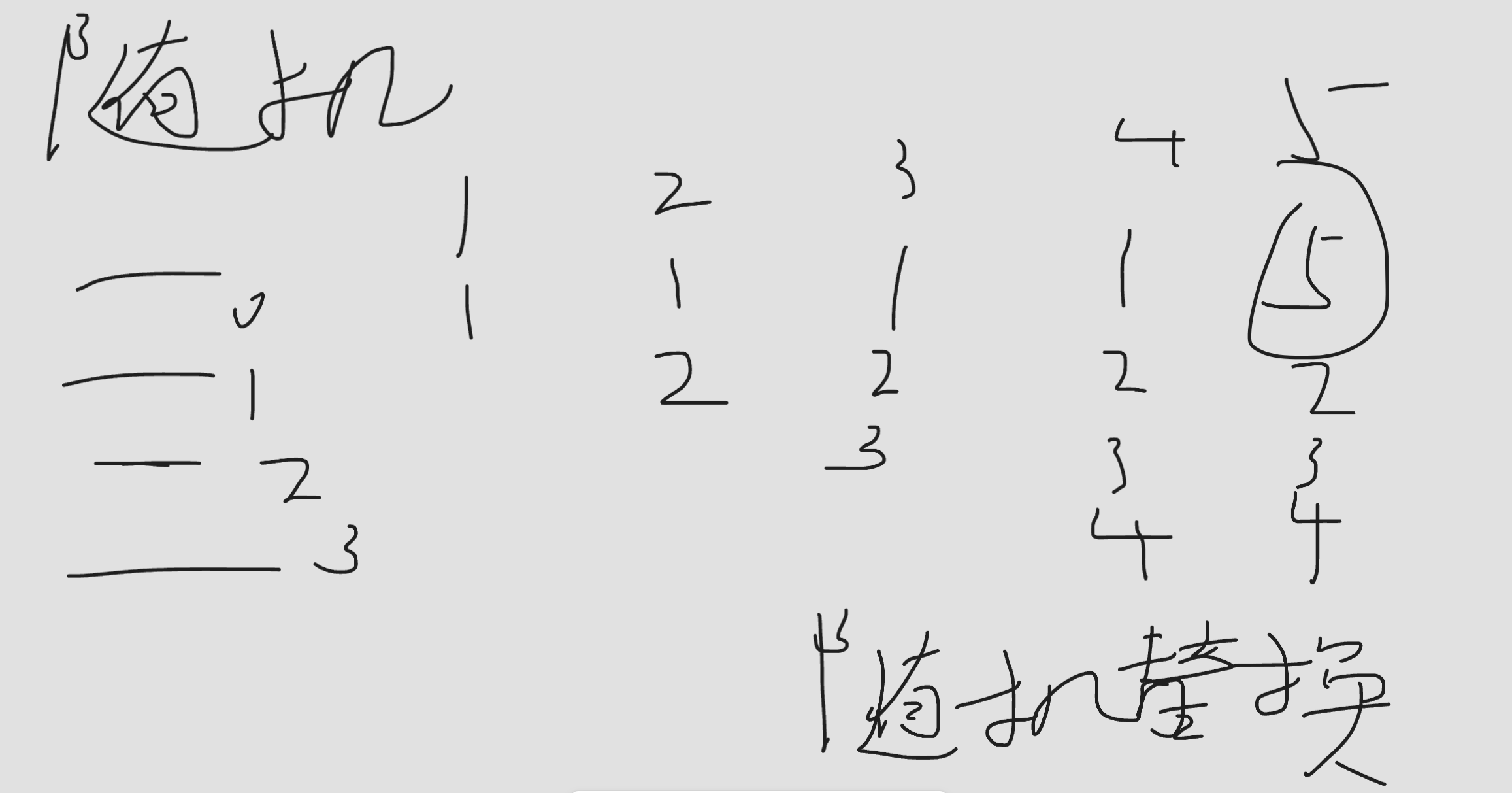

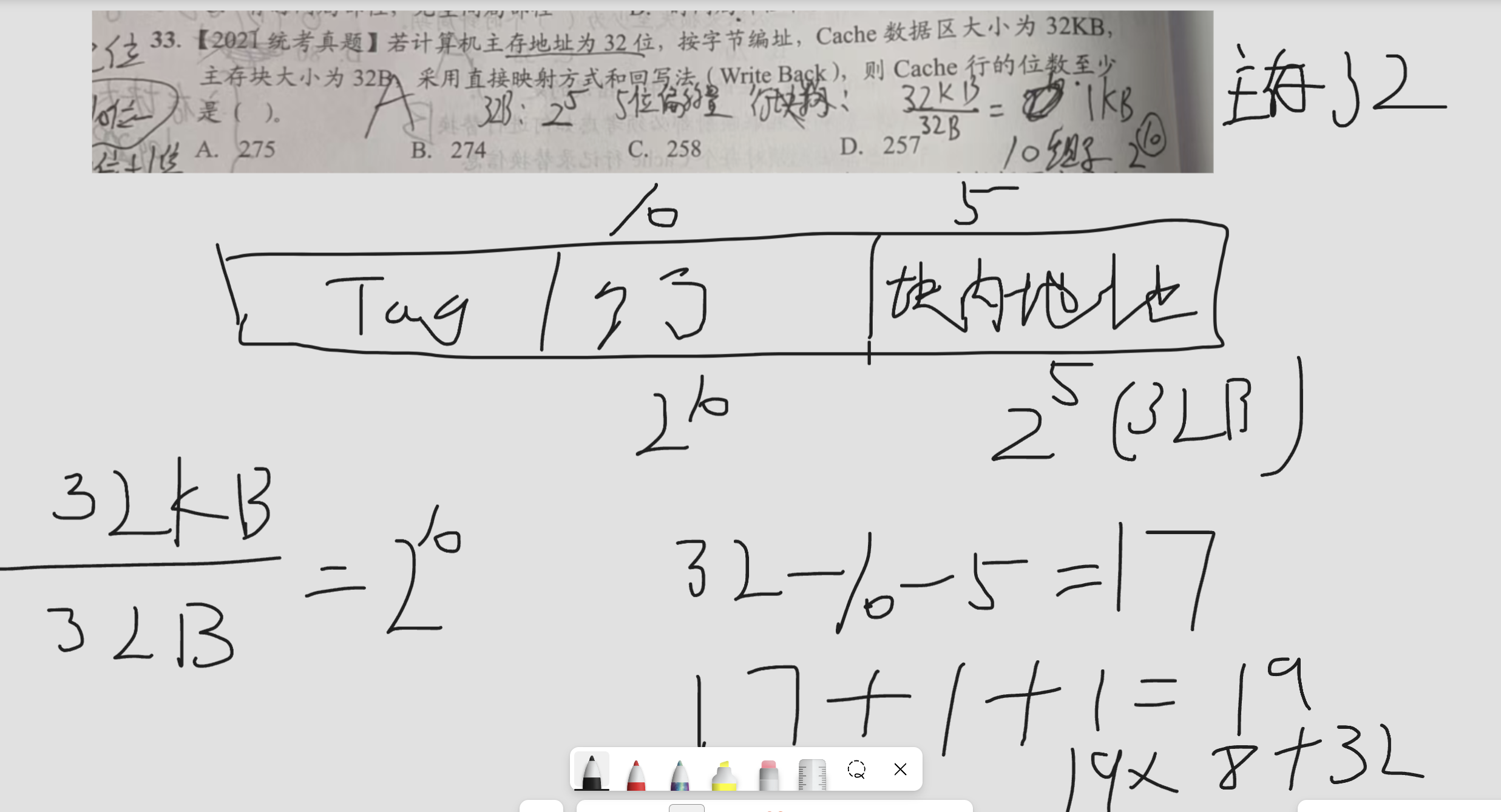

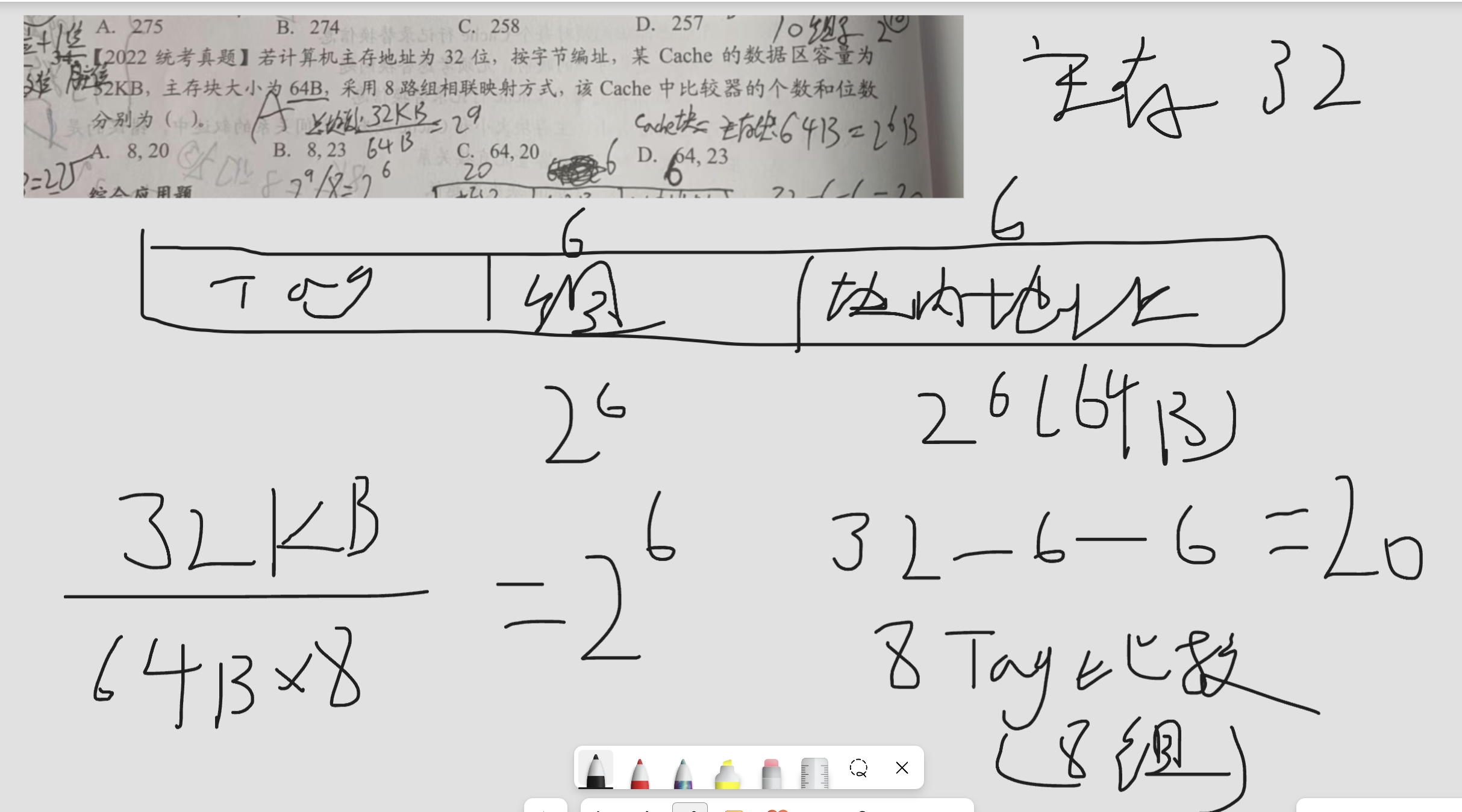

1.直接映射

主存每一块装入Cache唯一位置 若比如两个映射同一个位置 则产生块冲突 第一个块被替换出去 无须使用替换算法

35301H转换成二进制后 行号从前面去除6位 块内地址后面去除5位 剩下转换成十进制得到Tag

2.全相联映射

采用替换算法

每一块可以转入cache的任何位置

不常用 缺点是时间开销和硬件开销大 不适合大容量Cache

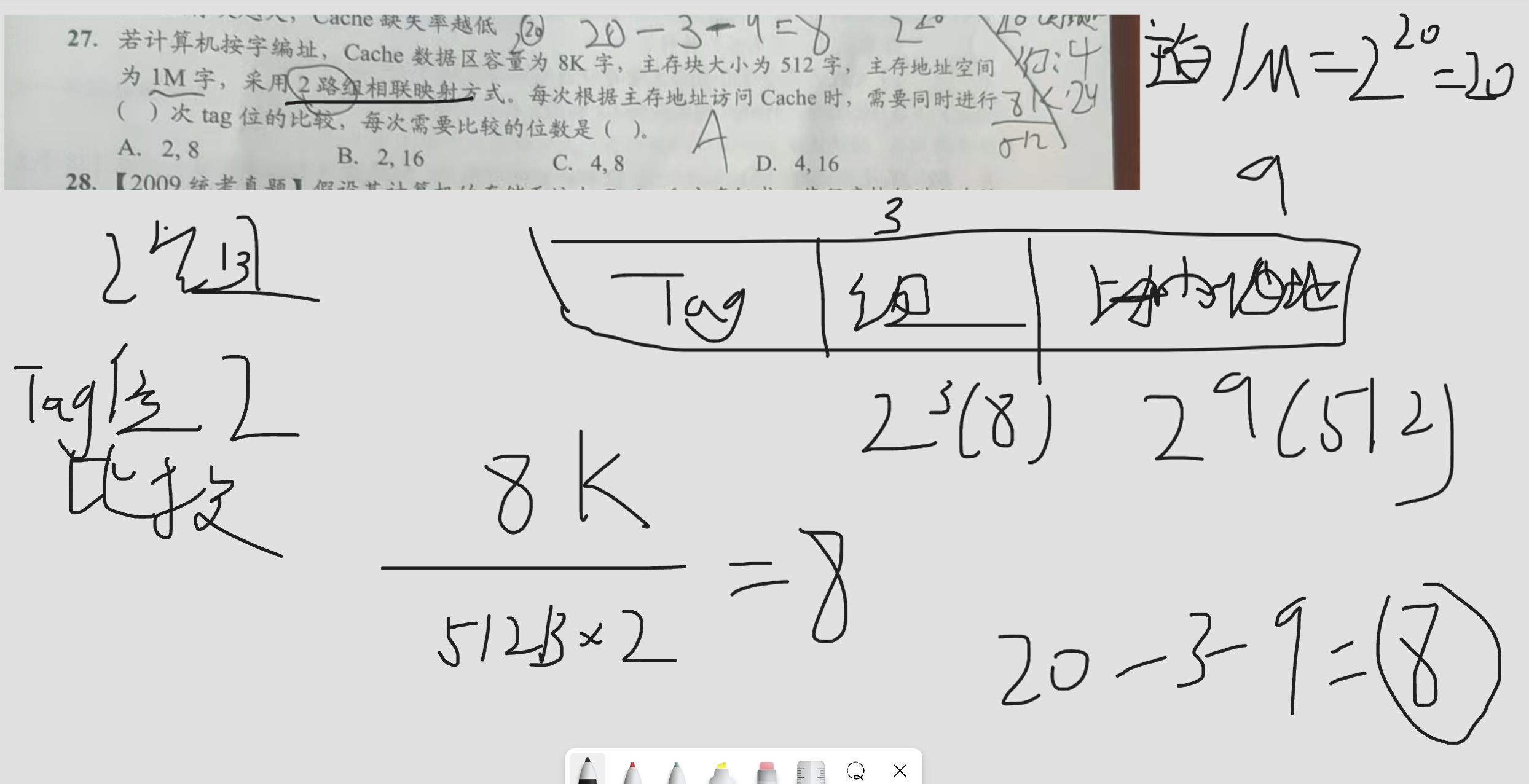

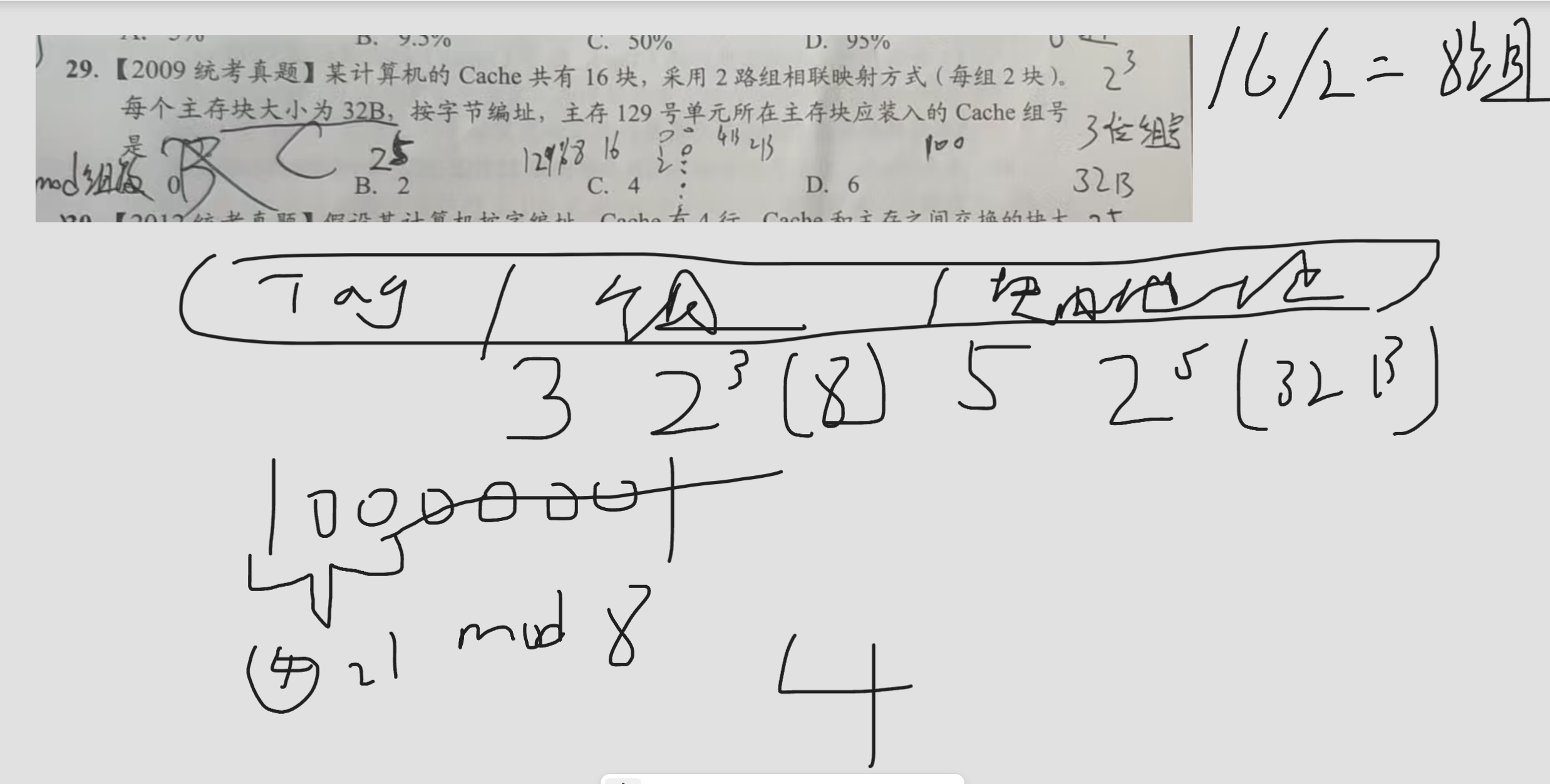

3.组相联映射

是直接映射和全相联映射的折中方案

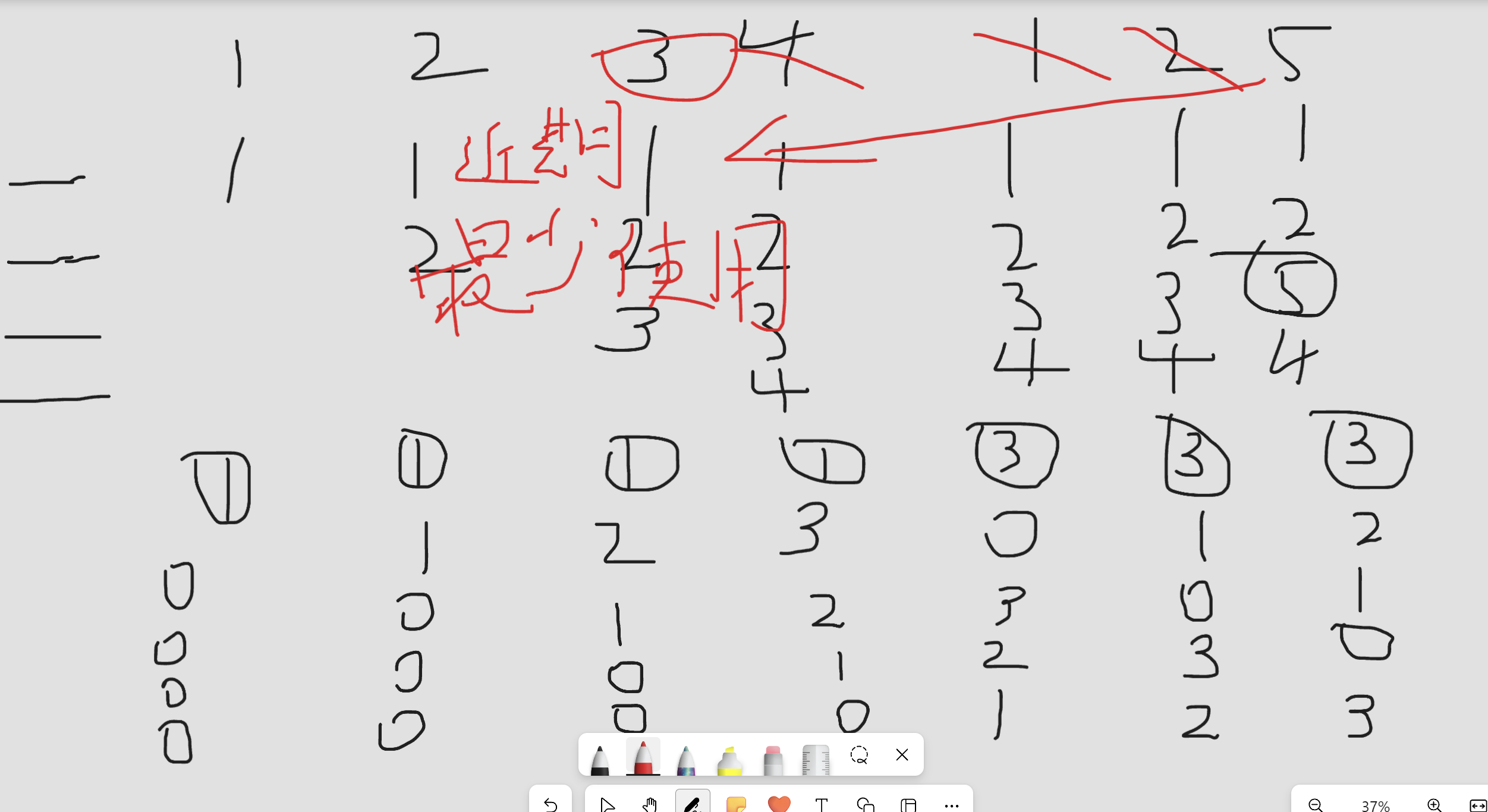

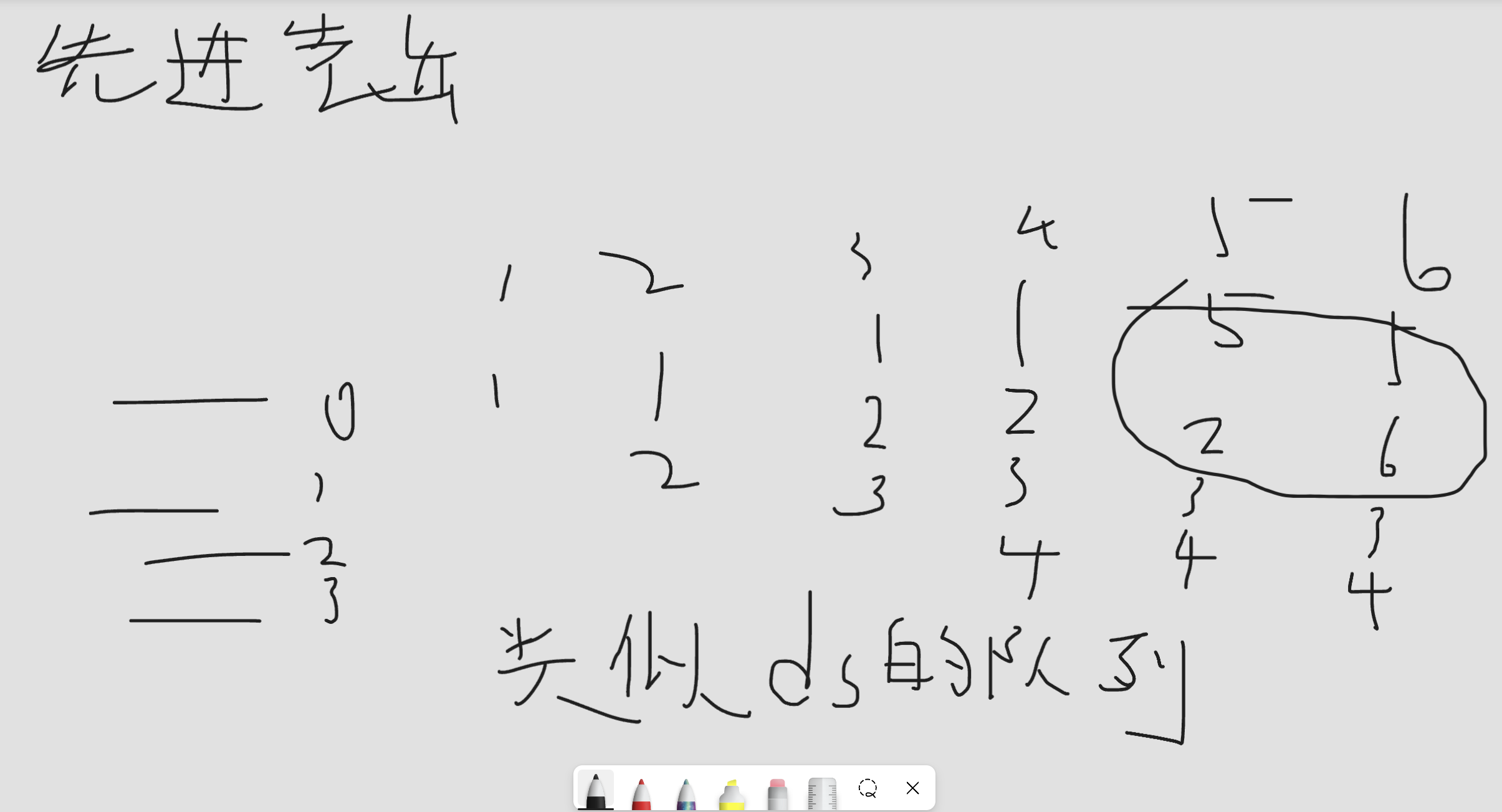

Cache主存块的替换算法

- 随机算法

- 先进先出算法

- LRU(近期最少使用算法)

前两种简单 一笔带过 比如 主存访问序列{1,2,3,4,5} 四个cache块

重点看LRU算法

它设置了一个计数器 用来记录使用情况

变化规则:

1.命中时 行计数器清零 其他低的计数器+1

2.未命中且有空闲行时 新装入行计数器置0 其余非空闲行+1

3.未命中且无空闲行 计数值3行被替换 新装入计数器置0 其余+1

例如:主存访问序列{1,2,3,4,1,2,5} 四个cache块

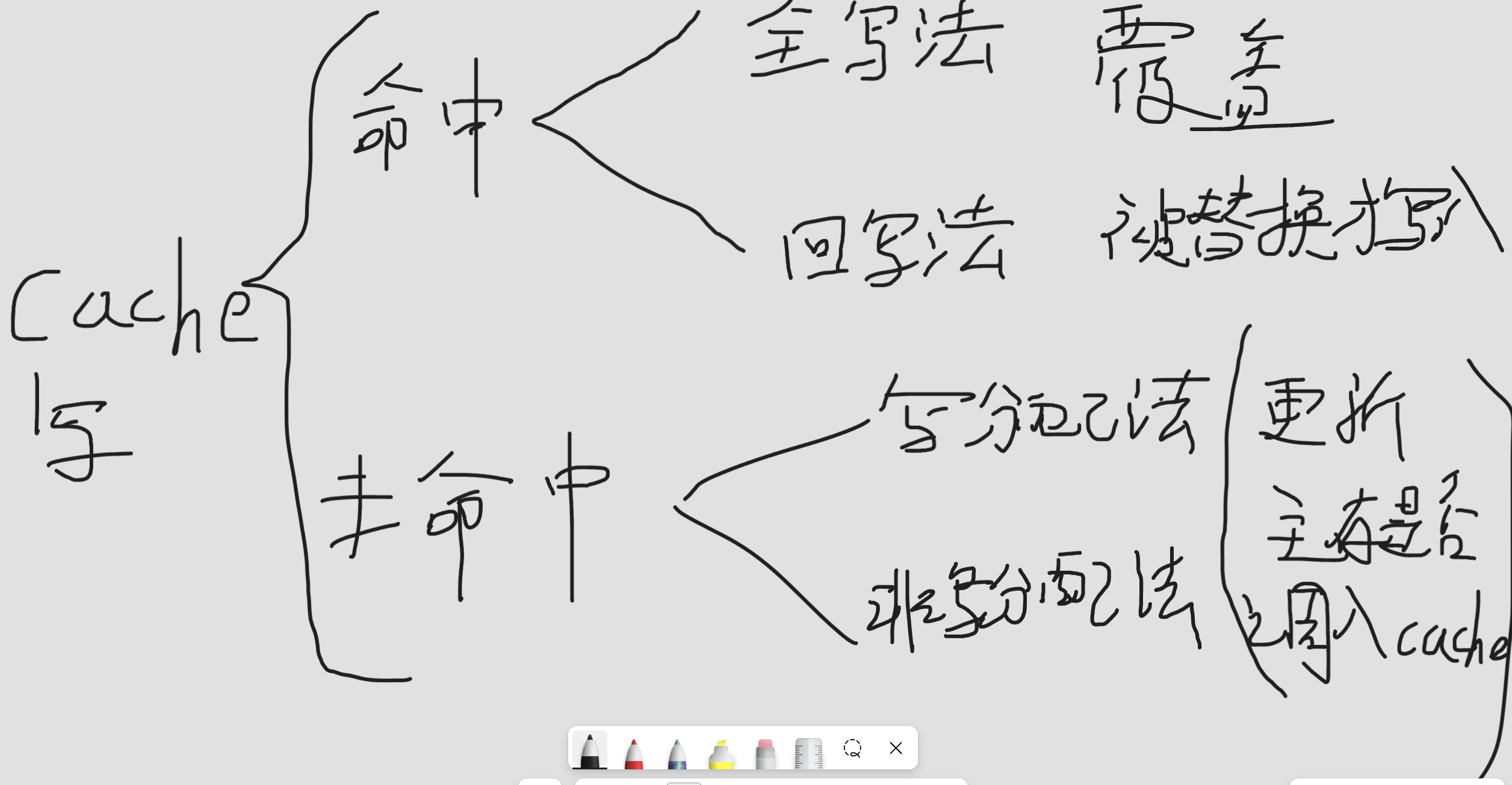

Cache一致性问题

cache内容修改 主存中保持一致

一张图搞定

题目:

一般+1+1+1

一个有效位必须有

一个替换位 若采用回写法不需要

一个脏位(修改位) 采用回写法使用

六.虚拟存储器

主存和辅存共同构成了虚拟存储器

对于应用程序员 虚拟存储器透明

对于所有程序员 主存-cache透明

地址空间统一编址

原理:局部性原理(在程序执行过程中 程序对主存访问是不均匀的)

处理一致性问题 采用回写法

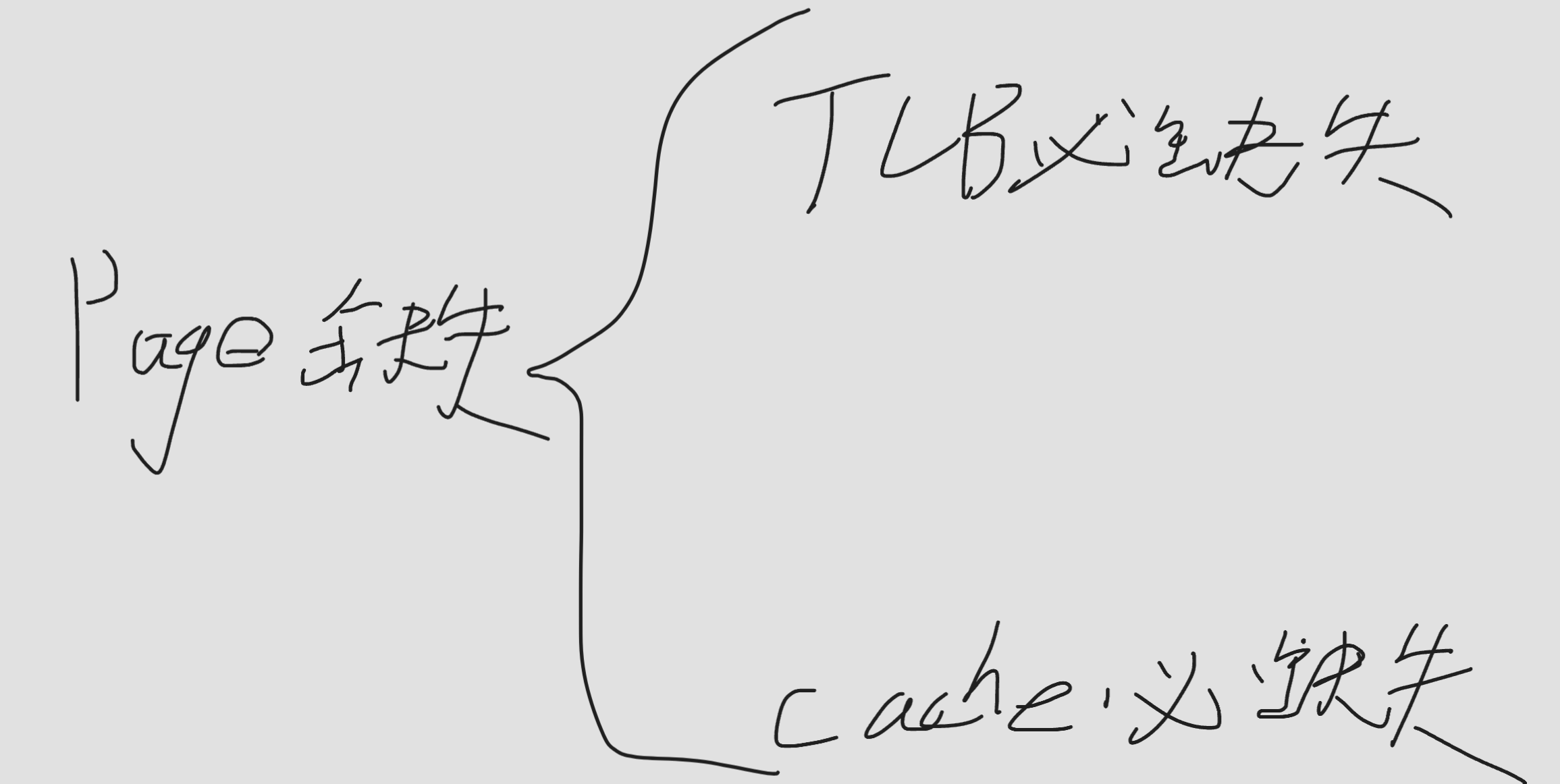

重点两个东西

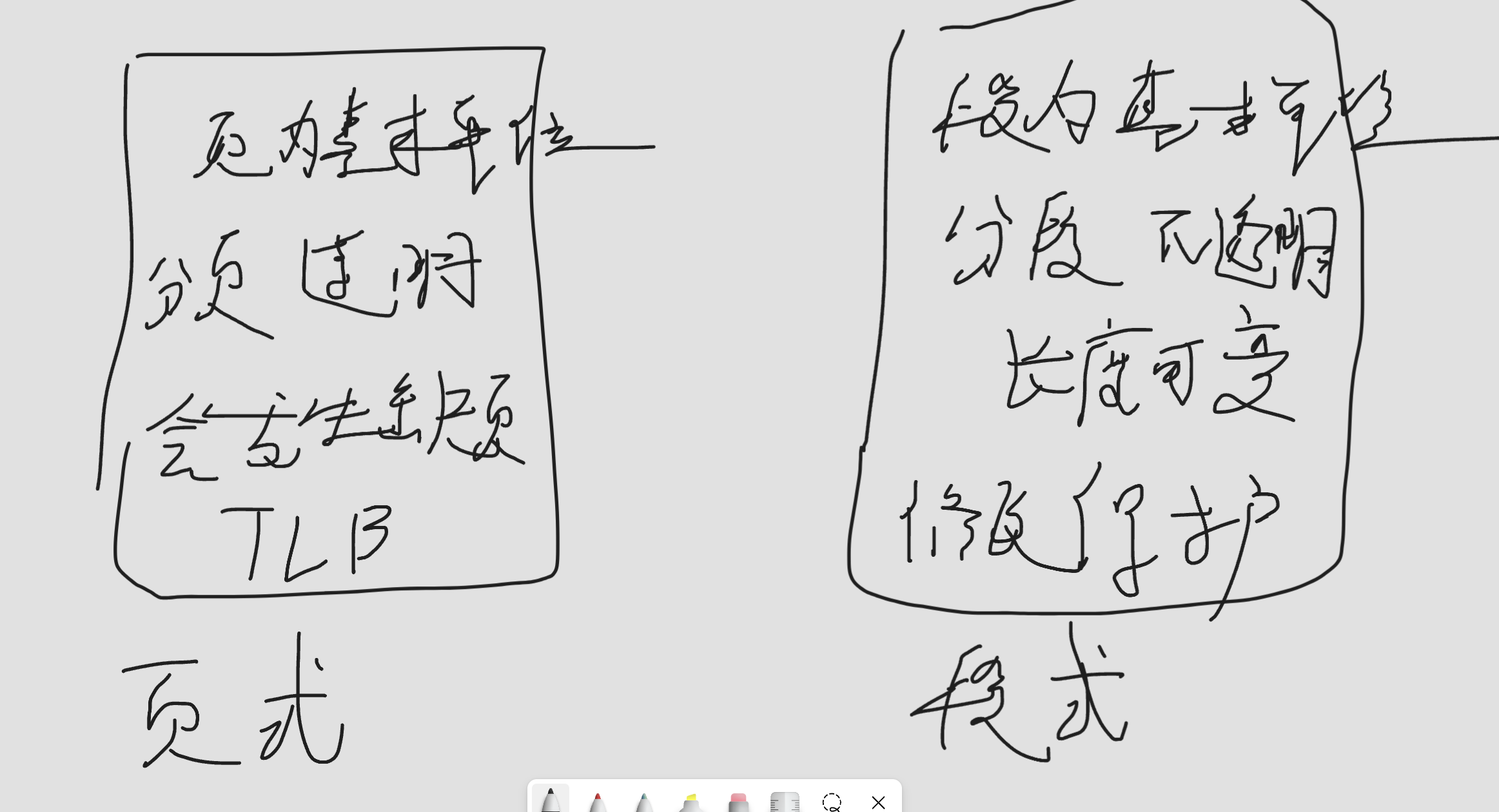

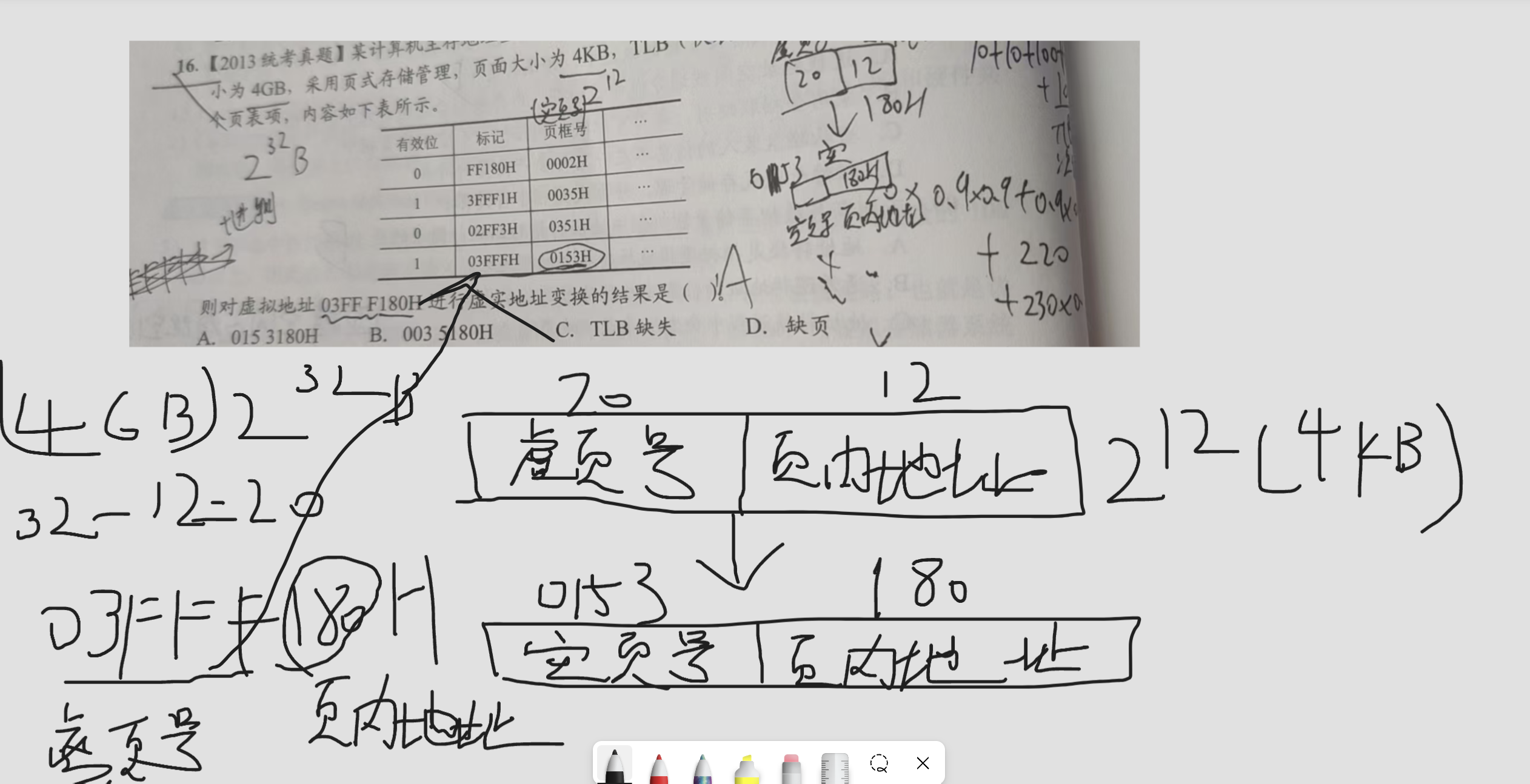

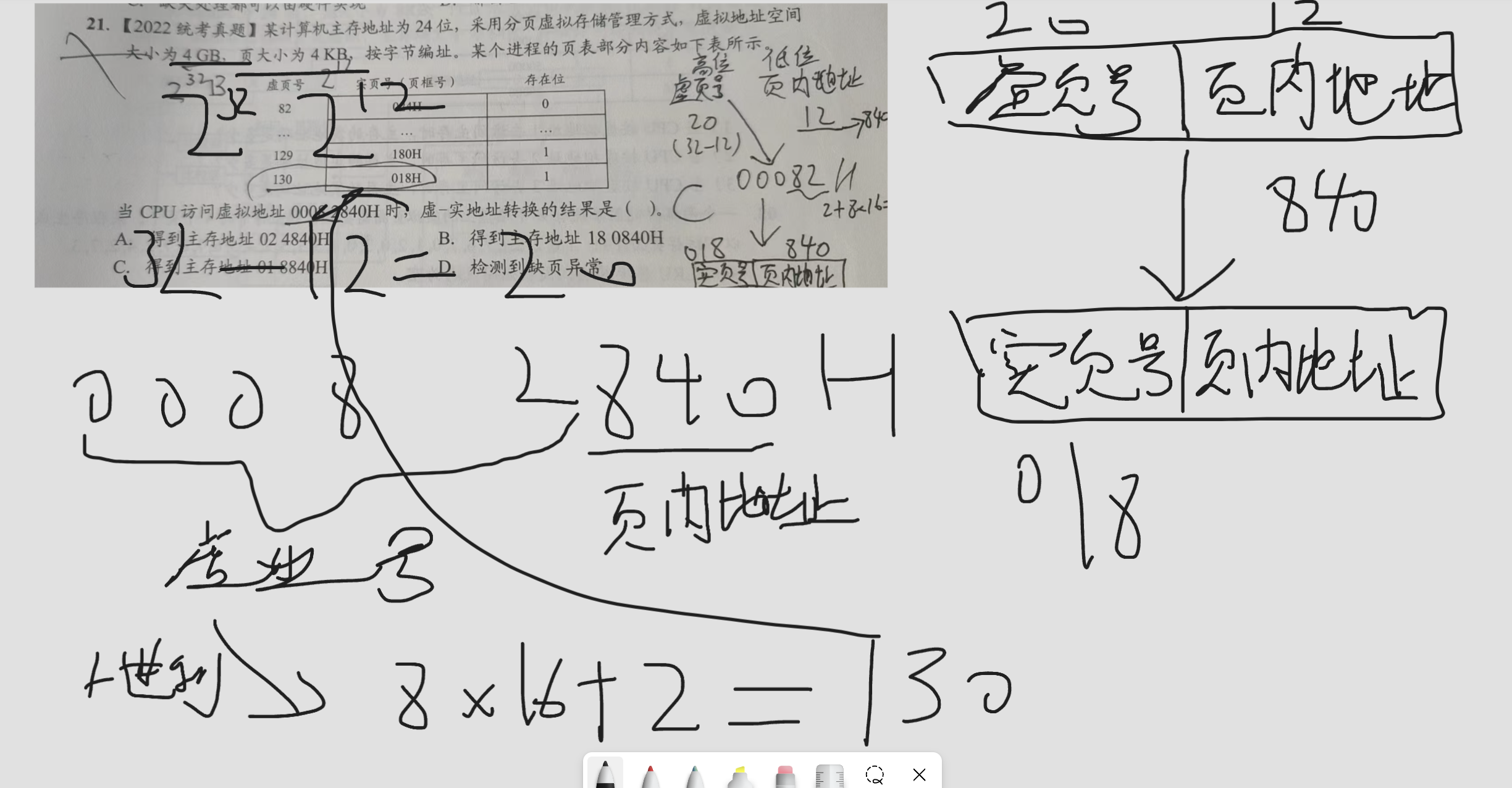

- 页式虚拟存储器

- 段式虚拟存储器

考察主要页式虚拟存储器

缺页:操作系统缺页异常处理程序解决

地址转换:由操作系统完成

逻辑空间(虚拟)>物理空间(实际)

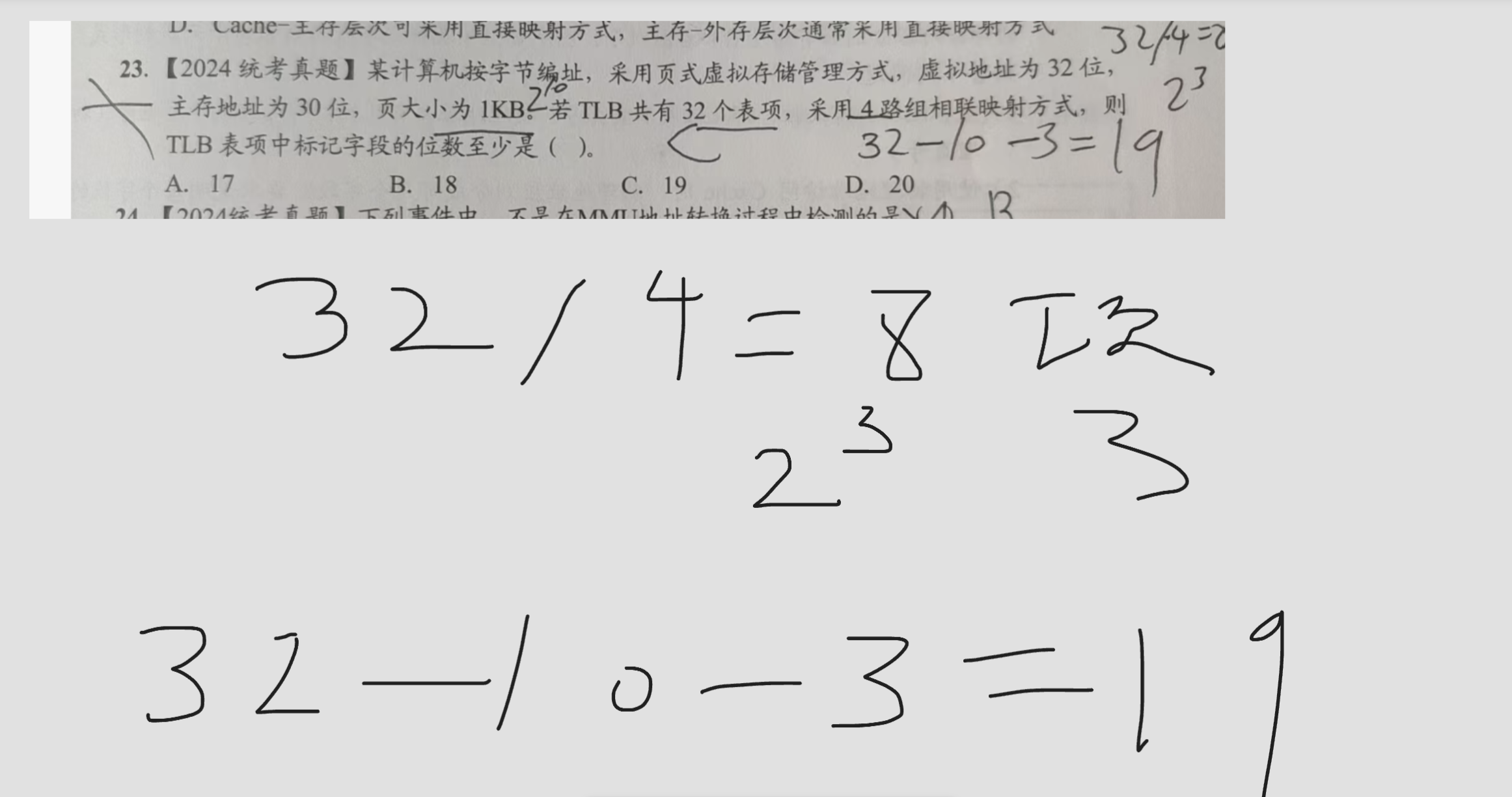

TLB(快表)

用SRAM实现 工作原理类似cache

至于段页式虚拟存储器 仍然以页为基本单位 综合两种折中

看题:

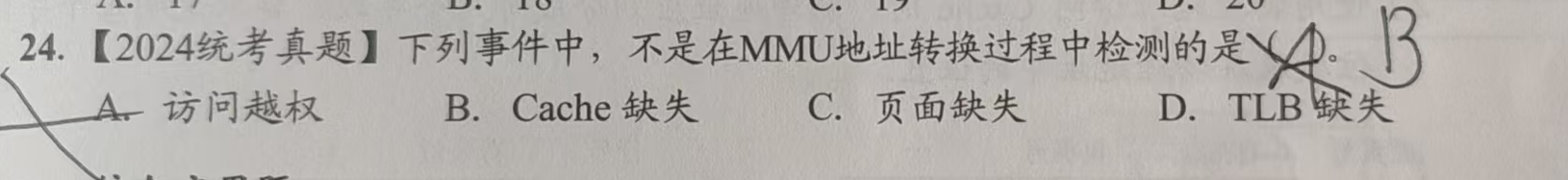

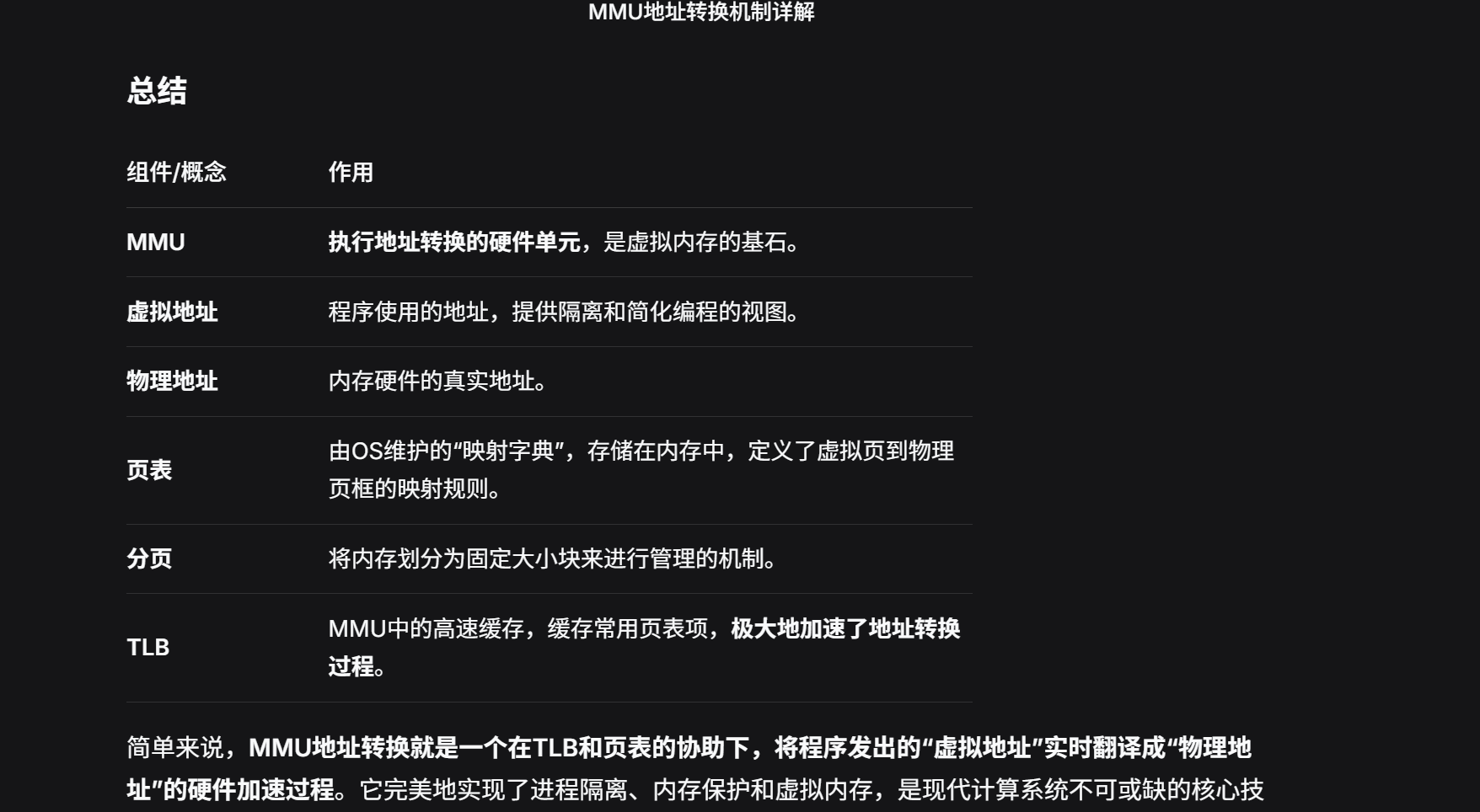

关于MMU参考deepseek

第三章到此结束!

浙公网安备 33010602011771号

浙公网安备 33010602011771号