计算机体系结构-hw9

计算机体系结构-hw9

前言

张科老师的计算机体系结构课后作业,不保证正确,请辩证看待。

Problem 1:

如果存在L3 Cache,AMAT为:

AMAT = 0.98*1 + 0.02(0.99 * 10 + 0.01*(0.995 * 30 + 0.005 * 300)) = 1.18427

another answer: 1000 + 20*10 + 10*30 + 5*300 = 3000

如果不存在L3 Cache,AMAT为:

AMAT = 0.98*1 + 0.02*(0.99*10 + 0.01 * 300)= 1.238

another answer: 1000 + 20*10 + 10*300 = 4200

可以发现:使用L3Cache的(平均)内存访问时间比不使用L3Cache的(平均)内存访问时间更短

所以:需要L3 Cache

Problem 2:

A-组0 B-组1 C-组0 D-组1 E-组0 F-组1 G-组0 这里假设采用LRU置换,估算命中和失效次数:

失效次数:1+1+1+1+...+1 = 11次

命中次数:1+1+1+1+1 = 5次

Problem 3:

由于一个Cacheline大小为64B,8KB的全相联数据缓存阵列,共有Cacheline个数为:

8192B / 64B = 128(个)

- 由于采用全相联映射,因此组个数为1,128路.

- CacheLine大小为64B,按照字节寻址,可以表示64个地址,共用6bits. 因此offset bits为6bits.

- 全相联映射,index bits 为 0.

- 由于地址位为40位。tag bits = 40 - 0 - 6 = 34bits

- 标记数组大小 = 组个数*路个数*tag大小 = 128 * 34 = 4352bits = 544B.

Problem 4:

如果要避免VIPT出现的别名问题,我们应该保证:

page offset >= block index + block offset

明白了上述的内容之后,我们来做一下这道题:

直接映射L1缓存:

- 页面大小16KB,地址以字节寻址,那么一个页面可以表示16K地址。16K = 16 * 1024 = 2^4 * 2^10 = 2^14个地址。共需要14bits.

- 由于缓存块大小32B,可以表示32个地址,2^5个地址。共需要5bits.

- 即 14 >= block index + 5 => 要满足最大,block index 为9bits。

- 9bits共有512路,一路有32B的块。因此:最大映射L1Cache = 512 * 32B = 16KB。

最大二路L1缓存:

- 页面大小16KB,地址以字节寻址,那么一个页面可以表示16K地址。16K = 16 * 1024 = 2^4 * 2^10 = 2^14个地址。共需要14bits.

- 由于缓存块大小32B,可以表示32个地址,2^5个地址。共需要5bits.

- 即 14 >= block index + 5 => 要满足最大,block index 为9bits。

- 9bits共有512个组,一个组有两个块.因此最大二路L1Cache = 512*2*32B = 32KB。

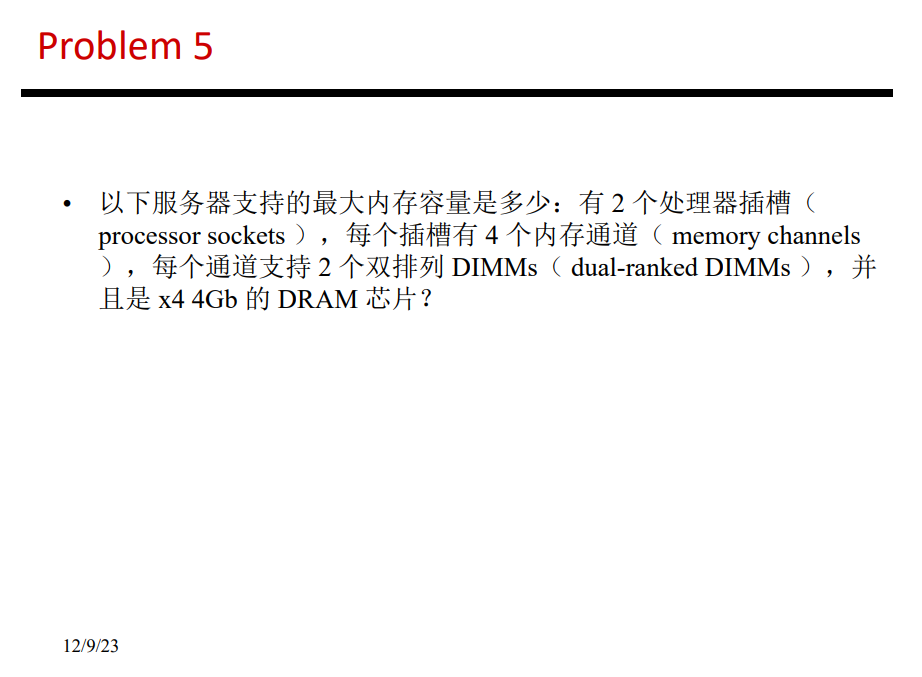

Problem 5:

先给出DRAM的组织结构:

Channel(通道) > DIMM(模组) > Rank(内存组) > Chip(内存芯片) > Bank(内存库) > Row/Column(矩阵行列)

- 共有DIMMs个数 = 2*4*2 = 16DIMMs

- 一个DIMMs有两个2Ranks,因此共有32Ranks

- 一个Rank共有16个chips,因此共有32*16 = 512chips(这里总线的位数是64位,x4代表chip带宽为4位,为了保证最大内存容量,需要16个chips)

- 一个chip4Gb,因此共有512*4Gb = 2048Gb

- 512Gb = 2048 / 8 = 256GB

- 因此服务器支持的最大内存容量为:256GB

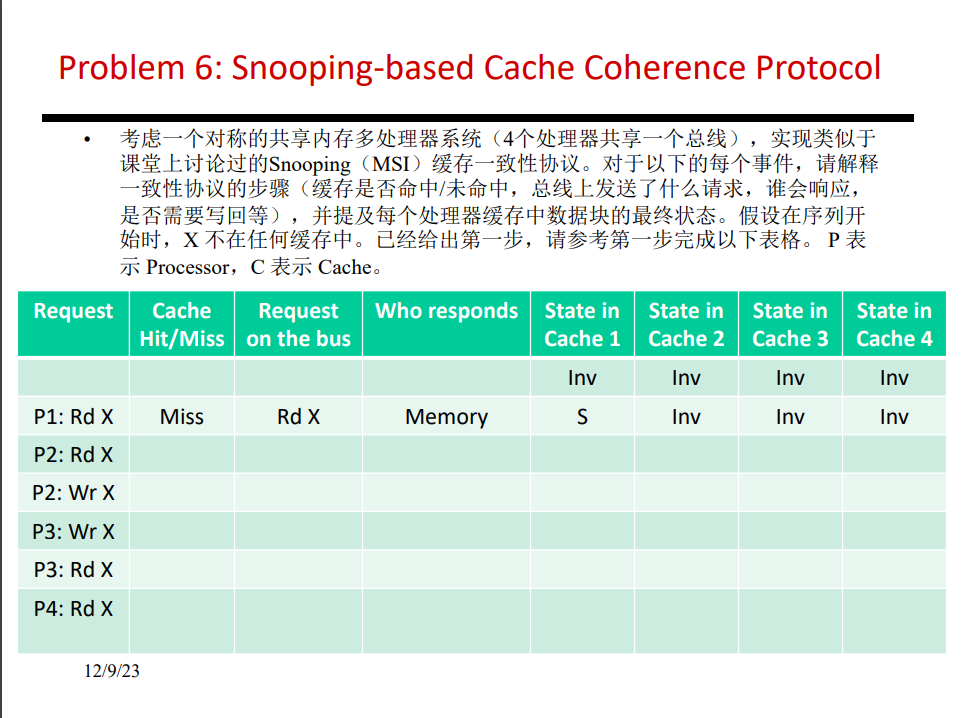

Problem 6:

| Request | Cache Hit/Miss | Request on the bus | Who responds | State in Cache 1 | State in Cache 2 | State in Cache 3 | State in Cache 4 |

|---|---|---|---|---|---|---|---|

| Inv | Inv | Inv | Inv | ||||

| P1:Rd X | Miss | Rd X | Memory | S | Inv | Inv | Inv |

| P2:Rd X | Miss | Rd X | Memory | S | S | Inv | Inv |

| P2:Wr X | Perms Miss | Rdx X/Upgrade X | No responds | Inv | M | Inv | Inv |

| P3:Wr X | Miss | Wr X | P2 | Inv | Inv | M | Inv |

| P3:Rd X | Hit | Inv | Inv | M | Inv | ||

| P4:Rd X | Miss | Rd X | P3 responds. Mem wrtbk |

Inv | Inv | S | S |

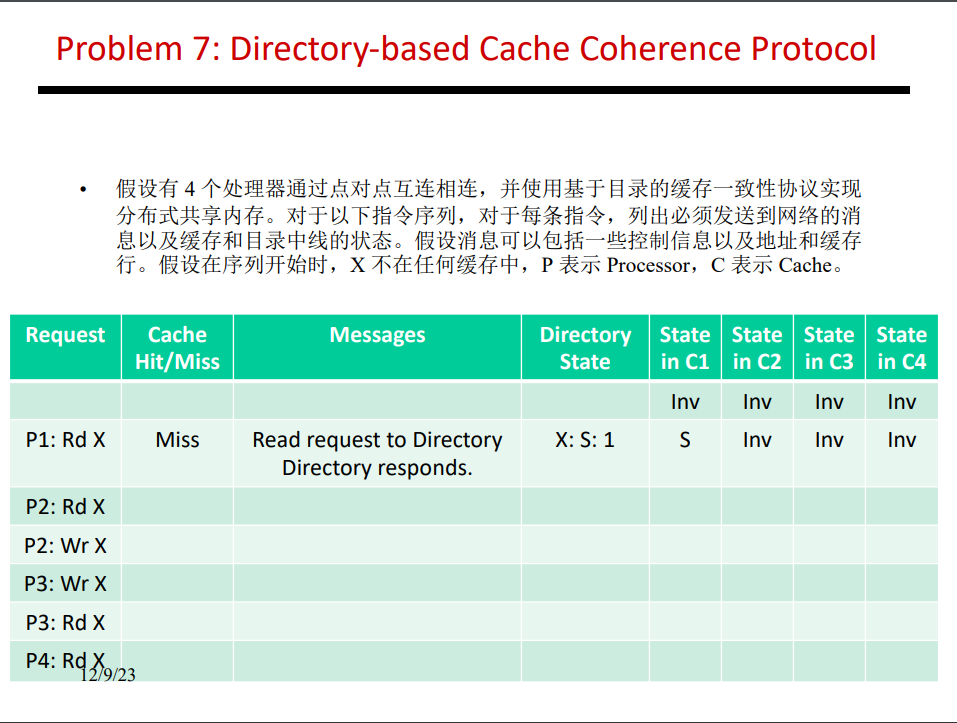

Problem 7:

| Request | Cache Hit/Miss | Messages | Directory State | State in Cache 1 | State in Cache 2 | State in Cache 3 | State in Cache 4 |

|---|---|---|---|---|---|---|---|

| Inv | Inv | Inv | Inv | ||||

| P1:Rd X | Miss | Read request to Directory; Directory responds |

X: S: 1 | S | Inv | Inv | Inv |

| P2:Rd X | Miss | Read request to Directory; Directory responds |

X: S: | S | S | Inv | Inv |

| P2:Wr X | Perms Miss | Upgrade request to Directory; Directory Inv request P1; P1 Inv response Directory; Directory grants perms to P2; |

X: M: 2 | Inv | M | Inv | Inv |

| P3:Wr X | Miss | Write request to Directory; Directory Inv request P2; P2 Inv response Directory with data X; Directory Write response with data X; |

X: M: 3 | Inv | Inv | M | Inv |

| P3:Rd X | Hit | X: M: 3 | Inv | Inv | M | Inv | |

| P4:Rd X | Miss | P4 Read request to Directory Directory Down request P3 P3 Down response Directory with data X Memory write back Directory responds P4 with data X |

X: S: | Inv | Inv | S | S |

致谢

[1] 以上图片来自于中国科学院大学-计算机体系结构刘珂老师的课程。

浙公网安备 33010602011771号

浙公网安备 33010602011771号