1.SDRAM原理

black

(1)SDRAM内部存储结构:

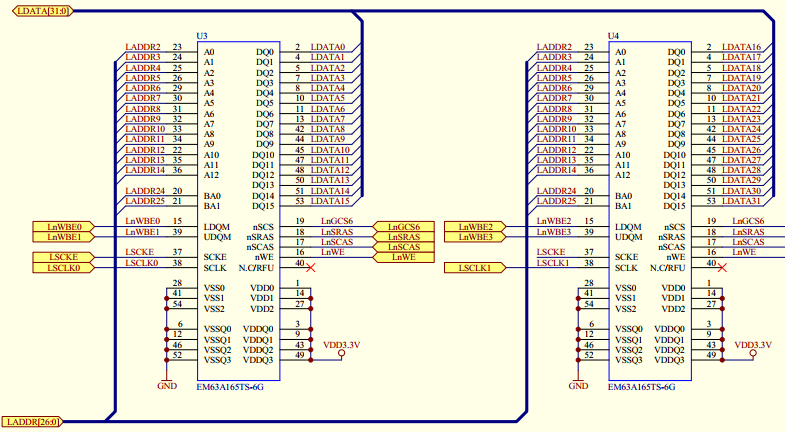

(2)再看看与2440连接的SDRAM原理图:

sdram引脚说明:

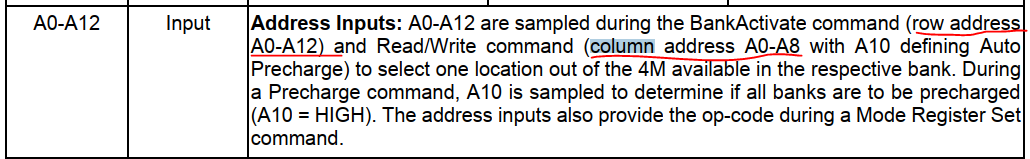

A0-A12:地址总线

D0-D15:数据总线(位宽16,2片级联成位宽32)

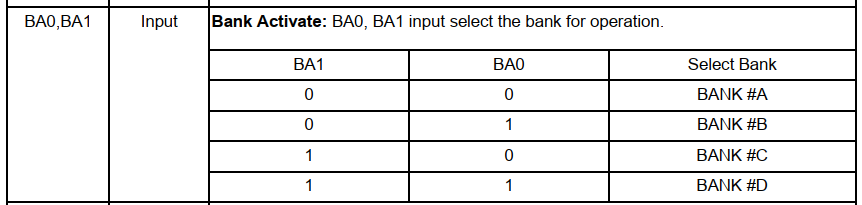

BA0-BA1:bank选择

nSCS:片选

nSRAS:行地址选择

nSCAS:列地址选择

nWE:写使能

SCLK:时钟

SCKE:时钟使能

(3)SDRAM的地址范围:

之前我们讲“二、不同位宽外设与CPU地址总线的连接”这一节的时候,我们留下了一个问题,SDRAM的地址范围是多少?

我们知道地址范围肯定是base_addr + size。我们根据片选接了nGCS6,base_addr=0x3000,0000,那么size是多大呢?

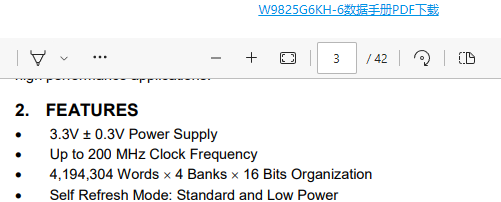

下图是我截取的sdram手册上的特性描述:

我们看见容量为:4M word x 16-bit x 4-bank = 32M,再看原理图我们是两片级联,所以容量为4M word x 32-bit x 4-bank=64M。所以地址范围是[0x3000_0000 ~ 0x33ff_ffff]

再以W9825G6KH这款SDRAM为例,地址总线A0-A12,数据总线D0-D15,因此内存大小:2^13 * 2^9 = = 4194304,等于4M,加上有4个bank,数据为宽16位,因此内存大小4Mx4x2字节

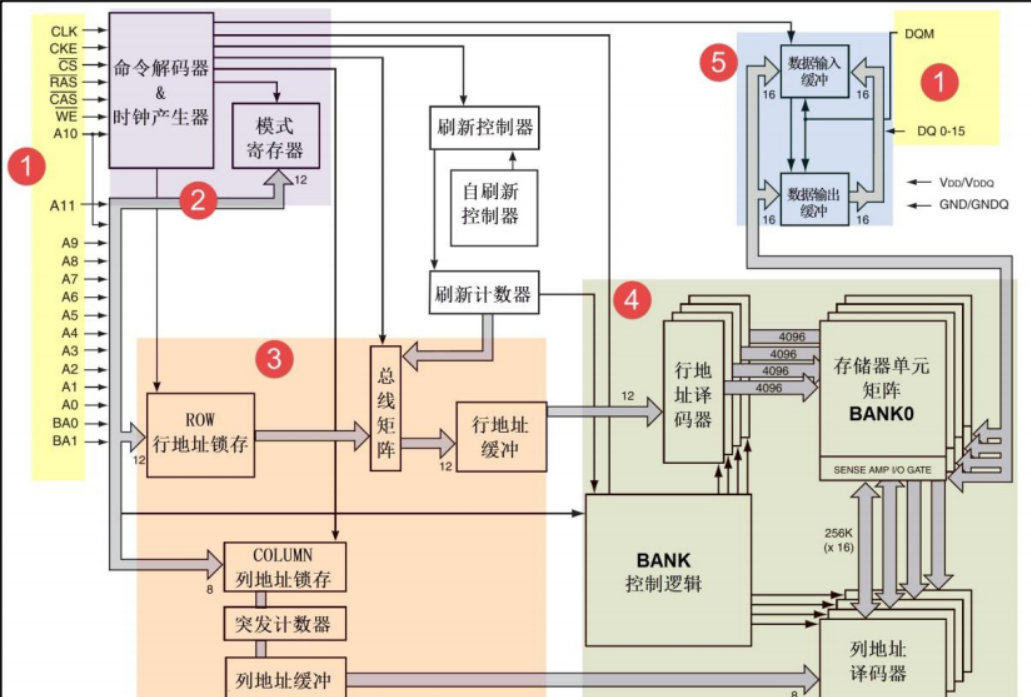

框图翻译成中文形式:

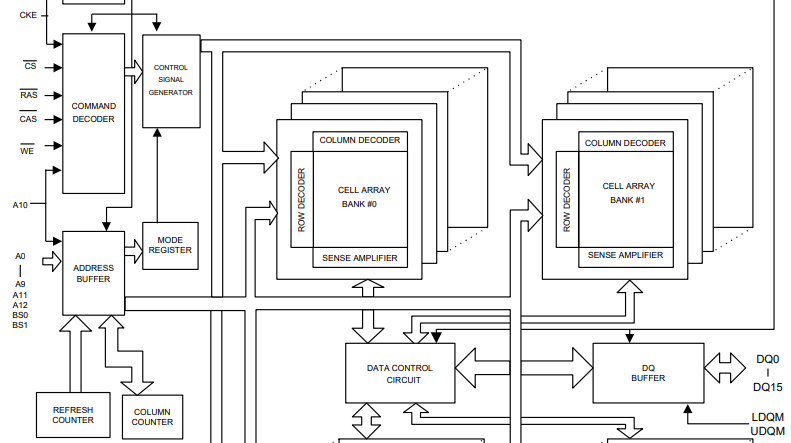

CLK:时钟线,SDRAM 是同步动态随机存储器,“同步”的意思就是时钟,因此需要一根额外的时钟线,这是和 SRAM 最大的不同,SRAM 没有时钟线。

CKE:时钟使能信号线,SRAM 没有 CKE 信号。

CS:片选信号,这个和 SRAM 一样,都有片选信号。

RAS:行选通信号,低电平有效,SDRAM 和 SRAM 的寻址方式不同,SDRAM 按照行、列来确定某个具体的存储区域。因此就有行地址和列地址之分,行地址和列地址共同复用同一组地址线,要访问某一个地址区域,必须要先后发送行地址和列地址

CAS:列选通信号,和 RAS 类似,低电平有效,选中以后就可以发送列地址了。

WE:写使能信号,低电平有效

A0-A12: 地址线

DQ0-DQ15: 16位数据线

BS0-BS1: BANK 选择线

LDQM,UDQM: 高低字节数据选择线

(4)SDRAM数据访问原理:

我们知道64M=220*26=226,那么需要26条地址线,再看看原理图,我们发现SDRAM的地址线A[12:0]只有13条,那么最多只能访问213=8K的数据,地址线明显配不上这么大的容量,那么它是如何解决的呢?

答:当然是拆分地址了,地址分多次传输。我们从SDRAM的内部存储结构得知要确定SDRAM的一个存储单元,先确定是哪个bank,然后再确定在哪一行、哪一列即可。

SDRAM有4个bank,由BA0、BA1决定选中哪个bank,查看SDRAM手册见下图;

然后通过选中nSRAS选中行地址,从而发送行地址;最后通过选中nSCAS选中列地址,从而发送列地址。

举个栗子:

CPU执行如下指令:

ldr r0, =0x30000000;

ldr r1, [r0]; 从SDRAM基地址读取4byte数据

过程分析:

1.发出片选信号nGCS6,选中SDRAM

2.发出bank选中信号(BA0,BA1),确定是SDRAM上的哪个bank,从原理图得知CPU的ADDR24、ADDR25对应SDRAM上的BA0,BA1,所以让BA0、BA1=00,选中bankA。

从SDRAM手册确定行列地址的数目,如下图:

3.发出行地址信号nSRAS,使能行地址传输。传输行地址,确定是哪一行(看SDRAM手册确定行地址数(A12-A0)13条)

4.发出列地址信号nnSCAS,使能列地址传输。传输列地址,确定是哪一列(看SDRAM手册确定列地址(A8-A0)9条)

从而发送完整的0x30000000地址到了SDRAM,SDRAM返回4byte数据给CPU。

浙公网安备 33010602011771号

浙公网安备 33010602011771号