基于STM32F407MAC与DP83848实现以太网通讯一(STM32以太网(ETH)外设)

STM32F4xx 可以通过以太网按照 IEEE 802.3-2002 标准发送和接收数据。支持与外部物理层 (PHY) 相连的两个工业标准接口:默认情况下使用的介质独立接口 (MII)(在 IEEE 802.3 规范中定义)和简化介质独立接口 (RMII)。

具体的以太网(ETM)特性参考:STM32F4xx中文参考手册

这里将重要的地方进行说明

一、STM32F4xx以太网(ETH)框图

以太网外设包括带专用 DMA 控制器的 MAC 802.3(介质访问控制)。默认使用MII接口,可通过配置寄存器(SYSCFG_PMC)切换位RMII接口,后面的DP83848使用的就是RMII接口。

DMA控制器通过AHB主接口用于控制数据传输,DMA从接口用于访问CSR(Control and Status Registers)

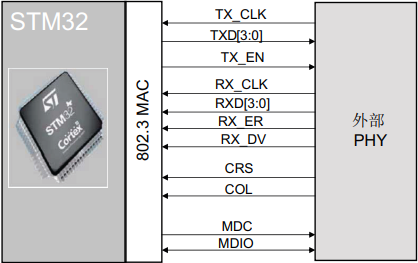

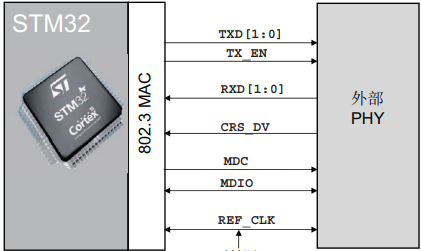

二、MII/RMII接口

2.1.MII/RMII接口

MII/RMII接口主要用作以太网数据传输

- TX CLK:数据发送参考时钟.10Mbis / s时为2.5 mhz, 100 mbit / s时为25兆赫。(MII)

- RX_CLK:数据接收参考时钟。10Mbis/s时为2.5MHz, 100Mbit/s时为25MHz。(MII)

- TX_EN:数据发送使能。数据发送过程保持有效。

- TXD[3:0]/[1:0]:数据发送信号线, RMII为TXD[3:0]4位, RMII为TXD[1:0]2位。

- CRS:载波侦听信号,PHY芯片驱动,发送或接收介质处于非空闲状态时使能。全双工时该信号线无效。(MII)

- COL:冲突检测信号,PHY芯片驱动,检测到介质上存在冲突,使能该信号。全双工时该信号线无效。(MII)

- RXD[3:0]/ [1:0]:数据接收信号线,PHY芯片同步驱动, RMII为TXD[3:0]4位, RMII为TXD[1:0]2位, MII模式时RX_DV禁止, RX_ER使能时RX_D[3:0]用来传输特定信息(参考STM32F4xx中文参考手册-表164 RX接口信号编码)。

- RX_DV:接收数据有效信号,PHY芯片驱动。(MII)

- CRS_DV: CRS与RX_DV功能的整合信号线,PHY芯片驱动,介质在不同状态会自动切换,(RMII)

- RX_ER:接收错误信号。PHY芯片驱动,只有当RX_DV与RX_ER同时有效时错误有效。(MII)

- REF_CLK: RMII模式外部50MHz参考时钟。可以直接使用外部晶振接入MAC和PHY,也可以通过STM3的PLL来驱动。(RMII)

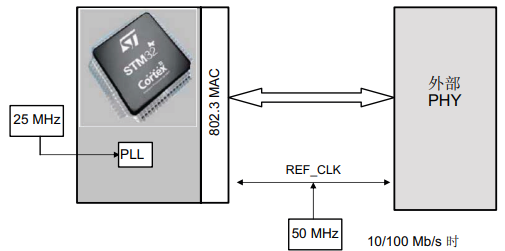

2.2.MII/RMII时钟源

使用MII接口时,STM32F4可使用外部25MHz高速时钟(HSE),通过MCO引脚输出25MHz驱动PHY,PHY也可单独使用外部25MHz时钟源。

使用RMII接口时,STM32F4使用外部25MHz时钟源时,可通过STM32内部PLL生成50MHz来驱动PHY,也可直接使用外部50MHz时钟源。

三、SMI接口

SMI接口(station management interface)通过时钟线(MDC)以及数据线(MDIO)访问PYH寄存器。

STM32F4xx的SMI接口支持访问32个PHY,可通过应用程序选择一个PHY,然后从PHY包含的32个寄存器选择一个,发送控制数据或者接受状态信息。任一时间只能对一个PHY中的一个寄存器寻址。

MDC (PC1复用):周期性时钟输出,最大频率2.5MHz,最小高低电平时间必须均为160ns,最小时钟周期必须为400ns。,最小时钟周期必须为400ns。

MDIO (PA2 复用):数据输入/输出同步传输 PYH 设备状态信息。

3.1.SMI帧字段

报头:与 PHY 建立同步

起始:验证 1->01 转变

操作:事务类型(读 or 写)

PADDR: PYH 地址,5 位,MSB

RADDR: PHY寄存器地址,5位,MSB

TA:周转字段,主要用于避免读取时的竞争。

数据:先发送 ETH_MIID 位 15

空闲:MDIO 高阻态(PHY 内部上拉为 1)

3.2.SMI写操作

- 初始化MAC MII地址寄存器(ETH_MACMIIAR)写入PHY地址、PHY寄存器地址、时钟范围(CR),初始化MAC MII数据寄存器(ETH_MACMIIDR)

- 将写入位(MW)、繁忙位(MB)置1

- 触发对PHY寄存器写操作事务(事务期间对ETH_MACMIIAR与ETH_MACMIIDR的写操作无效)

- 写操作完成

- 复位繁忙位(MB)

3.3.SMI读操作

- 初始化MAC MII地址寄存器(ETH_MACMIIAR)写入PHY地址、PHY寄存器地址、时钟范围(CR),初始化MAC MII数据寄存器(ETH_MACMIIDR)

- 将写入位(MW)清0,繁忙位(MB)置1

- 触发对PHY寄存器读操作事务(事务期间对ETH_MACMIIAR与ETH_MACMIIDR的写操作无效)

- 复位繁忙位(MB)

- 将从PHY中读取的数据更新到MII数据寄存器(ETH_MACMIIDR)

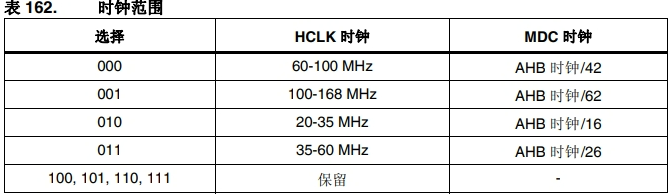

3.4.SMI时钟选择

SMI时钟源应为AHB时钟,分频系数取决于MII地址寄存器(MII Address register)设置的时钟范围。

ETH外设硬件主要就是了解MII/RMII与SMI接口,以及用于MAC DMA的AHB主从接口的数据流向(参考开头的系统框图)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号