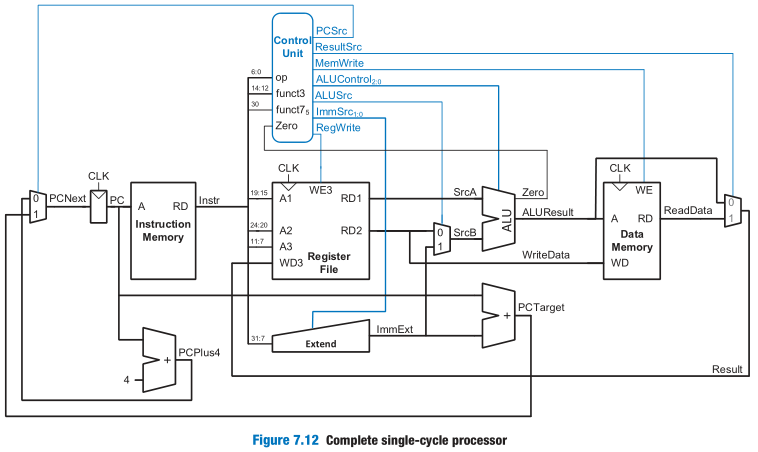

Complete single-cycle processor

Heavy lines indicate 32-bit data busses. Medium lines indicate narrower busses, such as the 5-bit address busses on the register file. Narrow lines indicate 1-bit wires, and blue lines are used for control signals, such as the register file write enable. Registers usually have a reset input to put them into a known state at start-up, but reset is not shown to reduce clutter.

bus pl [plural] buses; US also busses

To the uninitiated, building a microprocessor may seem like black magic. But it is actually relatively straightforward and, by this point, you have learned everything you need to know. Microarchitecture is the connection between logic and architecture. It is the specific arrangement of registers, arithmetic logic units (ALUs), finite state machines (FSMs), memories, and other logic building blocks needed to implement an architecture.

Unlike other architectures, such as MIPS and ARM, RISC-V does not include instructions (or exceptions) for detecting overflow because it can be detected using a series of existing instructions. The following code detects overflow when adding two signed numbers, t1 and t2:

add t0, t1, t2

slti t3, t2, 0

slt t4, t0, t1

bne t3, t4, overflow

In equation form, overflow = (t2 < 0) & (t0 ≥ t1) | (t2 ≥ 0) & (t0 < t1)

In words, overflow occurs when one operand is negative (t3 = 1) and the result is not less than the other operand (t4 = 0), or when one operand is greater than or equal to 0 (t3 = 0), and the result is less than the other operand (t4 = 1).

Set less than instructions compare either two registers (slt) or a register and an immediate (slti).

RISC有点美丽冻人啊。x86说“我保暖性好”,RISC说“我优雅”。

浙公网安备 33010602011771号

浙公网安备 33010602011771号