原来D latch和D flip flop不一样啊

CMOS circuits favor NAND and NOR gates because these gates can be built directly from CMOS transistors without requiring extra NOT gates.

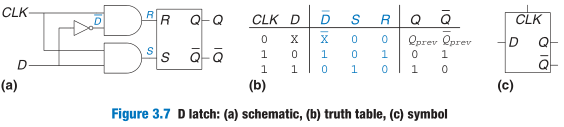

The D latch updates its state continuously while CLK = 1.

Calculating the propagation delay of a circuit involves identifying the critical path through the circuit, then adding up the propagation delays of each element along that path.

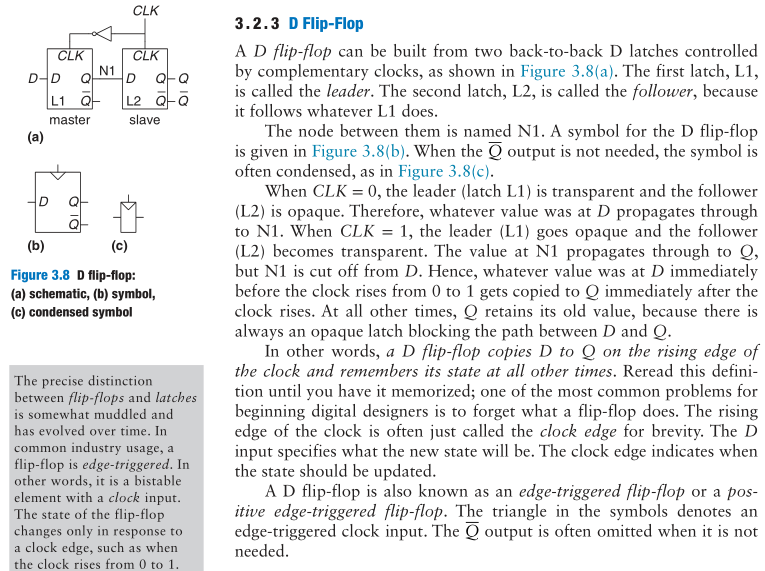

A D flip-flop can be built from two back-to-back D latches controlled by complementary clocks, as shown in Figure 3.8(a). The first latch, L1, is called the leader. The second latch, L2, is called the follower, because it follows whatever L1 does.

A D flip-flop is also known as an edge-triggered flip-flop or a positive edge-triggered flip-flop.

浙公网安备 33010602011771号

浙公网安备 33010602011771号