Verilog之[-2]贴

改编自Deepak Kumar Tala@www.asic-world.com和Shubham Singh的Verilog Fundamentals@csg.csail.mit.edu/6.375等。参考资料下载 3MB

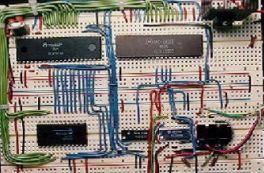

面包板(Bread Board)和印刷电路板(Printed Circuit Board, PCB): 处理数十个门(Gate)。

在屏幕上画若干个module,鼠标点下module A的port x和module B的port y,程序画线把它们连起来。拖动A和B,线会跟着跑。EDA(曾)是CAD的一种。不知道为啥不叫circuit和pin。

然后用文字描述gate和它们之间的连接。与上一步相比,像是所见即所得的编辑器变成直接改HTML代码,如TinyMCE和TextBox,或者WPS Office和DOS下的WPS。后者在文本中嵌入描述字体等的命令,可以模拟显示: render和present. 或者说像LaTex和Word. IC业的成功告诉我们: 字符串还是比图好处理。:-) .docx是XML文件。

Verilog里可以进行gate level的描述: nand g1(ab, a, b), g2(aab, a, ab), g3(bab, b, ab), g4(c, aab, bab); 像消消乐啊。

可以这么干不等于必须这么干或大多数人这么干。为什么不一步跨到Register Transfer Level (RTL)? 可能当时没想到,更可能当时电脑太慢。

好像有些电路把输出接到自己的输入,此时需要<=语句。q <= d; q_bar <= !d; 不能充分展示它的威力,只是强调了q和q_bar是同时冒出来的,没有时间先后之分。

当一个module就一个procedure时,procedure就一条语句时,assign是多余的,assign a=b;和a=b; a<=b;都一样。BASIC里的let去掉了,JavaScript里的let x=3有使x成为局部变量的作用,C/C++里我们可以:#define in_the_name_of_black_magic_i_command /*empty*/,然后in_the_name_of_black_magic_i_command a = b;

Verilog was started initially as a proprietary hardware modeling language by Gateway Design Automation Inc. around 1984. It is rumored that the original language was designed by taking features from the most popular HDL language of the time, called HiLo as well as from traditional computer language such as C. At that time, Verilog was not standardized and the language modified itself in almost all the revisions that came out within 1984 to 1990.

Verilog simulator was first used beginning in 1985 and was extended substantially through 1987. The first major extension was Verilog-XL, which added the infamous "XL algorithm" which was a very efficient method for doing gate-level simulation. "infamous"原文如此,可能有故事。

In 1990, Cadence recognized that if Verilog remained a closed language, the pressures of standardization would eventually cause the industry to shift to VHDL... Verilog became an IEEE standard in December, 1995. The standard combined both the Verilog language syntax and the PLI in a single volume. New features have been added to Verilog, and the new version is called Verilog 2001, which seems to have fixed lots of problems. 原文是lot of problems that Verilog 1995 had, 我给加了个s - 英语考试对我们太不友好了。

void fn(a, b) int a, b; {} 是合法的/过时的C语法。现在Verilog也(早)可以xor_gate_level(output c, input a, input b),不要再a,b,c各写两遍了。

我国科学家早就人工合成了牛胰岛素,论文题目不叫《牛胰岛素的人工综合》。Logic Synthesis咋翻译好?

CSDN上有人说for循环, Verilog会重复你的电路。我觉得说得很精辟。优化C/C++程序时我们也会做循环展开的事情,例如for(int i=0; i<4; i++) sth; 变成sth; sth; sth; sth. 4太小不值得上跳转指令,4个sth占地方不大。忘了在哪里看到过for里xor的例子,Verilog还要把n个xor门串联起来——光摆上4个门而不把它们连起来是没有意义的。虽然还是"串行",但速度只受光速的制约(说得过了点)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号