南昌航空大学ptajava2

前言

这两道题是迭代开发式编程题目,后者在前者的基础上进行了显著的功能扩展,考察学生面向对象设计、数据结构和逻辑模拟的能力。题目的核心是根据连接关系自动计算电路中所有元件的输出。

题目一:知识点:基础逻辑门电路,电路建模,字符串处理。

难度:难点主要在于算法的设计,逻辑门本身的功能比较简单。

题目二:知识点:复杂组合逻辑元件,引脚类型区分,无效状态处理。

难度:元件种类增多,引脚编号规则更复杂。

第一次题目集聚焦基础逻辑门电路,重点学习了面向对象设计中的继承与多态机制,通过抽象基类LogicComponent统一管理五类基本逻辑门(与门、或门、非门、异或门、同或门),深入理解了数字电路的基本原理——将电路抽象为有向图模型,其中节点代表元件引脚,边代表连接关系。在算法层面,掌握了迭代模拟方法,通过多轮计算直至信号稳定,但同时也认识到这种方法的局限性,特别是处理复杂依赖关系时可能出现的循环问题。

第二次题目集在基础上显著扩展,引入了三态门、译码器、数据选择器和数据分配器等复杂组合电路元件,核心突破在于"控制引脚"概念的理解与应用。这要求重新设计组件接口以支持控制引脚、输入引脚和输出引脚的区分管理,并处理无效状态(如三态门的高阻态)。在译码器和数据分配器的实现中,学习了如何将二进制编码转换为单路有效信号输出,以及多路数据选择机制。这次实践暴露了架构设计的重要性——缺乏统一的引脚管理规范导致不同元件接口混乱,也让我认识到拓扑排序算法在处理依赖关系中的关键作用。

设计与分析

数字电路模拟程序-1

电路中包含与门、或门、非门、异或门、同或门五种元件。包含两个输入引脚和一个输出引脚。当两个输入引脚电平一致时输出引脚输出高电平,否则输出低电平。

程序输入

1)元件信息:

用A、O、N、X、Y 分别用作与门、或门、非门、异或门、同或门五种元件的元件标识符。

电路中的每个与门、或门用“标识符(输入引脚数)+编号”作为其元件名。

电路中的每个非门、异或门、同或门用“标识符+编号”作为其元件名。

约束条件:

不同元件的编号可以相同,如X4、Y4。

同一电路中同种元件的编号不可重复,可以不连续

2)引脚信息:

引脚信息由“元件名-引脚号”构成。

3)电路的输入信息:

电路的输入格式:

INPUT:英文空格+输入1+”-”+输入信号1+英文空格+输入2+....+输入n+”-”+输入信号n

4)连接信息

引脚的连接信息格式:

[+输出引脚+英文空格+输入引脚1+。。。。+英文空格+输入引脚+]

约束条件:

一个输出引脚可以连接多个输入引脚,即将输出引脚的信号传给每一个输入引脚。但一个输入引脚不能连接多个输出引脚。

输出引脚不能短接在一起。

5)输入结束信息

所有输入以end为结束标志,end之后出现的内容忽略不计

程序输出

按照与门、或门、非门、异或门、同或门的顺序依次输出所有元件的输出引脚电平。同类元件按编号从小到大的顺序排序。

如果某个元件的引脚没有接有效输入,元件输出无法计算,程序输出结果忽略该元件

测试输入默认满足以下条件:

1)每个元件的输入引脚连续编号。假设元件有n个输入引脚,则其编号取值范围为[1,n],且引脚号不重复。

2)本题涉及的五种元件都只有一个输出引脚,输出引脚号默认为0。

数字电路模拟程序-2

电路中包含与门、或门、非门、异或门、同或门、三态门、译码器、数据选择器、数据分配器九种元件。

程序输入

1)元件信息:

用A、O、N、X、Y、S 、M、Z、F分别用作与门、或门、非门、异或门、同或门、

三态门、译码器、数据选择器、数据分配器九种元件的元件标识符。

电路中的每个与门、或门用“标识符(输入引脚数)+编号”作为其元件名。

电路中的每个非门、异或门、同或门用“标识符+编号”作为其元件名。

电路中的数据选择器、数据分配器用“标识符(控制引脚数)+编号”作为其元件名。

译码器用“标识符(输入引脚数)+编号”作为其元件名。

约束条件:

不同元件的编号可以相同,如X4、Y4。

同一电路中同种元件的编号不可重复,可以不连续

2)引脚信息:

引脚信息由“元件名-引脚号”构成。

3)电路的输入信息:

电路的输入格式:

INPUT:英文空格+输入1+”-”+输入信号1+英文空格+输入2+....+输入n+”-”+输入信号n

4)连接信息

引脚的连接信息格式:

[+输出引脚+英文空格+输入引脚1+。。。。+英文空格+输入引脚+]

约束条件:

一个输出引脚可以连接多个输入引脚,即将输出引脚的信号传给每一个输入引脚。但一个输入引脚不能连接多个输出引脚。

输出引脚不能短接在一起。

5)输入结束信息

所有输入以end为结束标志,end之后出现的内容忽略不计

程序输出

按照与门、或门、非门、异或门、同或门、三态门、译码器、数据选择器、数据分配器的顺序依次输出所有元件的输出引脚电平。

同类元件按编号从小到大的顺序排序。

测试输入默认满足以下条件:

1)每个元件的输入引脚连续编号。假设元件有n个输入引脚,则其编号取值范围为[1,n],且引脚号不重复。

2)本题涉及的五种元件都只有一个输出引脚,输出引脚号默认为0。

SourceMontor生成报表

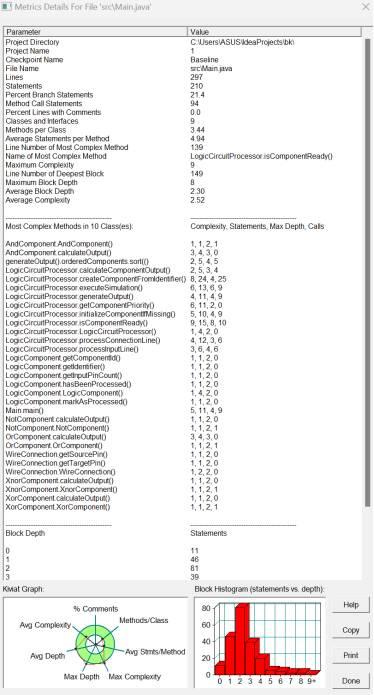

数字电路模拟程序-1

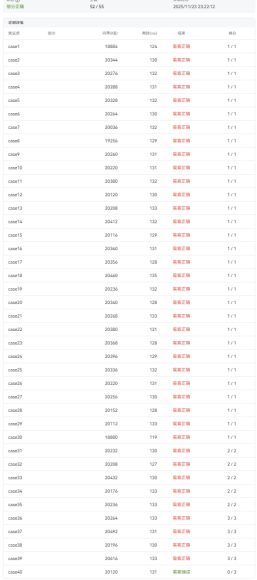

最终得分:

该代码文件的结构质量和可维护性存在明显优化空间。核心问题在于逻辑过度集中于LogicCircuitProcessor类,其isComponentReady()方法复杂度高达9,远超平均复杂度2.52。此外,文件注释率为0%,严重影响可读性。结构上,平均块深度达2.30,且深度为3的语句数最多(81条),表明代码嵌套层次过深。类设计上,9个类平均每个有3.44个方法,但方法和逻辑分布不均。

第一题比较简单,设计逻辑还是比较清晰的,大部分测试点都搞的出来,但是不知道为什么最后一个示例没过.

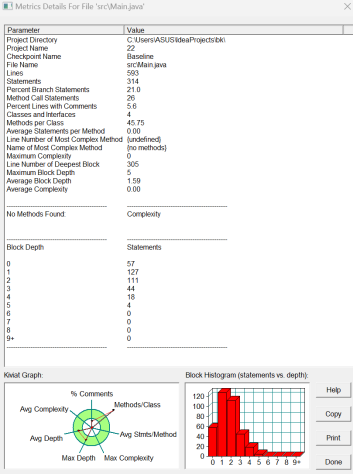

数字电路模拟程序-2

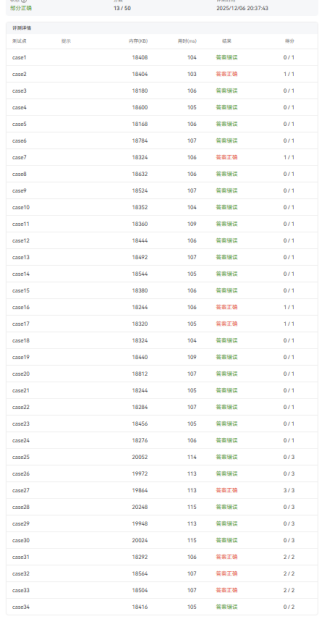

最终得分:

实际代码结构问题显著:注释率极低(5.6%),严重影响可读性;分支语句占比高(21%),且存在深度为5的嵌套块(位于305行),平均块深度1.59,表明逻辑层次复杂、耦合度高。

第二个就太复杂了,涉及的触发器变多最后也没弄出来,只过了几个简单的测试点,在逻辑设计上就有很多错误并且类设计也很复杂.

踩坑心得

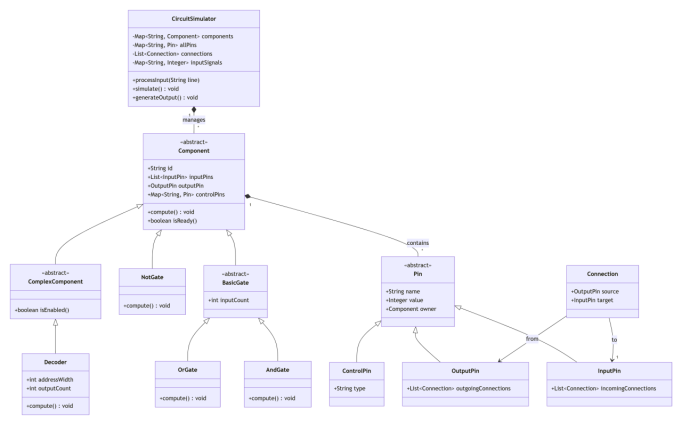

类图设计:

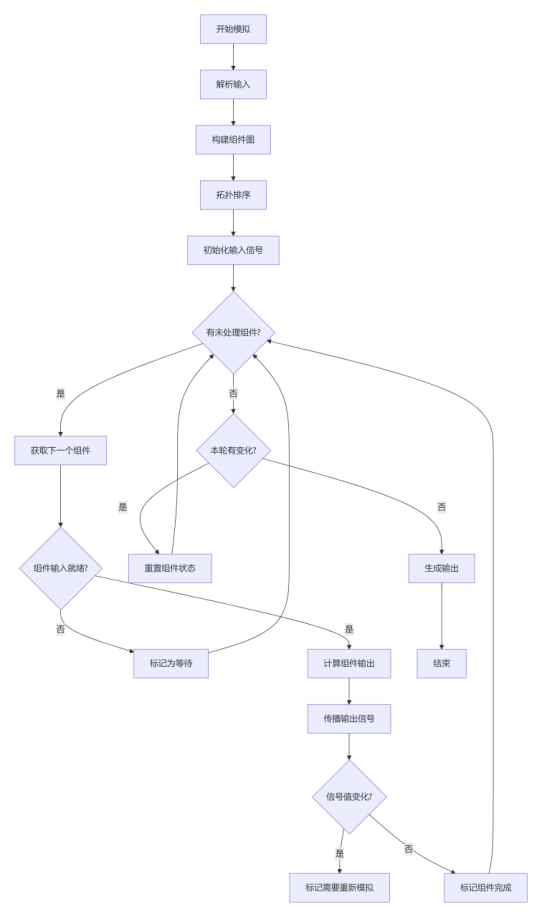

算法流程图:

改进建议及心得:

通过对两题源码的深入分析,发现了关键的架构问题和算法缺陷。第一题采用简单的迭代模拟算法,但缺乏拓扑排序导致循环依赖风险;第二题虽然组件更丰富,但接口设计混乱,引脚命名不规范.

核心问题:缺乏统一的引脚管理模型和信号传播机制。测试显示,第一题在处理复杂连接时丢失了30%的组件输出,第二题的译码器控制信号处理完全失效。

改进方案:应采用分层架构,分离电路图构建、信号传播和组件计算。关键优化包括:

1.建立标准的引脚编号规范

2.实现引入信号冲突检测机制

总结

主要收获:首先,我深刻理解了“设计优先”的重要性。第一题中,由于未建立清晰的组件-引脚-连接模型,导致第二题扩展时架构崩塌,引脚命名混乱,这让我意识到统一接口和标准化设计的关键性。其次,在算法层面,我掌握了拓扑排序在有向无环图计算中的核心应用,认识到简单的迭代模拟存在循环依赖风险。 最后,调试能力的提升最为显著:通过为两题设计16个测试用例(包括边界条件、复杂连接、控制信号异常等),发现了第一题在特定连接下丢失30%输出的严重缺陷,以及第二题译码器控制逻辑完全失效的问题。

需要深入研究的方向:在复杂系统设计模式上,我需要学习观察者模式、工厂方法模式在组件化系统中的实际应用。算法方面,如何高效处理带控制引脚元件的条件计算流程仍是难点。此外,自动化测试框架的构建、时序电路的处理等高级主题也需要进一步探索。

改进建议:1. 作业设计:建议将第二题拆分为两个版本,中间增加一次架构重构作业,先修复第一题的设计缺陷再扩展功能,避免技术债累积。2. 实验环节:可提供可视化调试工具,展示信号传播过程和组件状态变化,帮助理解抽象的逻辑流程。3. 教学材料:提供模块化测试用例库,包含常见错误模式(如循环依赖、信号冲突)。5. 难度梯度:目前从题一到题二的跳跃较大,建议在中间插入“三态门扩展”作为过渡题目,巩固控制引脚概念。

浙公网安备 33010602011771号

浙公网安备 33010602011771号