【心得】Lattice Diamond 后端约束实战小结

IOB约束

参考《插入IO寄存器和位置约束---lattice&diamond》,推荐的方法是:

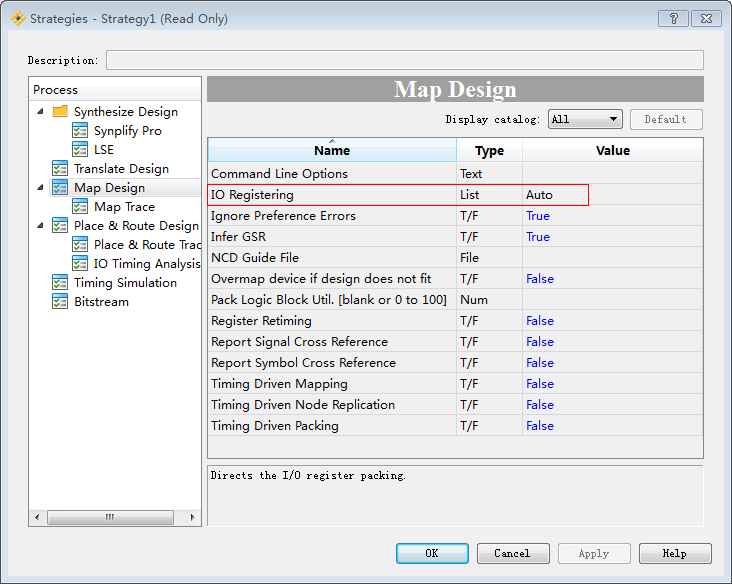

1、在strategy设置【Map Design-IO Registering】为Auto

2、修改代码接口描述,添加/* synthesis syn_useioff = 1*/语句(也可以不加,见第3条),如:

1 input VSRC_CLK /* synthesis syn_useioff = 1*/,//I1,

2 output wire VSRC_RESET /* synthesis syn_useioff = 1*/,//O1,

3 input VSRC_VS /* synthesis syn_useioff = 1*/,//I1,

4 input VSRC_DE /* synthesis syn_useioff = 1*/,//I1,

5 input [15:0] VSRC_D /* synthesis syn_useioff = 1*/,//I16,

3、确保输入信号不被优化,可使用/* synthesis syn_preserve=1 */,将输入打拍的信号保留住。(注:这个才是关键,工具有时不理解为何要将输入信号多打几拍,就擅自帮我们将信号给优化了,这些需要保留的信号,都要使用preserve进行保留。)

1 //---------------------------------------------------------------------------- 2 // Register & Wire Definition 3 //---------------------------------------------------------------------------- 4 reg [5:0] hdmi_vs_dy,hdmi_hs_dy,hdmi_de_dy; 5 reg [15:0] hdmi_dat_d0/* synthesis syn_preserve=1 */; 6 reg [15:0] hdmi_dat_d1/* synthesis syn_preserve=1 */; 7 reg [15:0] hdmi_dat_d2/* synthesis syn_preserve=1 */;

检查IOB是否符合预期

方法1、打开【Tools-Spreadsheet View】,点击“Cell Mapping”选项卡,查看对应输入输出管脚的PIO Register是否为True。

方法2、也可以使用Follrpaln和Physical View查看:

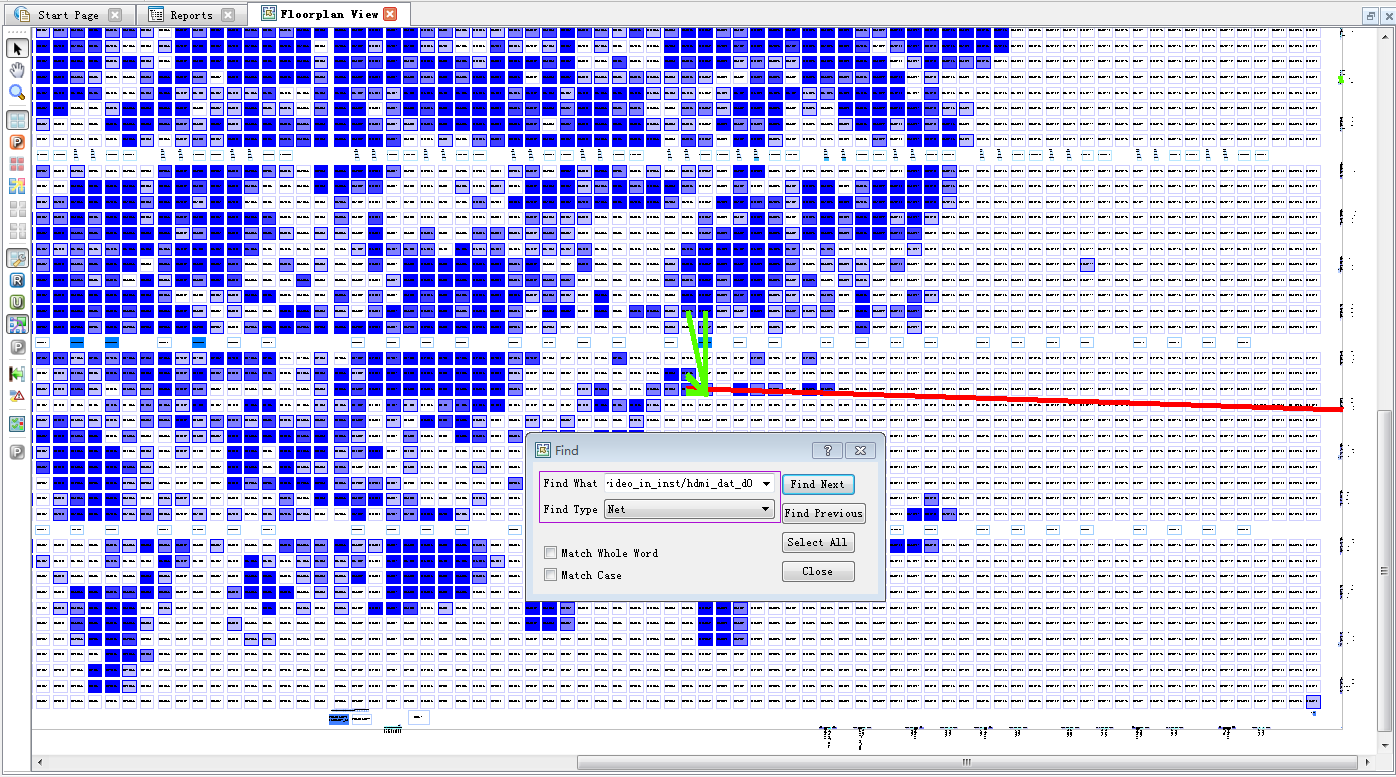

1、在Map之后,打开Floorplan View,使用Ctrl+f进行net的查找,可以按 video_input_top_16b_inst0/video_in_inst/hdmi_dat_d0 方式,从TOP层层下去找到第一级寄存器信号名。

2、找到net之后,右键,使用Physical View查看。

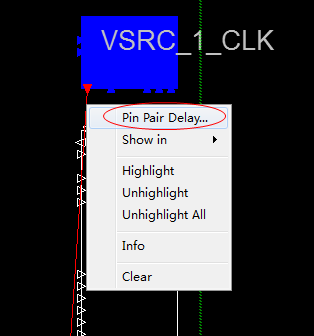

管脚VSRC_0_D[4]旁边的后缀为MGIOL的模块,就是PIO Register。若没放入IOB,则前缀IOL_的模块不是蓝色。

查看信号延时

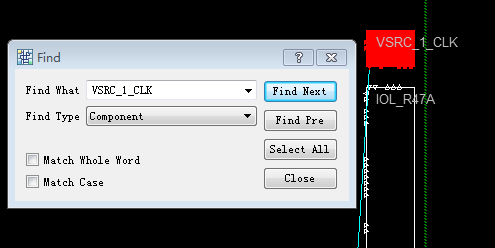

在Physical View,查找某个PIN脚信号,比如VSRC_1_CLK(类型选择component),然后点击该模块下边的net,右键Pin Pair Delay可查看该信号延时。

关于时序收敛

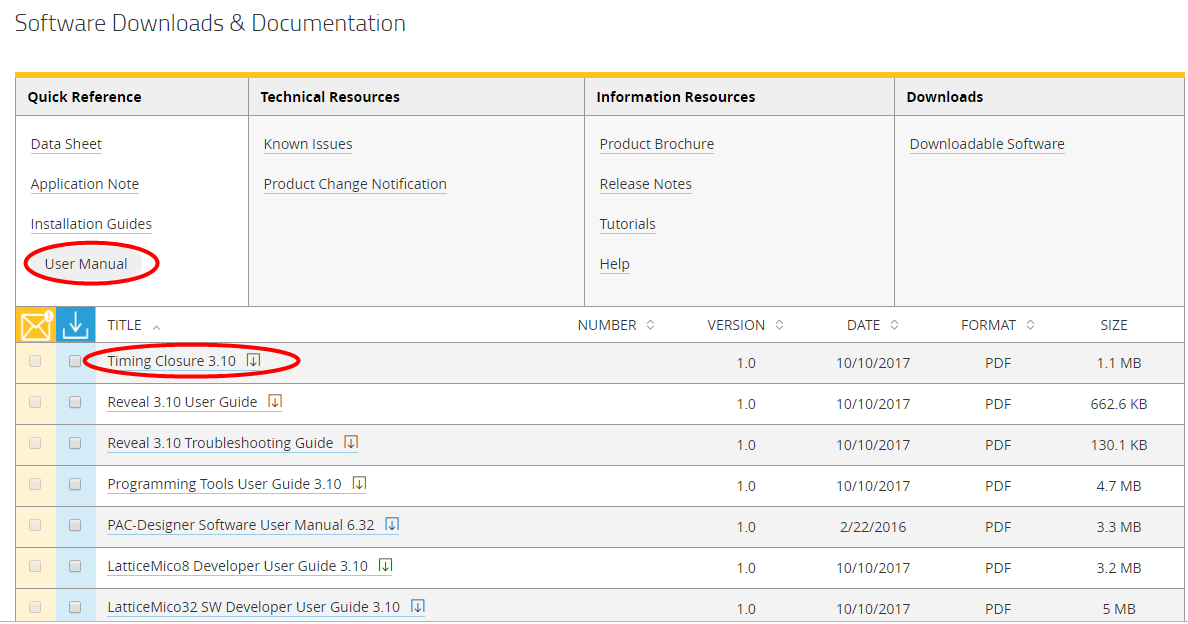

参考官网的帮助文档,Timing Closure 3.10。

该文档102页,关于时序收敛的一些建议:

1、综合Syplify Pro设置:

- 打开Pipelining and retiming

- 关闭Resource Sharing

- 可以使用sdc文件

2、查看Synplify Pro的报告,关注时钟频率的估计值。

3、Map设置:检测未约束的连接和路径;设置full name;Report Style选择Error Timing Report,这样只显示error的路径,方便快速定位问题。

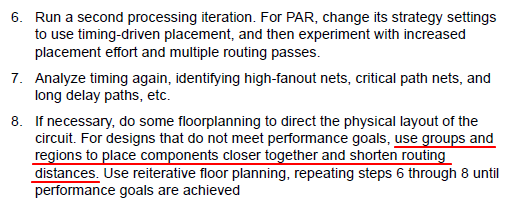

4、第36页给出优化时序的建议:

5、使用GSR资源。Syplify设置里建议关闭,在MAP设置里打开。

6、使用PAR_ADJ关键字,使得在PAR阶段按过约束的频率进行P&R,但在TRACE分析时按正常频率分析(第46页、71页)。

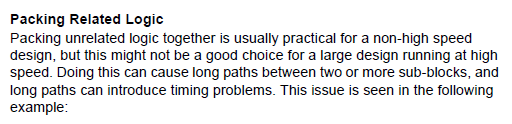

7、尝试将关键路径UGROUP(第82页),以及97页的Packing相关逻辑。

8、关注logic levels是否过多。

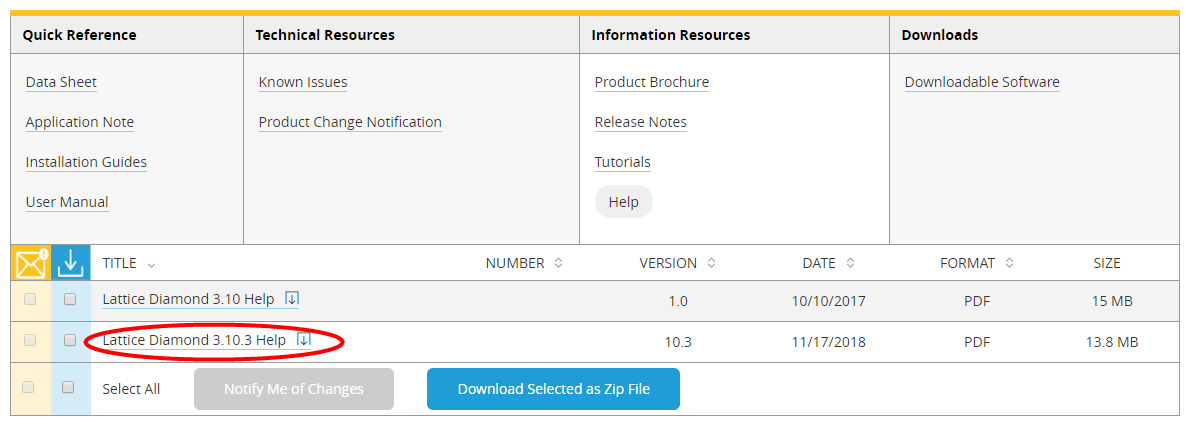

进一步的详细帮助信息,可下载13.8M的《Lattice_Diamond_3_10_3_Help.pdf》。

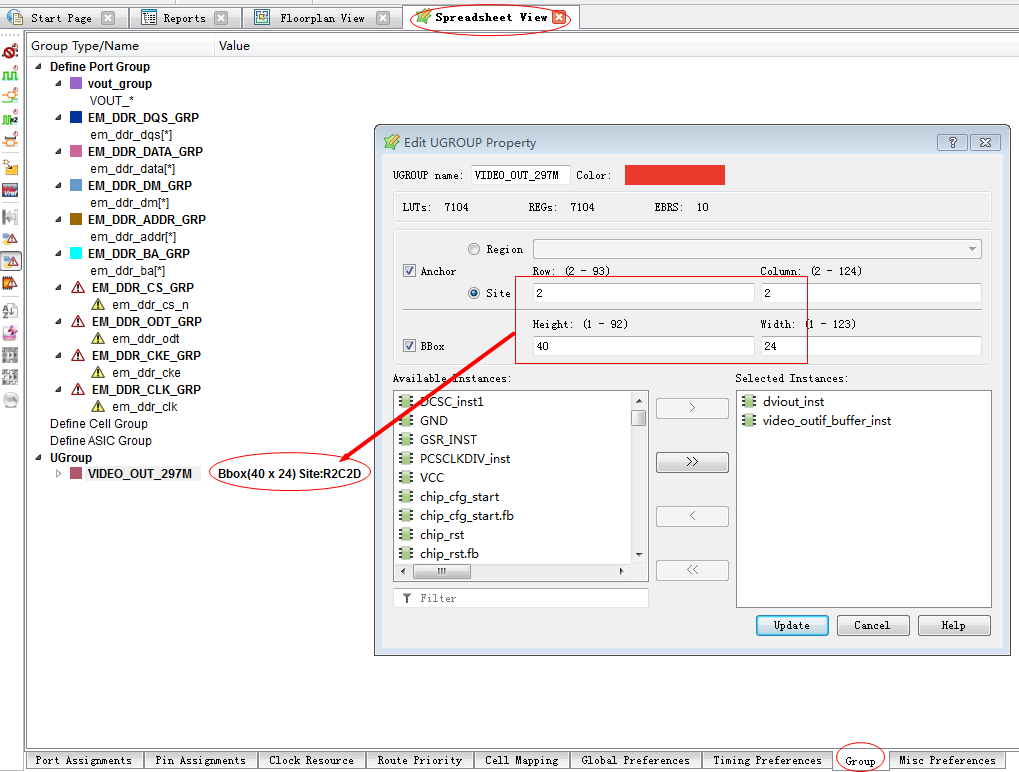

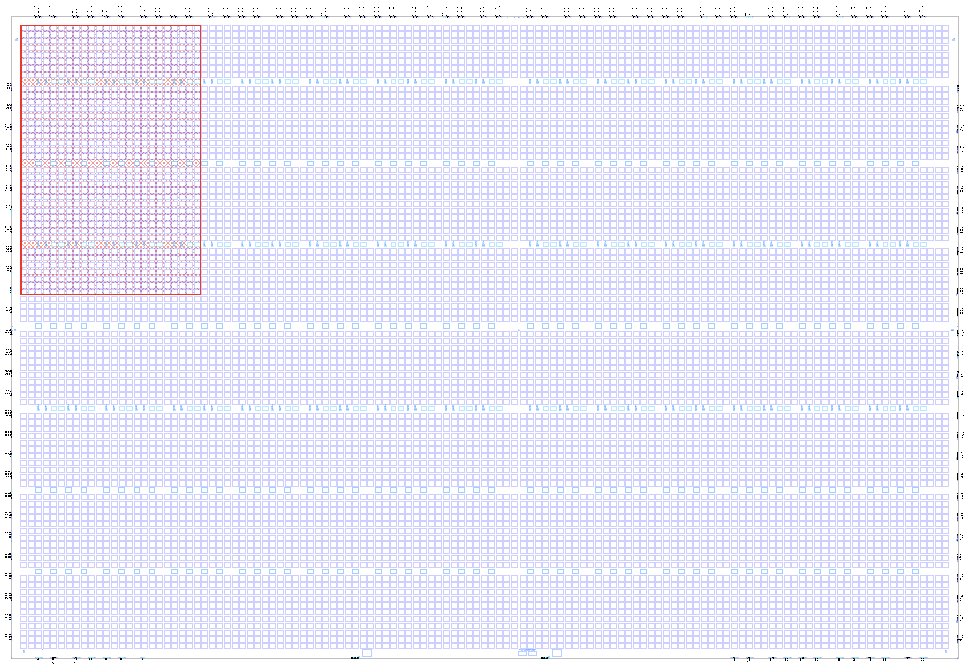

《Lattice_Diamond_3_10_3_Help.pdf》第496页,给出UGROUP的具体用法,参考该方法进行位置约束如下:

297M高速设计几点原则:

1、FIFO或RAM要设置输出寄存(Lattice默认打1拍,寄存后,相当于打2拍输出)

2、涉及大位宽比较时,使用减法器替代加法器,就只用和0进行比较。

3、后端约束使用位置约束(Lattice使用UGROUP)

4、计数器不能大于11bit,大于的就只能拆分。

5、一些相对固定的变量,比如分辨率res_mode,显示模式disp_mode,可以在后端约束里,用BLOCK将其进行时序忽略。

=======================

by NicoWei

2019-3-16 22:20:08

=======================

浙公网安备 33010602011771号

浙公网安备 33010602011771号