CPU缓存

CPU缓存结构

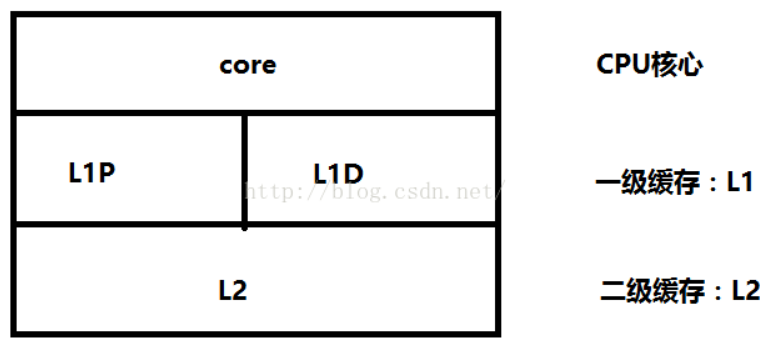

单核CPU

在单核CPU结构中,为了缓解CPU指令流水中cycle冲突,L1分成了指令(L1P)和数据(L1D)两部分,而L2则是指令和数据共存。

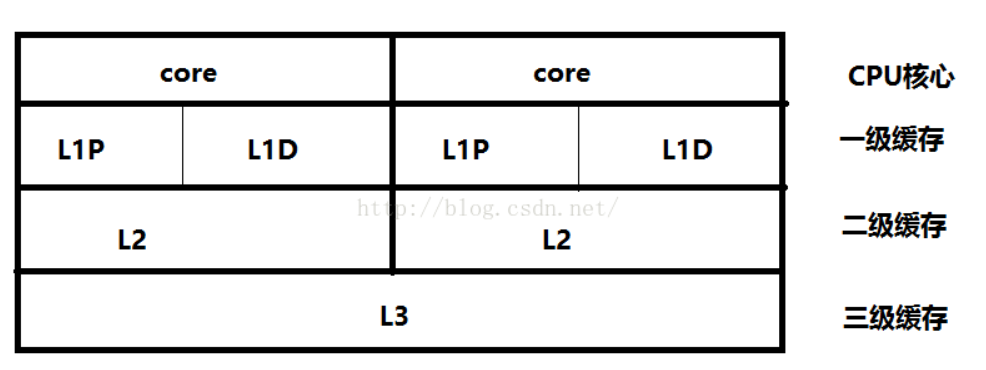

多核CPU

多核CPU的结构与单核相似,但是多了所有CPU共享的L3三级缓存。在多核CPU的结构中,L1和L2是CPU私有的,L3则是所有CPU核心共享的。

缓存一致性

在多核CPU中,内存中的数据会在多个核心中存在数据副本,某一个核心发生修改操作,就产生了数据不一致的问题。而一致性协议正是用于保证多个CPU cache之间缓存共享数据的一致。

参考文章:

https://blog.csdn.net/reliveit/article/details/50450136

伪共享(false-sharing)

参考文章:

https://www.cnblogs.com/cyfonly/p/5800758.html

https://coolshell.cn/articles/10249.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号