5.8举例仿真

对5.8及5章题目的仿真

1.四选一多路选择器

四选一多路选择器的执行模块:

/* 下面是一个四选一多路选择器的单元模块。 */ module mux4_to_1(out,i0,i1,i2,i3,s1,s0); output out; input i0,i1,i2,i3; input s1,s0; reg out; always @(s1 or s0 or i0 or i1 or i2 or i3) begin case({s1,s0}) 2'b00:out=i0; 2'b01:out=i1; 2'b10:out=i2; 2'b11:out=i3; default:out=1'bx; endcase end endmodule

四选一多路选择器的测试单元模块:

/* 对study_1.v的测试模块 */ `include "study_1.v" module study_1_tb; reg ts1,ts0,ti0,ti1,ti2,ti3; reg clock; wire tout; initial begin ts1=0; ts0=0; ti0=0; ti1=0; ti2=0; ti3=0; clock=0; end always #25 clock=~clock; always @(posedge clock) begin #1 ti0=($random)%2; #1 ti1=($random)%2; #1 ti2=($random)%2; #1 ti3=($random)%2; end always # 50 begin {ts1,ts0}=2'b00; #50 {ts1,ts0}=2'b01; #100 {ts1,ts0}=2'b10; #150 {ts1,ts0}=2'b11; end mux4_to_1 m (.out(tout),.i0(ti0),.i1(ti1),.i2(ti2),.i3(ti3),.s1(ts1),.s0(ts0)); endmodule

注意:1)在初始化的时候,不能写成 ts0=1'b0;只能写成ts0=0;(?) 2)不能写成ts0=ts1=ti0=0;只能写成ts0=0;ts1=0;ti0=0;

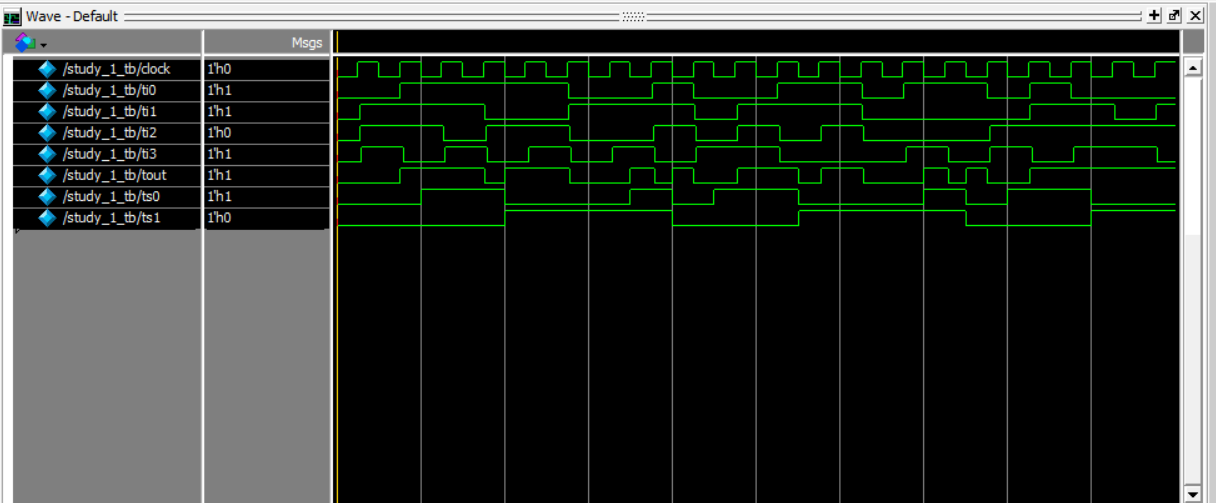

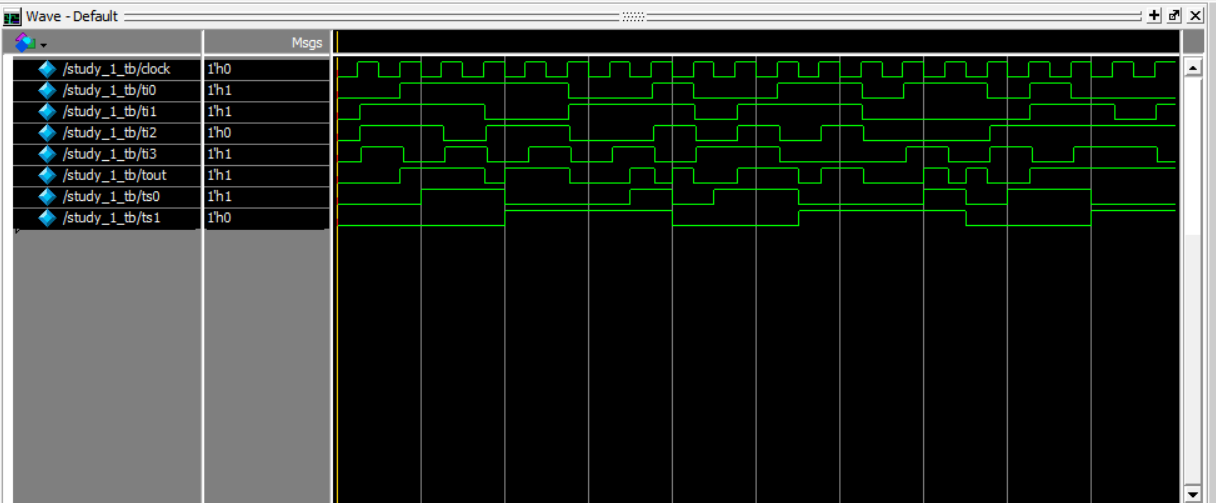

仿真结果:

不过但我想按照书上P60页说的“forever与always语句不同之处在于不能独立写在程序中,而必须写在initial块中。”的意思,将控制信号{ts1,ts0}用forever写在initial块中,而不是用always生成;代码如下:

/* 对study_1.v的测试模块 */ `include "study_1.v" module study_1_tb; reg ts1,ts0,ti0,ti1,ti2,ti3; reg clock; wire tout; initial begin forever begin {ts1,ts0}=2'b00; #25 {ts1,ts0}=2'b01; #25 {ts1,ts0}=2'b10; #25 {ts1,ts0}=2'b11; end // begin // ts1=0; // ts0=0; // ti0=0; // ti1=0; // ti2=0; // ti3=0; clock=0; end always #25 clock=~clock; always @(posedge clock) begin // #1 ts1=($random)%2; // #1 ts0=($random)%2; #1 ti0=($random)%2; #1 ti1=($random)%2; #1 ti2=($random)%2; #1 ti3=($random)%2; end // always # 50 begin // {ts1,ts0}=2'b00; // #50 {ts1,ts0}=2'b01; // #100 {ts1,ts0}=2'b10; // #150 {ts1,ts0}=2'b11; // end mux4_to_1 m (.out(tout),.i0(ti0),.i1(ti1),.i2(ti2),.i3(ti3),.s1(ts1),.s0(ts0)); endmodule

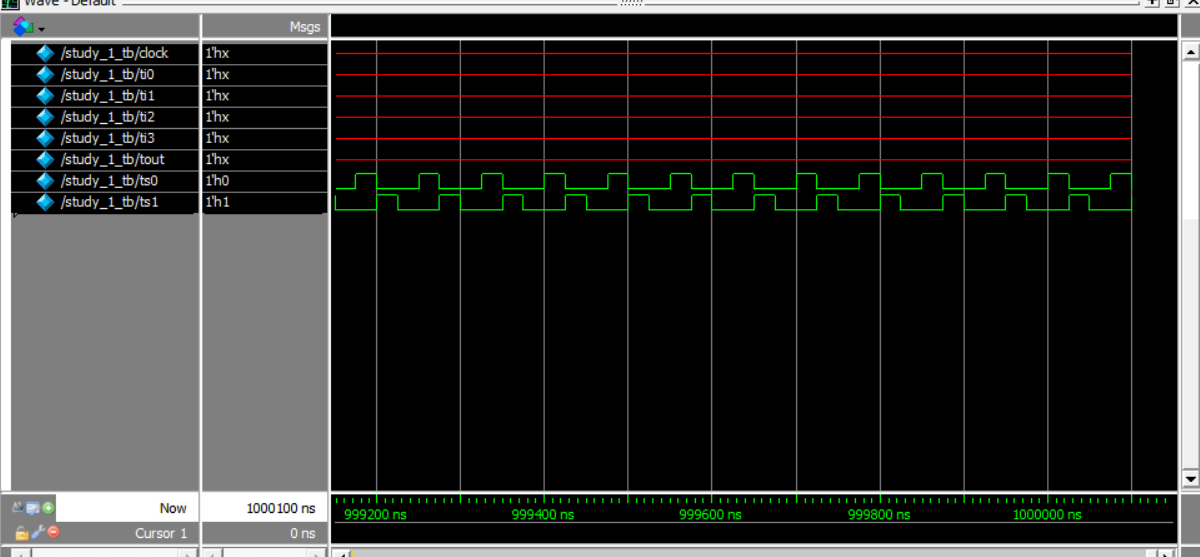

当用上面的代码进行仿真时;

原因:在initial中,forever下面的clock初始化一直没有完成。那么clock一直是x,那么后面对clock的反转,上升沿的判断都因为clock是不定值而无法正确实现。

解决方法:initial下的第一个大的begin-end换成fork-join就行了。

最后的输出时序貌似有问题。不过现在不考虑这些问题。。。。。。

四位计数器

1 // 四位二进制计数器 功能模块 2 module counter(Q,clock,clear); 3 output [3:0] Q; 4 input clock,clear; 5 reg [3:0] Q; 6 7 always @(posedge clear or negedge clock) 8 begin 9 if (clear) 10 Q<=4'b0; 11 else 12 Q<=Q+1; 13 end 14 endmodule 15 16 17 // 四位二进制计数器 测试模块 18 module countertb; 19 reg clock_tb,clear_tb; 20 wire [3:0] Q_tb; 21 22 initial 23 begin 24 clock_tb=0; 25 clear_tb=1; 26 end 27 always #25 clock_tb=~clock_tb; 28 always #1000 clear_tb=~clear_tb; 29 counter c (Q_tb,clock_tb,clear_tb); 30 endmodule

第25行要初始化clear_tb=1;不然前面会产生输出的不定态。

浙公网安备 33010602011771号

浙公网安备 33010602011771号