阻塞赋值-非阻塞赋值(LUT,FDC,BUF...)

一.看RTL级综合网络

1.1 FDC FDPE FDRE FDSE均是XILINX FPGA片上资源中四种不同的触发器,具体功能可直接百度

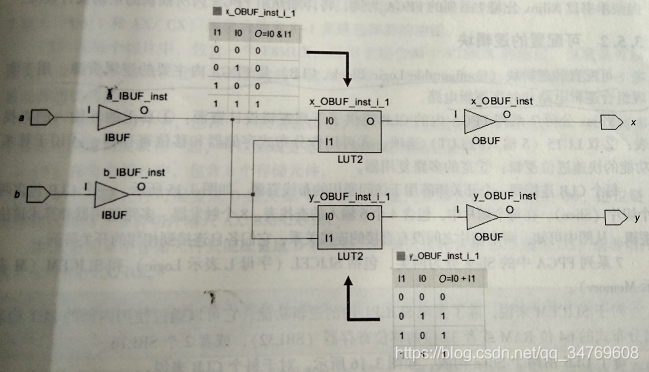

1.2 LUT是实现组合逻辑功能的一张真值表,根据输入值直接推输出,它可以取代复杂的组合逻辑电路,不再和复杂度有关,而且它的延迟是固定的。

1.3BUF是缓冲器。IBUF是输入缓冲器,OBUF是输出缓冲器,OBUFT三态输出缓冲门。

二.对比

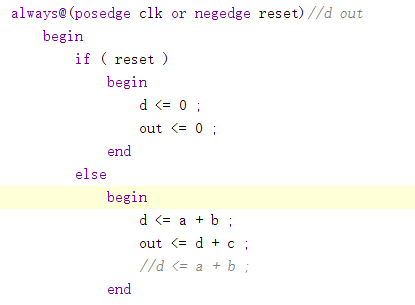

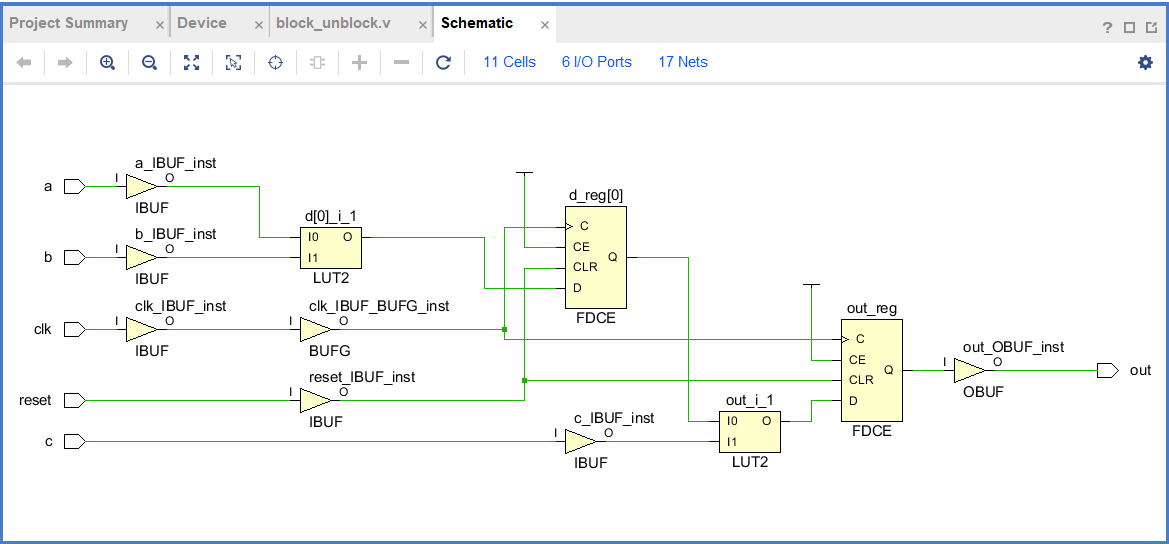

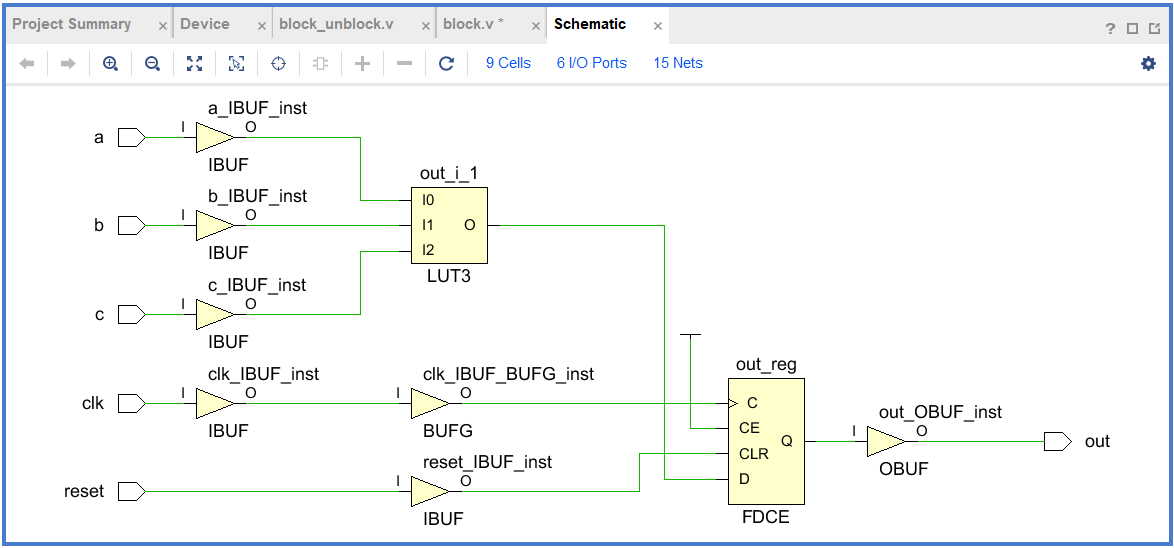

1.非阻塞赋值

两个非阻塞赋值语句,出现了两个触发器,每一个clk上升沿到来时,两个触发器同时触发,d和out同时变化。

调换顺序之后,综合出来的RTL级网络相同,说明非阻塞赋值与语句顺序无关,是并行执行。

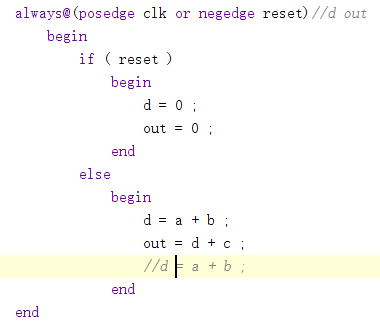

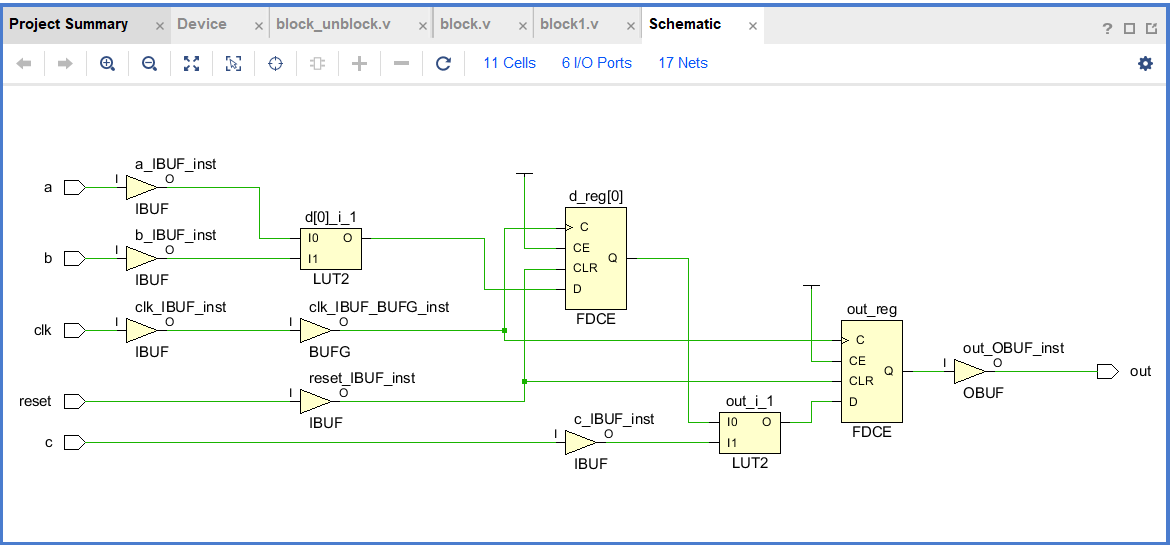

2.阻塞赋值

区别于非阻塞,这里d没有出现,只有一个触发器,也就是说每一个clk上升沿到来时,只有out变化。

这里就变成了是out = a+ b + c,即把两个语句串行执行了,取最终结果。

接下来换个顺序看看。

可以看到,这时出现了两个触发器,因为d的赋值语句在out后,按照顺序执行时不能直接连起来变成一条语句,说明阻塞赋值跟语句顺序有关。

综上所述,阻塞赋值与语句的顺序有关,顺序不同,综合出来的电路也不同,触发器的个数各不相同,所以阻塞赋值一般用于组合逻辑电路,在时序逻辑电路(alwasy@ clk)中虽然能用,能编译,但是不好控制,不知道综合出来的电路网络是怎样的。也可以看出,阻塞赋值为串行执行。

而非阻塞赋值与语句的顺序无关,为并行执行,电路是固定的,所以在时序电路中一般用非阻塞赋值语句。

三.

可以在赋值语句中加延时,如:out <= #10 a+ b

即让out 延时10个单位时间后再输出 out = a + b;

此法类似于模仿门电路的延时,易于观察波形。

浙公网安备 33010602011771号

浙公网安备 33010602011771号