参数化设计(多次调用同一子模块,critical warning,引脚constraint sources)

1.设计定义:4个led灯以不同的频率各自闪烁。

2.设计输入:时钟信号,复位信号,led多位输出。

思路:没有要求流水的效果,所以不需要叠加counter达到某一特定值来位移。只需要让每个灯的闪烁周期不同即可。所以可以直接调用led闪烁模块,设置不同的周期参数来实现。

`timescale 1ns/1ns

module led_flash_dif(

clk,

reset,

led

);

input clk;

input reset;

output wire [3:0]led;

led_flash led_flash_1(

.clk(clk),

.reset(reset),

.led(led[0])

);

defparam led_flash_1.number = 99999;

led_flash led_flash_2(

.clk(clk),

.reset(reset),

.led(led[1])

);

defparam led_flash_2.number = 49999;

led_flash led_flash_3(

.clk(clk),

.reset(reset),

.led(led[2])

);

defparam led_flash_3.number = 39999;

led_flash led_flash_4(

.clk(clk),

.reset(reset),

.led(led[3])

);

defparam led_flash_4.number = 29999;

endmodule

3.综合

4.综合后仿真,功能验证

`timescale 1ns/1ns

module led_flash_dif_tb();

reg s_clk;

reg s_reset;

wire [3:0]s_led;

led_flash_dif led_flash_dif_stim(

.clk(s_clk),

.reset(s_reset),

.led(s_led)

);

initial s_clk = 1;

always #10 s_clk = !s_clk;

initial begin

s_reset = 1'd1;

#100;

s_reset = 1'd0;

#20001000;

$stop;

end

endmodule

5.布局布线

6.时序仿真,性能分析

7.板级调试,I/O口连接

注意

1.在一个模块中多次例化同一子模块时,要用不同的例化名称区分开来,而且每次例化的输出也最好用不同的输出位,输出多个端口。如果一直是同个输出端口,虽然不会报错,但一般情况下达不到效果。(模块例化子模块可以用defparam)

2.引脚文件为constraint sources,加入之后要set as target source 才能生效。

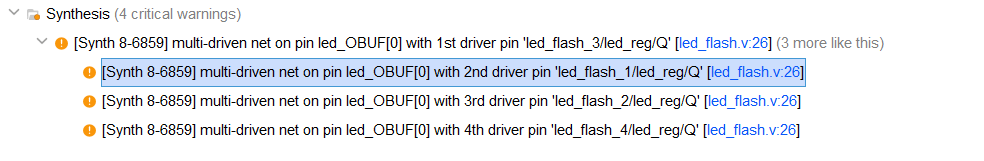

3.critical warning为比较重要的警告信息,应该看一看,如下:提示了多个模块用同个输出端口。

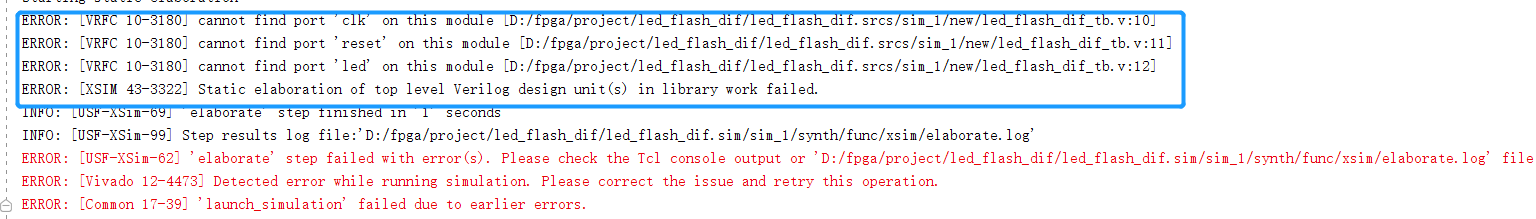

4.遇到了:cannot find port '' in this module 的报错,后面又自己好了,没找到原因。

浙公网安备 33010602011771号

浙公网安备 33010602011771号