7.8.4 Advanced Error Reporting Extended Capability (AER)

The PCI Express Advanced Error Reporting (AER) Capability is an optional Extended Capability that may be implemented by PCI Express device Functions supporting advanced error control and reporting. The Advanced Error Reporting Extended Capability structure definition has additional interpretation for Root Ports and Root Complex Event Collectors (RCECs); software must interpret the Device/Port Type field in the PCI Express Capabilities register to determine the availability of additional registers for RPs and RCECs. RPs or RCECs that support RC ECS Handling can distinguish ERR_COR Messages targeting SFW vs the OS and handle them appropriately.

In an SR-IOV Device, if AER is not implemented in a PF, it must not be implemented in its associated VFs. If AER is implemented in the PF, it is optional in its VFs.

In an SR-IOV Device, the Header Log space for a PF is independent of any for its associated VFs and must be implemented with dedicated storage space. VFs that implement AER may share Header Log space among VFs associated with a single PF. Shared Header Log space must have storage for at least one header. See § Section 6.2.4.2.1 for further details.

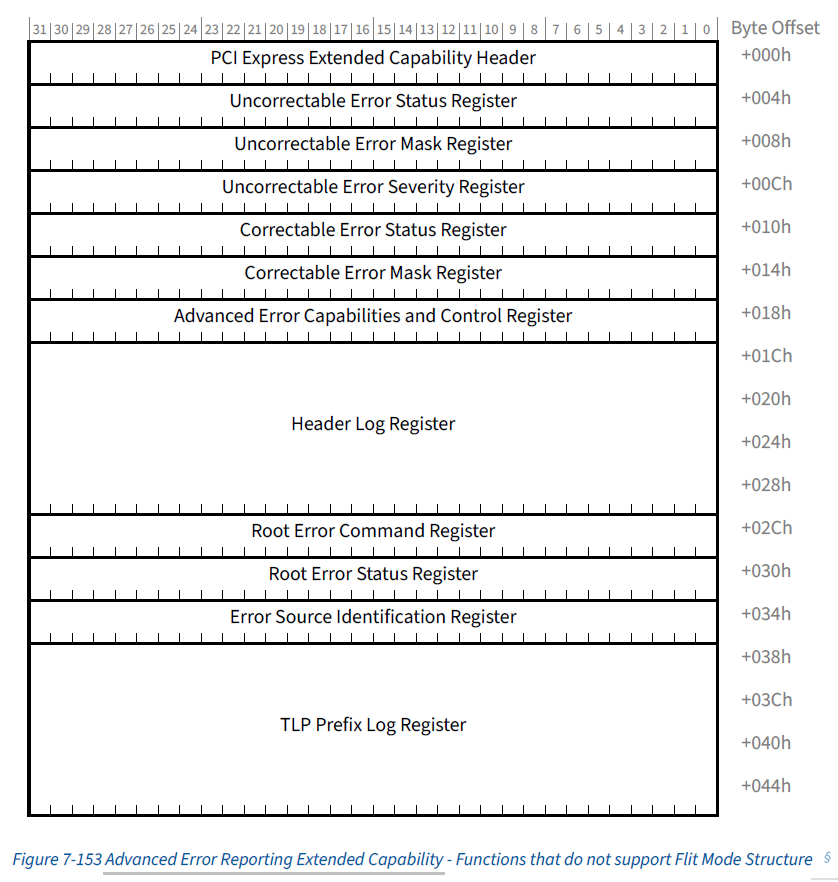

§ Figure 7-153 and § Figure 7-154 show the PCI Express Advanced Error Reporting Extended Capability structure. In § Figure 7-154, the last 6 DW are optional. Implementations are permitted to implement between 0 and 6 additional DW of Header Log (see Header Log Size for details).

Note that if an error reporting bit field is marked as optional in the error registers, the bits must be implemented or not implemented as a group across the Status, Mask and Severity registers. In other words, a Function is required to implement the same error bit fields in corresponding Status, Mask and Severity registers. Bits corresponding to bit fields that are not implemented must be hardwired to 0, unless otherwise specified.

posted on 2026-01-30 18:45 ENGINEER-F 阅读(8) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号