DMA

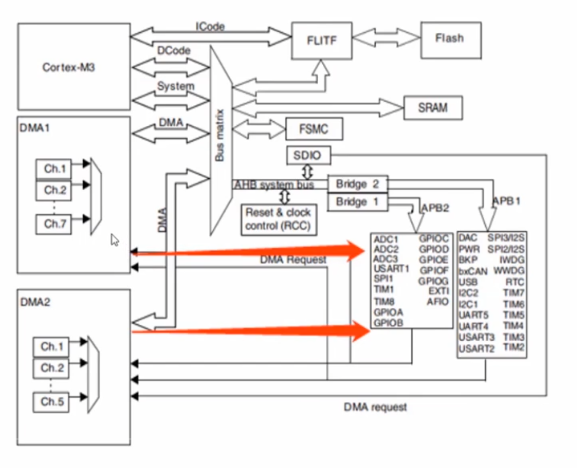

Direct Memory Access 直接内存访问

0

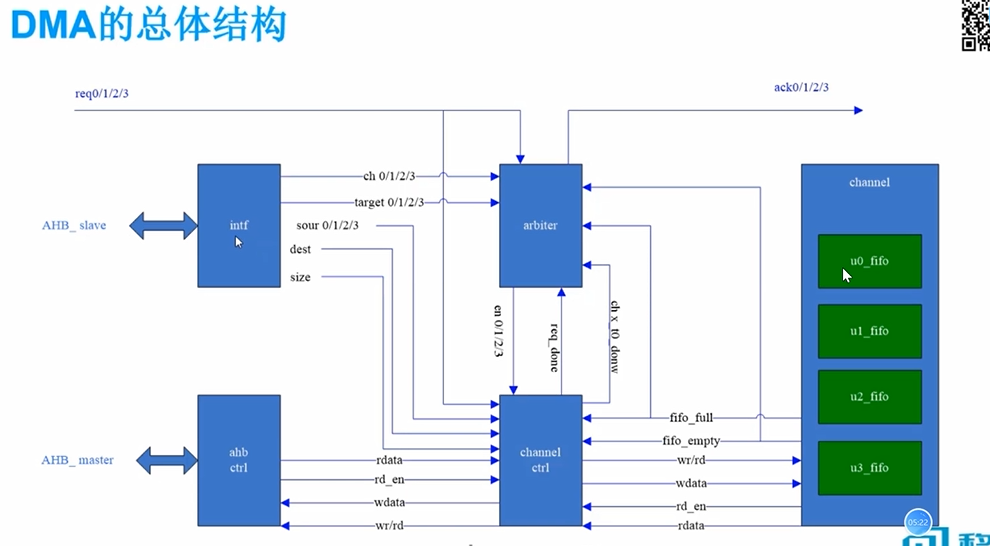

是CPU的slave,是外设和内存的master,

存储器之间通过FIFO进行数据搬移

1.1 工作模式

1)正常传输模式:配置后只传输一次,需要重新配置

2)循环模式:一直传送除非关闭,适于数据流

3)双缓冲模式:当第一片存储器传输完成自动切换到第二片并不断切换

一般用于外设和存储器之间,信号的编解码输出、视频、音频连续输出

1.2 流控制

控制数据流的传输

软件流:通过软件配置来结束传输

外设流:需要外设产生特定的结束信号,一般外设不具有流能力

DMA流控制:传输固定数量,可以控制

2.1 设计规格

HCLK、HRESETn

- 1个32位AHB Master interface 读写存储器和外设

OUT: HSEL、HADDR、HSIZE、HTRANS、HWRITE、HWDATA、HREADY

IN: HRDATA、HREADYOUT、HRESP - 1个32位AHB Slave interface 作为CPU的外设,供CPU配置DMA

如HSEL_SLV,输入输出与master相反 - 4个独立可配置的通道,固定优先级仲裁

- 支持外设与存储器之间的传输

- 可编程的数据最大为1024

AHB只支持基本的单次传输

req[3:0] 外设输入的dma_req信号

ack[3:0] 输出给外设的dma_ack信号

2.2 寄存器功能

寄存器,模块是接在AHB的slave模块,挂接在AHB总线上,接受AHB的配置,并解析4个通道的配置信息供其他模块使用

12个寄存器,每个通道三个寄存器,配置后输出

-

ch_0_ctrl 偏移地址0X0

0: ch_0_en 通道0使能

4: ch_0_target 传输方向,0为memory到外设

17~8:ch_0_size 传输大小 -

ch_0_sour 0X4-32位源地址

-

ch_0_dest 0X8-32位目的地址

2.3 总线接口

- 将内部的读写信号、地址、数据转换成AHB的时序接口

总线接口是AHB的master接口

channel_ctrl发出读写操作、由ahb_ctrl转换成AHB时序

wr为高表示向AHB的addr写,rd则读

2.4 仲裁器

根据输入的req信号仲裁当前优先级最高的通道进行操作

固定优先级算法进行仲裁req0>1>2>3,回ack握手信号

IN: clk、rst、req_0123、ch_0123_en、target_0123、req_done表示当前req处理完、ch_0123_t0_done 表示t0方向传输结束、fifo_0123_empty、fifo_0123_full

OUT: ack_0123、en_0123工作信号、

2.5 channel控制器

通道控制器含三个模块,根据仲裁结果管理通道

接收仲裁后的使能信号,发起对fifo操作,发起对ahb_ctrl模块的读写

dmac_fifo同步fifo存储数据、

dmac_channel例化4个通道的fifo、

dmac_channel_ctrl对通道进行传输控制

3.1 DMA顶层模块

声明输入输出端口,例化内部所有模块,没有其他逻辑

信号:HCLK、HRESETn AHB_Master AHB_Slave信号

3.2 AHB_ctrl模块

对外部总线进行数据读写

将内部的写信号、地址、数据转换成AHB时序

IN: wr写使能,rd读使能,addr 32位写地址,wdata 32位写数据wr高有效,

OUT: rd_en读标志信号,rdata 32位读数据rd_en高有效

3.3 interface模块

内部寄存器读写,控制信号的输出,ahb_slave interface

access高表示有读写,write写信号在数据周期有效,read读信号在地址周期有效

3.4 arbiter仲裁模块

IN: req_x ch_x_en target_x ch_x_to_done fifo_x_empty fifo_x_full req_done

OUT: en_x ack_x

状态机的转换-由输入的req确定输出通道使能

DMA回应ack信号

3.5 channel模块

例化四个同步fifo

每个fifo有单独的读写控制信号,空满判断信号

3.6 channel ctrl

T0 存储器到外设

T1 外设到存储器

fifo的读写操作

总线的读写操作

浙公网安备 33010602011771号

浙公网安备 33010602011771号