verilog 硬件描述语言

第一章 绪论

verilog--数字电路设计技术--ASIC/SOC芯片设计--协议pcie SATA USB--系统知识(个人计算机,芯片组,网络连接,嵌入式系统,硬件和软件的互操作)

第二章 寄存器传输语言 RTL(Register Transfer Language)

第三章 可综合的verilog--用于电路设计

3.3 verilog的结构

块(block)--子块(sub-block)--模块(module)

触发器:D,RS,JK,

3.7 组合逻辑 always变量为reg类型,assign变量为wire类型3.7 组合逻辑 always变量为reg类型,assign变量为wire类型

3.7.1 always块语句

- 使用(*)代表敏感信号,包括reset_center和center1.always块语句 使用(*)代表敏感信号,有reset_center和center

- 阻塞赋值符号“=”

- 内部第一句描述了cnter_nxt的默认值(大多数情况下cnter_nxt的取值),敏感信号变化时always块执行并重新计算cnter_nxt的值

- 开始为变量分配默认值,确保不会生成锁存器,之后用if-else语句获得cnter_nxt值

- 如果有一个以上语句需要在一定条件下执行放在begin-end结构中

- 只有一条语句就不需要begin-end

3.7.2 case和if-else语句

- case语句只能有1比特为1

3.8 操作符

- 一个是按位,两个就是逻辑

&&逻辑与 &按位与

||或

!逻辑非 ~按位非 ^按位异或 ~^按位异或非

缩位 &与 |或 ^异或 ~&与非 ~|或非 ~^异或非

==相等 !=不等于 > >= < <= + - * / {}并位 <<向左位移 >> ?条件运算符 %求模 **指数 - 执行顺序 尽量使用括号,括号优先执行

- 注释 //单行注释 或者 多行/**/

3.9 可重用模块化设计

- 可重用模块化设计:同一个电路单元可在不同的芯片中使用,常用的包括parameter,function,generate,`ifdef等

parameter使用方法:参数在使用前需要被提前定义,可以在模块中被定义也可以在include头文件中定义,如chiptop_parameter.vh,模块例化时可以将不同值传递到模块内部。FIFO(First in first out,先入先出) - 参数文件扩展名是.vh,包含芯片的全局参数,顶层参数文件中建议采用较长参数名。不同层次上有多个不同参数,需要确定参数是否唯一。

- Verilog函数 用来生成可综合的组合逻辑 函数有多个输入信号和一个输出信号,综合后得到组合逻辑,其内部不能出现时间控制相关语句,如wait,@或#

- generate结构 编译在综合和仿真之前,

- `ifdef结构用于模块设计 先创建一个chiptop_defines.vh的文件,将定义的字符串放在文件里面,使用include插入字符串语句之前。 ifdef-else if-else-endif,mux语句综合后会出现多个分支,ifdef只有一个

3.9.5 数组

定义一个深度128,位宽32的存储器

reg [31:0] memory[0:127];

Verilog supports multi-dimensional structures.

wire [7:0] ascii_char,

wire [7:0] abc [0:31] [0:15];

assign ascii_char=abc[10][2][7:0];

第四章 用于验证的Verilog的语法

4.1 测试平台 testbench

- DUT(Design Under Test,被测电路),Verilog中还有一些语法结构但不可综合。

4.2 initial语句

- 初始化变量,触 一句开始执行到最后一句,此后不再执行。

4.3 系统任务

- 电路仿真时,遇到$finish完成仿真并退出,一般放在testbench的顶层文件中,如果testbench_top.v是顶层仿真文件那么应在仿真结束时刻。

- $stop 停止仿真但不退出,提供一个命令提示符,在后面输入“.”继续进行

- $display 不可综合不能直接放在DUT的RTL代码中,将$display语句嵌入translate on与translate off之间,建议放在testbench中通过“.”指出信号在DUT中路径,显示需要观察的信号数值

- $monitor与display相似 仅当信号数值变化才显示

- $time返回当前仿真时间,tb中用timescale指出仿真时间单位(通常为1ns),当前时间是一个64位整数乘以timescale中的单位后取整得到的整数,不包括小数。realtime返回实数包括小数

- $random 返回一个32位带符号的随机整数。放入{}内可以得到非负整数。random(seed)中的seed是一个整数用于指出随机数的取值范围。被用于随机测试中。还可以描述不确定行为,比较器中输入值小于参考值输出0,大于输出1,相等都有可能。

- save("file name") 保存当前仿真信息

- readmemh从一个文本中读取数据,tb产生测试激励的一种方式先将要使用的数据存在文件中,仿真时使用readmemh读取并产生激励波形。

- writememh 将数据写入文本,好分析仿真过程。

- fopen("file name");打开文件 fclose(file1);关闭文件

4.4 任务

任务和函数很相似。可以将一段代码定义为一个任务,然后在不同地方多次调用该任务。任务可以自定义自己的输入输出端口,可以定时控制,如@posedge clk、non-zero timings和#10等时间控制语句。任务按顺序执行,仿真器会等到定时条件满足才执行后续的语句。如当遇到@posedge clk时,程序只在出现时钟上升沿时才执行,任务更多用于tb而不是DUT

4.5 存储器建模

通过定义二维寄存器数组的方式定义存储器,SRAM(Static Random Access Memory,静态随机存取存储器),定义一个深度为1k,位宽为8字节的存储器:

reg [7:0] OneKByte [1023:0];

wire [7:0] byte_9;

4.6 while循环

- while建议加入定时控制语句如@posedge clk或#5,以避免形成定时环路。

- for循环语句可用于tb或可综合的RTL代码中

- repeat(5)

- force将一个固定值(1,0)强制赋予一个变量。release执行前无论变量怎么被驱动,值都不变,执行后由具体驱动决定

- fork/join 是并行的,先执行内部再后面

4.7 一个简单的tb文件

//生成clk_tb

initial begin

clk_tb=1'b0;

forever begin

#CLKTB_HALF_PERIOD clk_tb=~clk_tb;

end

end

//生成resetb

resetb =1'b0;

#100 resetb=1'b1;

第五章 数字电路设计

5.1 组合逻辑门

组合逻辑门和触发器的存储元件组成数字电路

5.1.1 逻辑 1 和逻辑 0 模拟电压,低于某个门限的电压值代表0,高于一定门限的代表1,各自门限之差称为噪声容限。

5.1.2 真值表

5.1.3 晶体管 n型和p型

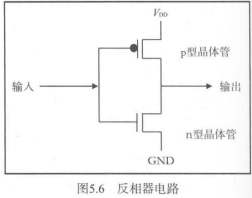

5.1.4 反相器

一个输入一个输出端,由一个p型和一个n型晶体管串联而成

对于CMOS逻辑门来说,只有当逻辑值发生变化时才有电流流过晶体管。

5.1.5

- 与门,一般最多五个输入,可以级联用 O=AB

- 或门 0=A+B

- 与非门 O=(AB)'

- 或非门 O=(A+B)'

- 异或XOR 不同输出1 异或非XNOR 相同输出1

- 缓冲门,输入输出相同,驱动多个负载

- 复用器 MUX 两个数据输入端,一个选择输入端以及一个输出端,sel=1选择一端输出

- 通用逻辑门 NAND与非门 NOR或非门

- 复杂门电路 由与或非电路组成

- 噪声容限 3.5v-5v为逻辑1,0-1.5v为逻辑0

低电平噪声容限 输入端逻辑0的最大电压 上一级输出端的低电平最大电压 之间差值

高电平噪声容限 输入端高电平最小电压 上一级输出端高电平最小电压 - 扇入 一个逻辑门正常工作时输入端的数量

- 扇出是在不降低输出电平的情况下逻辑门能够驱动的负载的数量

5.2 德摩根定理

- (A·B)'=A'+B'

- (A+B)'=A'·B'

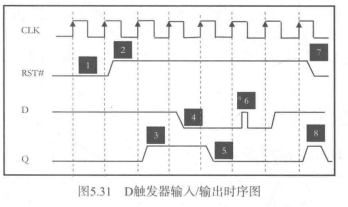

5.3 D触发器

单比特存储元件 数据、时钟、RST、Q、Q'

- 每一个时钟上升沿,输出Q将输入D的值锁存,直到下一个时钟上升沿出现才继续锁存当前D的值

- 时序图

![image]()

- 建立时间 上升沿之前D需要保持稳定的最短时间

- 保持时间 上升沿之后D不允许改变的时间

- 亚稳态 D发生变化时 此后的几乎一个时钟周期内 输出不确定 在下一个上升沿之前稳定为0或1

- 两个D触发器级联构成的同步器

- 信号同步规则 跨时钟域的信号必须直接来自源时钟域的寄存器输出,使用专用触发器,在一个点上进行跨时钟域信号同步

- 时序 常用的接口(PCIE SATA USB)时钟频率不变,确保延迟不超过一个时钟周期;另一种尽可能降低门延迟,最大限度提高系统频率 如处理器

Tctop+Tgate(max)=Tclk-Tskew-Tsetup - 事件/边沿检测 检测上升沿下降沿

同步上升/下降沿检测、异步输入上升沿检测

5.8 数值系统

- 十进制D 二进制B 八进制 十六进制H

- 行波进位加法器、超前进位加法器、累加器

- 乘一个常数 通过向左移位相加或相减

- 除一个2的整数次幂,向右移位

- 加法/减法计数器

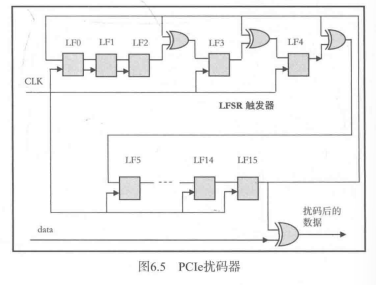

- LFSR计数器--线性反馈移位寄存器,由一组级联的移位寄存器加上异或(非)门的反馈构成

第六章 数字设计基础模块

6.1 LFSR

用于产生可重复的伪随机序列PRBS,最后一个触发器的输出就是一个周期性重复的伪随机序列,n个触发器可以产生周期为2的n次幂-1的序列

- 斐波那契LFSR为多到一型,多个触发器异或驱动一个触发器的输入

- 伽罗瓦LFSR为一到多型,一个触发器异或驱动多个触发器的输入

- 用作计数器速度快,消耗逻辑门少;扰码器产生重复的比特图案,密码系统,BIST,快速以太网及吉比特以太网

6.2 扰码与解码

发送数据前随机扰乱,接收电路采用相同的算法恢复数据

LFSR产生伪随机序列和串行输入的数据进行异或

周期长度取决于触发器级数和多项式

接收电路有一个一样的伪随机序列产生器,其与接收数据进行异或就能恢复数据 A^B=C 则C^B=A

- 扰码作用 可以使重复的数据频谱被展宽,例如10101010会产生较强的EMI电磁干扰,进行扰码后EMI大大减弱

还可以减少并行线路中的串扰,可以使功率谱分布更为平滑均匀,降低高频串扰 - 串行扰码器 一个时钟周期只有1比特数据到达

- 并行扰码器 每个时钟周期内产生八位随机数,扰码器也产生八位

- 设计要点 扰码器初始化,PCIE中使用COM字符;扰码器暂停,PCIE数据流中会添加或删除SKIP字符,扰码器去使能,不断更新

PCIE扰码器是一个16位LFSR

G(x)=x16+x5+x4+x3+1 有16个LFSR触发器,初始化为16'hFFFF,SKP字符可暂停

6.3 纠错与检错

检错

- 额外添加一些数据与原始数据一起传输,称为冗余比特,

- 奇偶校验 可以发现奇数个比特错误,找不到错误位置,不能纠错

- CRC校验是数据包中常用的检错机制

纠错

浙公网安备 33010602011771号

浙公网安备 33010602011771号