MSP430学习笔记3 时钟

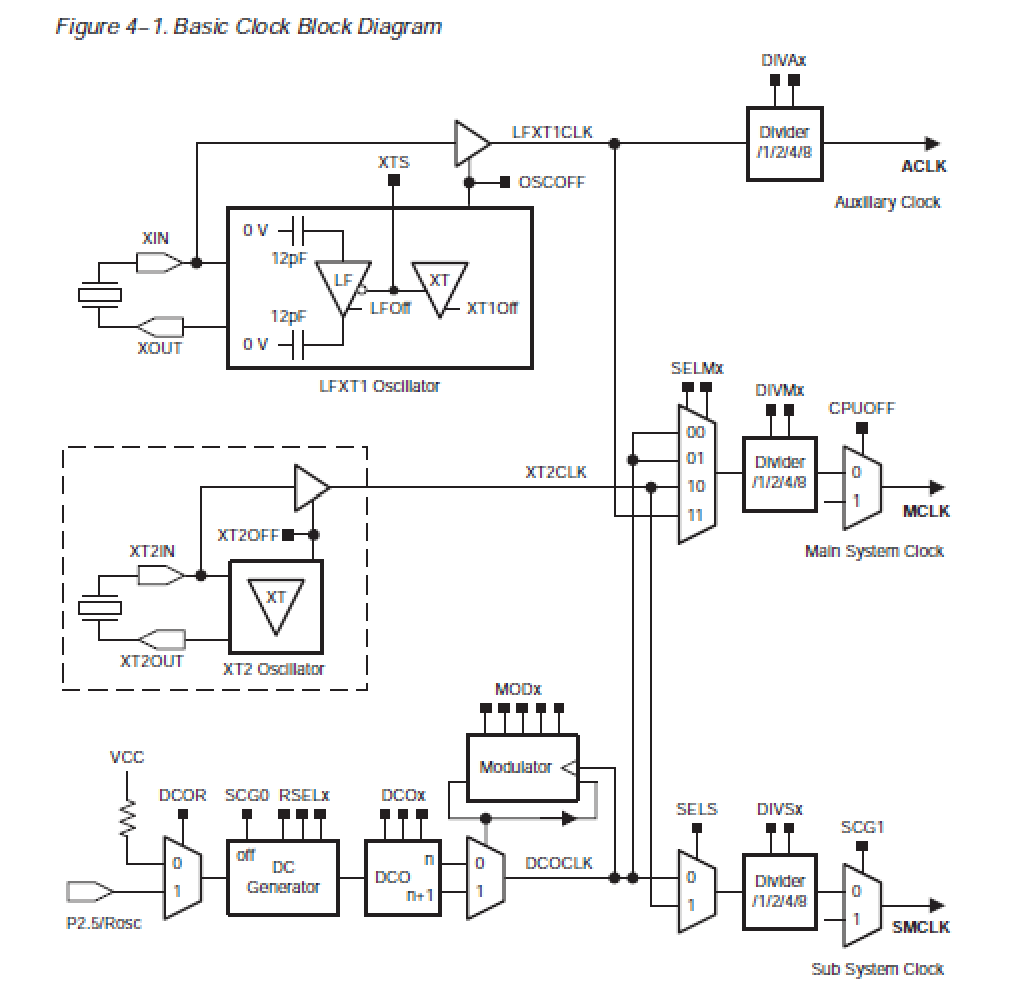

3个时钟输入源

- LFXT1CLK 低速晶体振荡器

一般外接32.768kHz的手表晶振

也可以通过外接450kHz~8MHz的高速晶体振荡器或谐振器工作在高频模式。 - XT2CLK 高速晶体振荡器

可选择的高频振荡器,通常外接8MHz的振荡器。 - DCOCLK 数字控制振荡器

可通过编程设定频率。

低速晶体振荡器专门为辅助系统时钟(ACLK)提供时钟源。

高速晶体振荡器用来满足大量的数据计算,快速的响应。

主系统时钟有三种来源

时钟系统十分灵活,比如MCLK是供给CPU和片内一些高速外设,系统需要处理大量数据,MCLK选为高速晶体振荡器不分频。如果是以低功耗为主,MCLK选为低速晶体振荡器再经过分频,降低CPU工作频率。

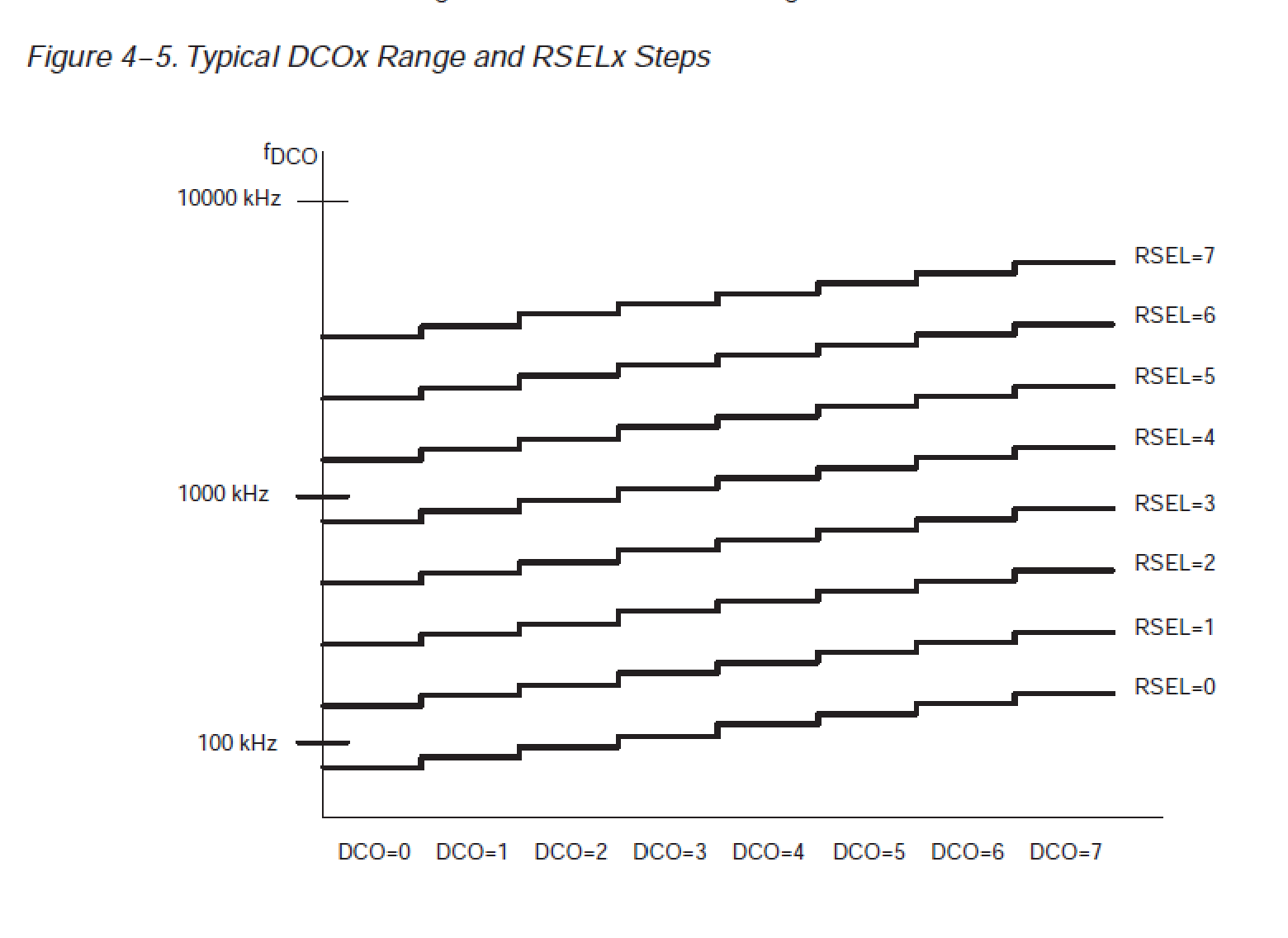

DCO

DCO的频率的调节图(DCOx和RSELx决定DCO频率)

基础时钟模块寄存器

DCOCTL、BCSCTL1、BCSCTL2、IE1、IFG1

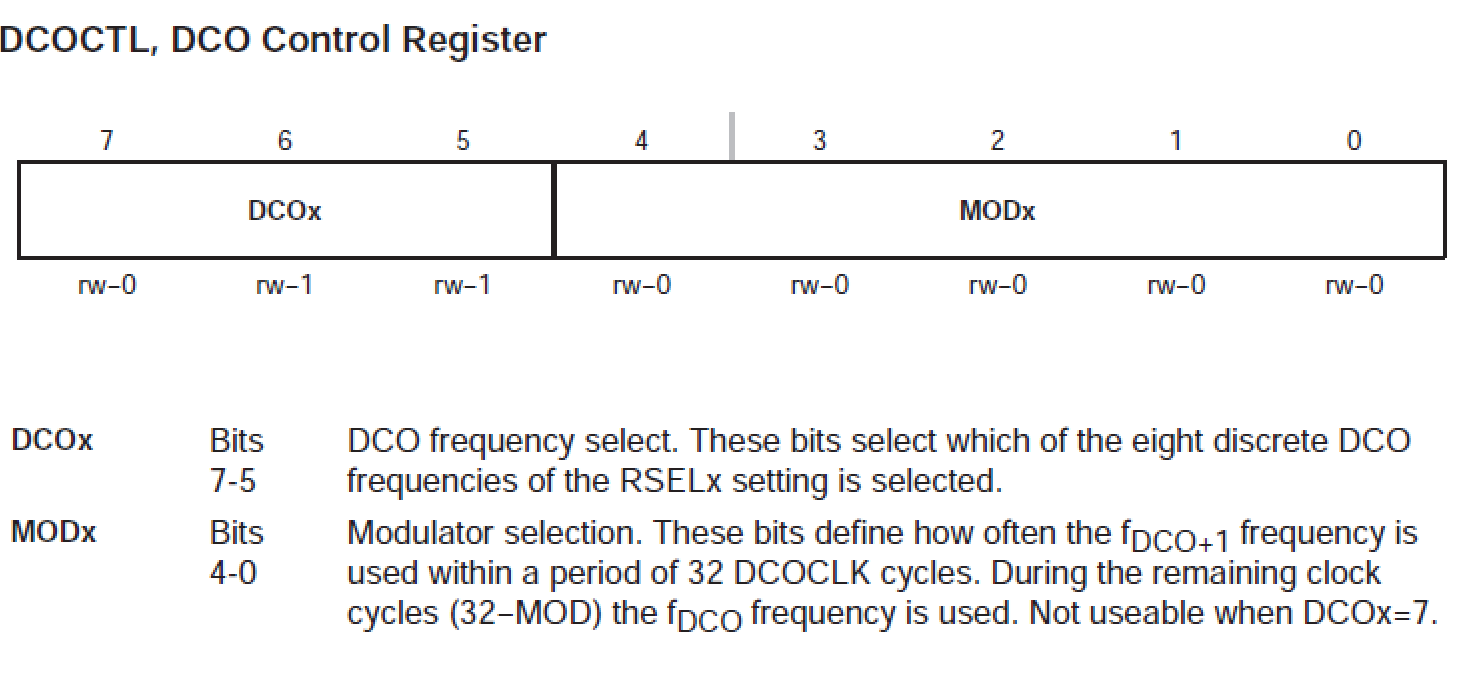

DCOCTL

DCOx:DCO频率选择(8种),可分段进行调节DCOCLK频率。该频率是建立在RSELx选定的频段上。

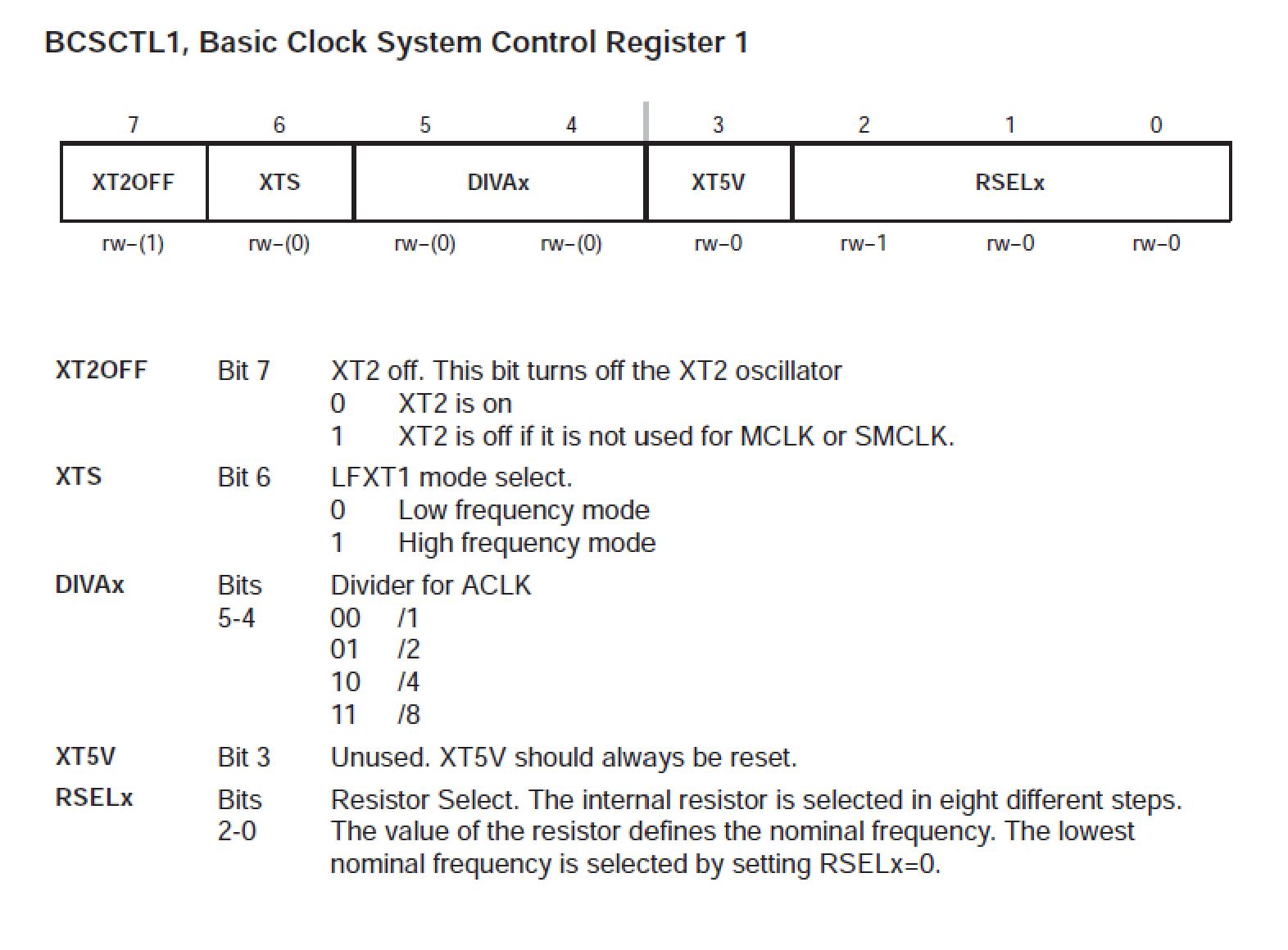

BCSCTL1

RSELx:DCO震荡器的频段选择,通过控制某个内部电阻以决定标称频率。

rw−(1) 默认XT2是关闭的。系统主时钟默认来源于DCO(保证系统先正常运行)。可以不接任何外部晶体。

将MCLK源从DCO时钟切换到晶体时钟(LFXT1CLK或XT2CLK)的顺序为:(后续有代码)

- 打开高频晶体振荡器

- 清除晶体振荡器标志(OFIFG)

- 等待至少50us,保证其起振

- 检测失效标志(OFIFG)。

- 重复步骤1-4,直到OFIFG保持清除状态(没置位),说明系统正常启动。

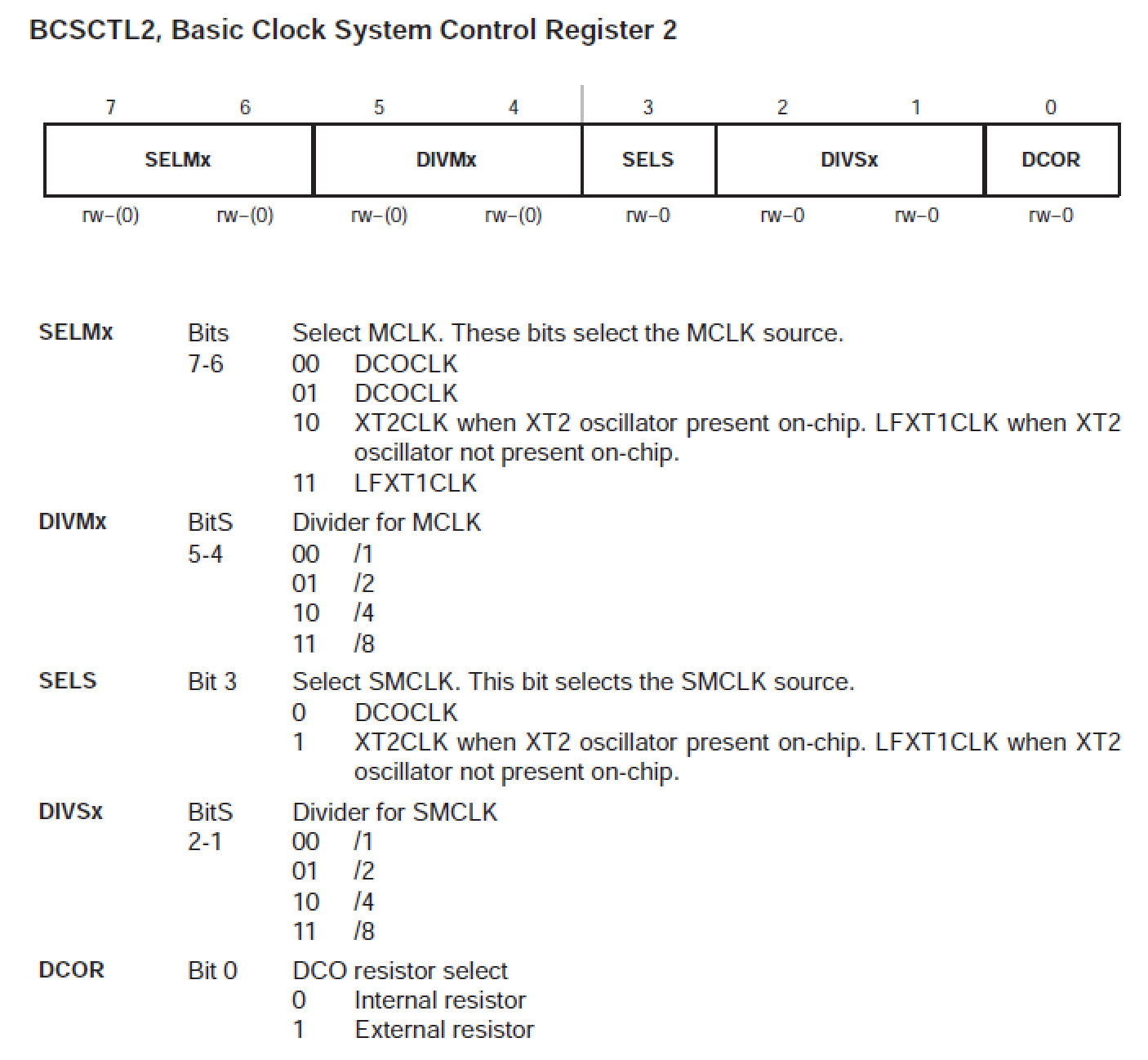

BCSCTL2

SELMx:选择MCLK时钟源

0:MCLK时钟源为DCOCLK(默认)

DIVMx:选择MCLK分频

SELS:选择SMCLK时钟源

0:SMCLK时钟源为DCOCLK(默认)

DIVSx:选择SMCLK分频

IE1

如果OFIE(中断使能位)置1即允许中断。当外部晶体振荡器没起振时,就会发出一个非可屏蔽中断(NMI)

IFG1

振荡器失效的标志,默认OFIFG置0,外部晶振没有起振

总结:41

每天进步多一点,妈妈夸我小天才。

浙公网安备 33010602011771号

浙公网安备 33010602011771号