【计算机组成原理】存储器

存储器的分类

存储器是计算机中的记忆设备,用来存放程序和数据(二进制代码存放)

构成存储器的存储介质,目前主要采用半导体 器件和磁性材料

存储器中最小的存储单元就是一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储器,可存储一个二进制代码(0 1)即一个bit

若干个存储元组成一个存储单元(8bit即一个字节),许多存储单元组成一个存储器。

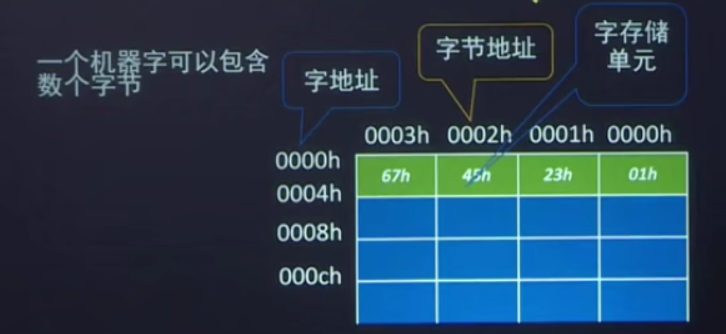

字存储单元(32位):

即存放一个机器字的存储单元,相应的地址称为字地址。

一个机器字可以包含数个字节

分类方法

存储介质:

- 半导体存储器

- 磁表面存储器

存储方式:

- 随机存储器:存取时间和存储单元地址无关 主存

- 顺序存储器:存取时间和存储单元地址有关 磁盘

作用:

- 存储器

- 辅助存储器

- 高速缓存存储器

- 控制存储器

层次化结构

解决容量大 速度快 成本低的矛盾常采用多级存储器体系:告诉缓存存储器 主存储器 外存储器

SRAM:

基本存储元:

基本存储元是组成存储器的基础和核心,他用来存储一位二进制信息0或1

基本存储元组成:

他由两个MOS反相器交叉耦合而藏的除法其,一个存储元存储一位二进制代码,这种电路有2个稳定的状态- 和1

DRAM:

刷新周期:

从上一次对整个存储器刷新结束导下一次对整个存储器全部刷新一遍为止的时间间隔

动态存储器考电容存储信息,因此必须刷新,2116的每个存储元必须2ms刷新一次,当RAS=0时,刷新一行上的128和存储元,因此需要在2ms完成128行个RAS刷新周期

刷新方式:

- 集中式:适用于高速存储器 有死时间 刷新期间不能进行读写

- 分散式:读写交替 不存在死时间 影响效率

- 异步式:

只读存储器:

RAM易失 ROM非易失

RAM ROM随机存储进行信息访问

SRAM做缓存

DRAM需要刷新

采用随机存储:ERPOM DRAM SRAM

不采用随机存储: CDRAM

闪存:信息可读可写 读写速度不一样MOS管组成 半导体存储器 掉电不丢失 非易失 采用随机访问方式,可

替代外部存储器

DRAM和SRAM:DRAM集成度高 DRAM芯片成本低 DRAM速度比SRAM慢 DRAM需要刷新 SRAM不需要刷新

存储器容量扩展:

位扩展:只扩大字长数(即位扩展的芯片同时工作)

连接时:每个芯片具有相同的地址线不同的数据线

字扩展:

字位同时扩展:连接时:每个芯片具有不同的地址线 数据线

D

提高存储器的性能:

顺序编址:某个模块进行存取时,其他模块不工作,某一模块出现故障时,其他模块可以照常工作,通过增添模块来扩充存储器容量比较方便,但各模块串行工作,存储器的带宽收到了限制。

连续地址基本分布在同一个模块内,同一个模块内的地址是连续的。

交叉编址:低两位是片选地址,高三位为地址。

顺序方式存储器连续读取m个字所需时间为t=mT

假设模块字长等于数据总线宽度,模块存取一个字的存储周期为T,总线传送周期为t,存储器的交叉模块数为m(m=4)为了实现流水线方式存取,应答满足T=mt(m=T/t为交叉存取度)

要求模块数须大于或等于m,以保证启动某模块后经过mt时间再次启动该模块时,他的上次存取操作已经完成,连续读取m个字所需的时间为t1=T+(m-1)t

cache的命中率:Nc表示cache完成存取的总次数,Nm表示主存完成存取的总次数,h定义为命中率则有h=Nc、(Nc+Nm)

平均访问时间=cache命中率*cache访问时间+(1-cache命中率)*主存访问时间

访问效率=缓存访问时间/平均访问时间

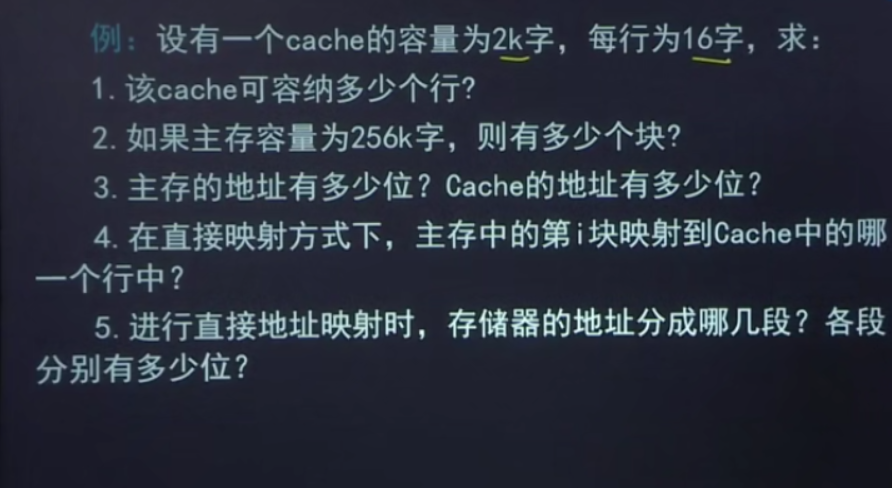

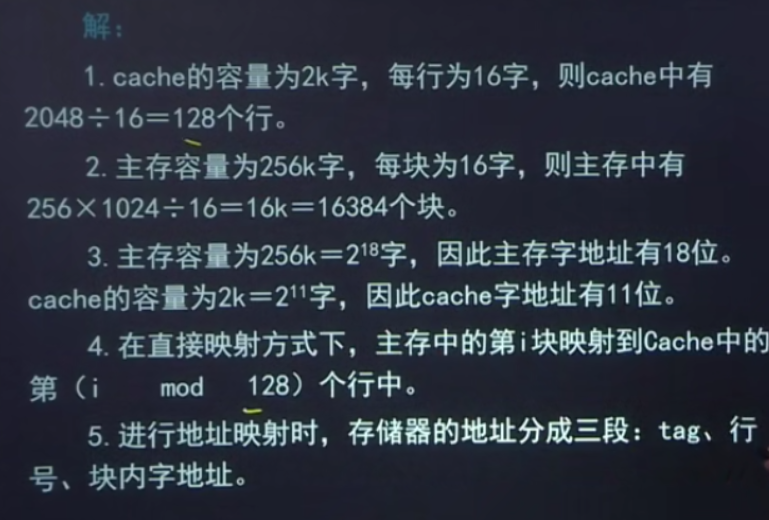

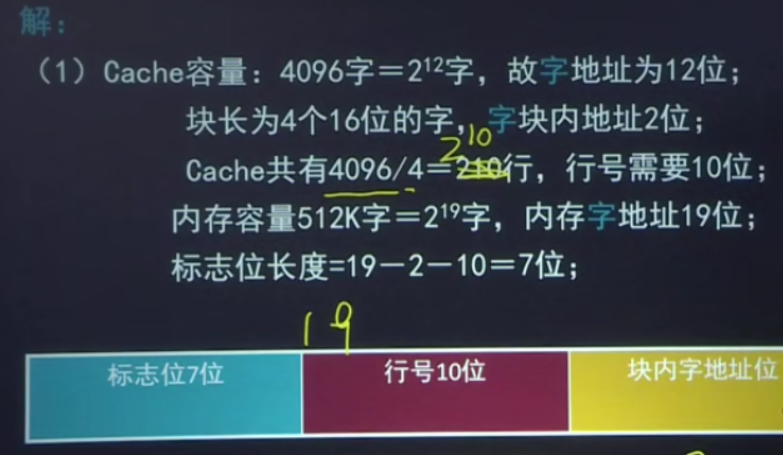

主存与Cache的地址映射:

地址映射:主存地址定位到cache中

1)全相联方式

cache的数据块大小称为行L,设cache共有2的r次方行(行地址r位)

主存的数据库大小为块B,设主存有2的s次方块(块地址s位)

行的长度=块的长度

每个块/行有若干连续的字W组成,字是CPU每次访问存储器时的访问单元

主存中一个快的地址与块的内容一起存于cache的行中,其中块地址存于cache行的标记部分中

全相联映射方式是指主存的一个快直接拷贝到cache中的任意一行上,非常灵活(多对多方式)

优点:冲突概率小 cache利用率高

缺点:比较器电路难于设计实习,适合于容量cache采用

直接映射方式:

多对一的映射方式 i=j mod m(m为cache中的总行数)

优点:硬件简单,成本低

缺点:容易产生冲突,适合大容量cache采用

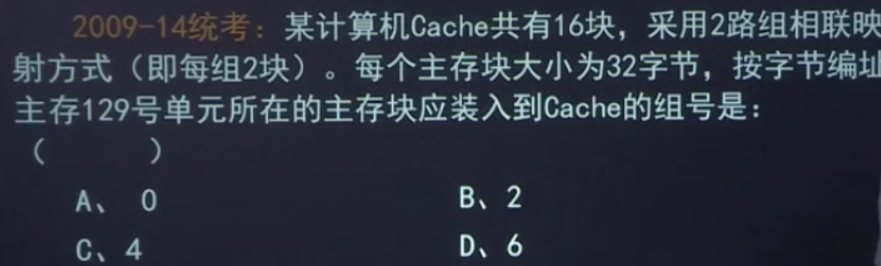

组相联方式

m行分为若干组 q=j mod u

每组2行交2路组相联

cache写操作命令

1、写回发

当CPU写cache命中时,只修改cache的内存,而不立即写入主存,只有当此行被换出是才写回主存。

这种方法减少了主存的访问次数

2、全写法

写cache命中时,cache与主存同时发生写修改

3、写一次法

结合写回法和全写法,第一次写命中时写入内存。

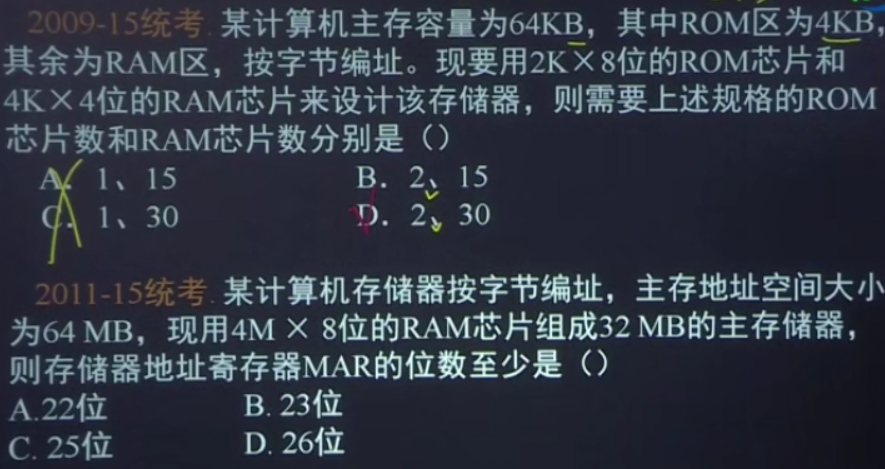

例题

真题

C

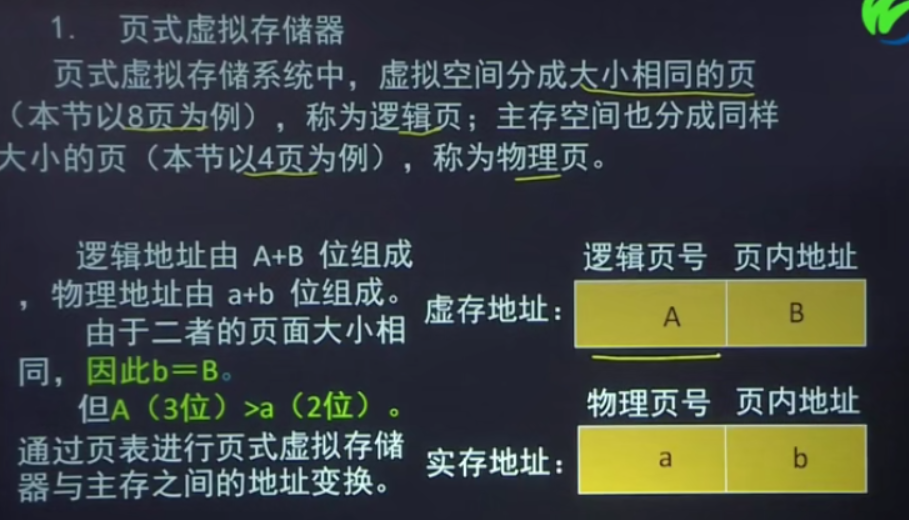

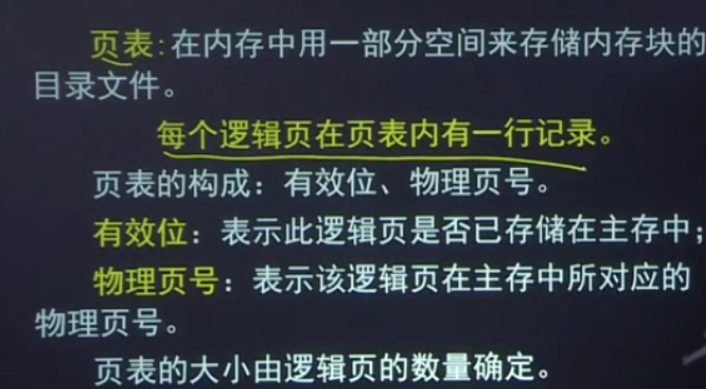

主存-外村层次的基本信息传送单位:

段 页 段页

浙公网安备 33010602011771号

浙公网安备 33010602011771号