并发编程Bug源头

一.简介

编写正确的并发程序是一件困难的事情,往往调试过程中发生很多不确定的事情,这时需要对理论知识的一个认知,能够准确的追踪问题。

二.硬件背景

CPU,内存,I/O设备不断迭代,这三者速度存在差异,CPU和内存的速度差异可以形象的描述:CPU速度最快,内存次之,I/O设备更次之。

为了合理利用CPU的高性能,平衡这三者的速度差异,计算机体系结构、操作系统、编译程序都做出了贡献,主要体现为:

- CPU增加缓存,以均衡与内存速度差异;

- 操作系统增加了进程、线程,以分时复用CPU,进而均衡CPU与I/O设备的速度差异;

- 编译程序优化指令执行次序,使得缓存能够更合理利用。

三.源头

3.1 源头一

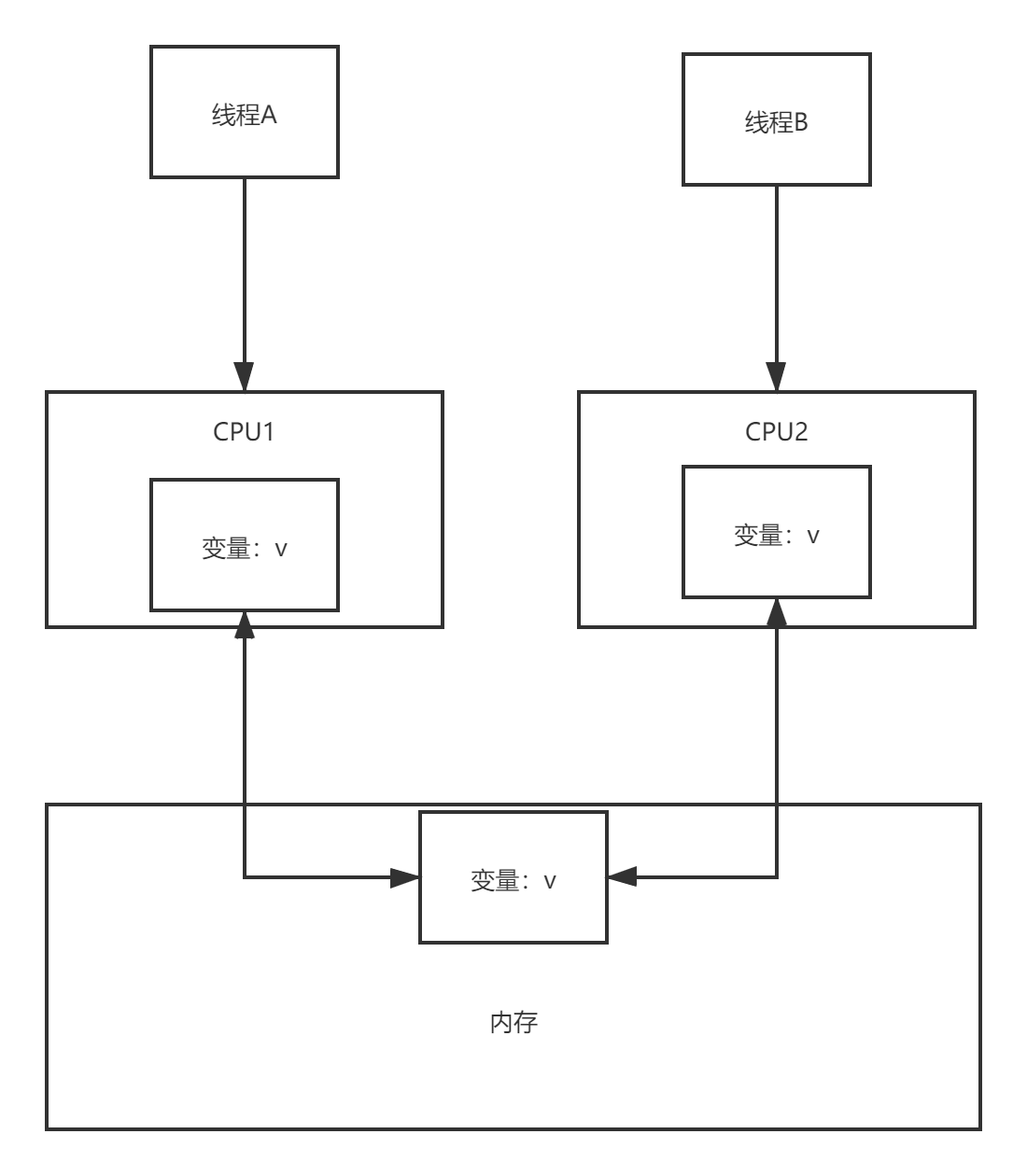

缓存导致的可见性问题

在单核时代,所有的线程都是在一颗 CPU 上执行,CPU 缓存与内存的数据一致性容易解决,所有都是串行。

一个线程对共享变量的修改,另一个线程能够立刻看到,我们称为可见性。

多核时代,每颗 CPU 都有自己的缓存,

浙公网安备 33010602011771号

浙公网安备 33010602011771号