数字模拟电路心得

前言:两次数字电路模拟程序题目集,是从基础逻辑门到复杂组合电路的梯度进阶练习。题目集 1 聚焦与、或、非、异或、同或 5 类基础门电路,核心考查数字电路的入门逻辑、输入输出信息解析及简单电平计算,题量 6 组,难度适中,重点培养字符串处理、哈希表存储及基础逻辑运算的编程能力,覆盖输入不全导致输出无效等基础边界场景。题目集 2 在保留基础门电路的基础上,新增三态门、译码器、数据选择器、数据分配器 4 类组合电路元件,引入控制引脚概念,扩展了引脚分类规则与输出格式,题量增至 10 组,难度显著提升。不仅要求掌握更复杂的元件逻辑(如译码器的控制条件判断、数据选择器的输入选择规则),还需处理多输出元件的状态计算、无效场景的多维度判断(如三态门断开、控制引脚无效),既深化了数字电路的组合逻辑知识,也强化了复杂场景下的编程抽象、分层设计与多规则适配能力,是从基础编程到工程化模拟的重要过渡练习。

设计与分析:

第一次作业

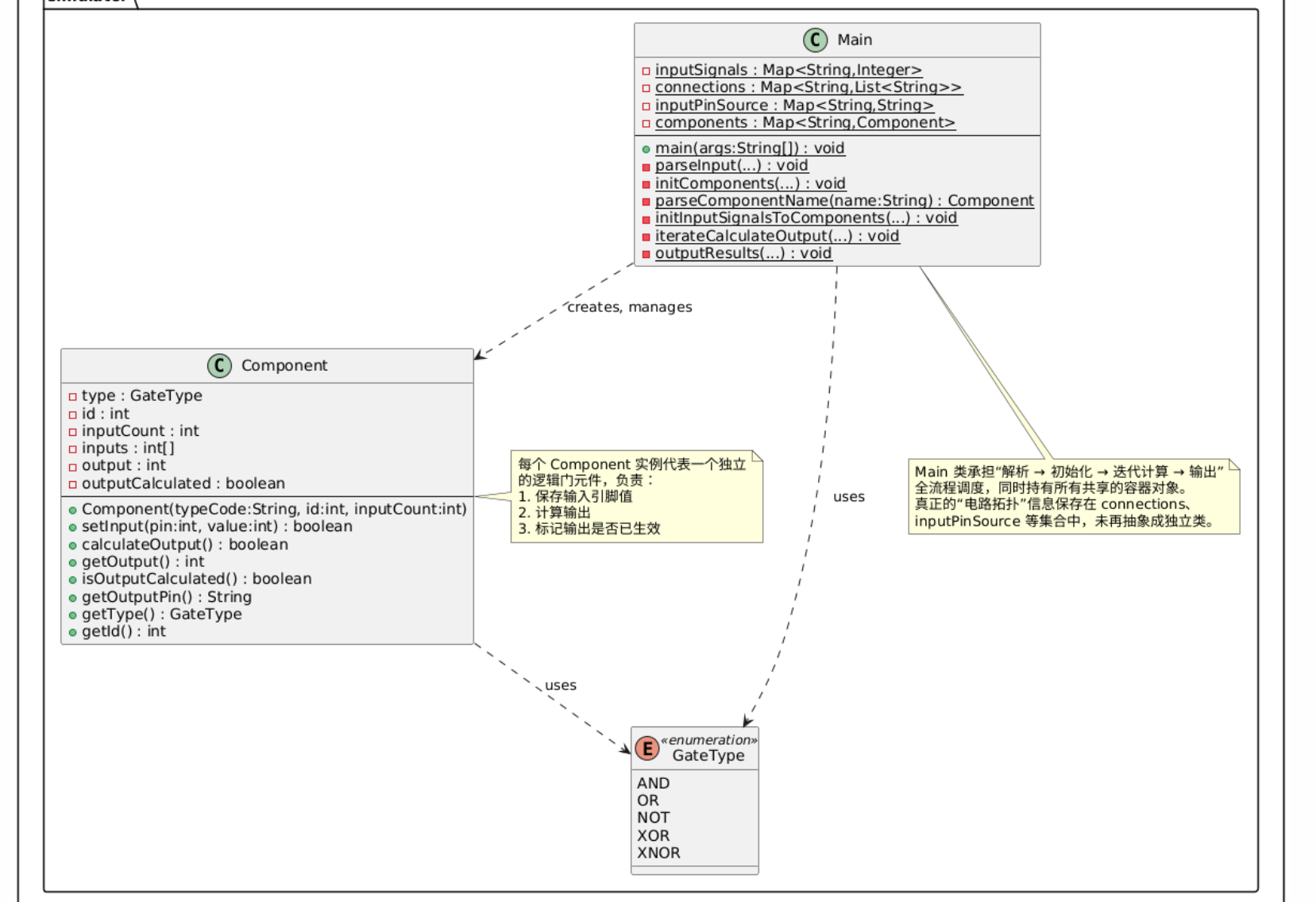

类图设计

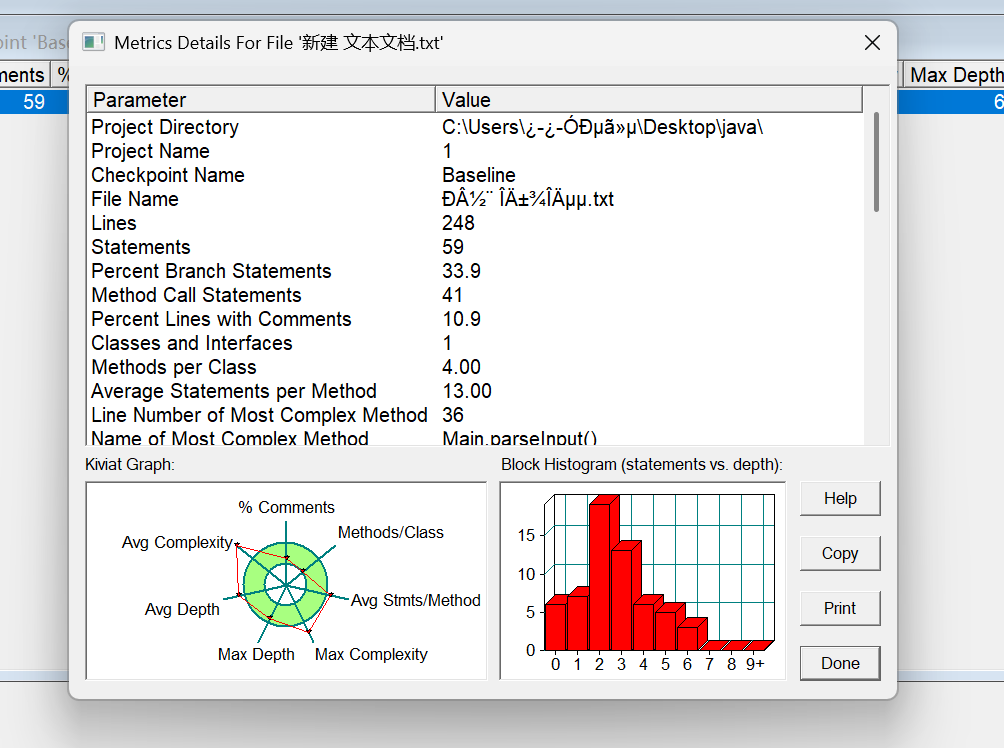

SourceMonitor 度量分析

结合指标和第一次题目集的功能(基础逻辑门),该源码的设计有以下特点:

- 优势点

轻量易实现:仅 1 个类 + 4 个方法,适合基础功能的快速开发,减少了类间交互的复杂度。

方法粒度合理:每个方法平均 13 行,职责单一(如parselnput()仅负责输入解析),便于定位问题。

注释达标:10.9% 的注释占比能保证后续修改时的可读性。 - 待优化点

从工程化角度看,该源码存在以下可提升点:

无抽象设计:仅用 1 个类实现所有功能,若后续扩展(如第二次题目集的进阶元件),会导致代码耦合度急剧上。

最复杂方法风险:parselnput()是最复杂方法,说明输入解析的分支逻辑相对集中,可进一步拆分(。

可扩展性弱:若新增门电路(如第二次的三态门),需在原有类中新增大量分支,不符合 “开闭原则”。

第二次作业

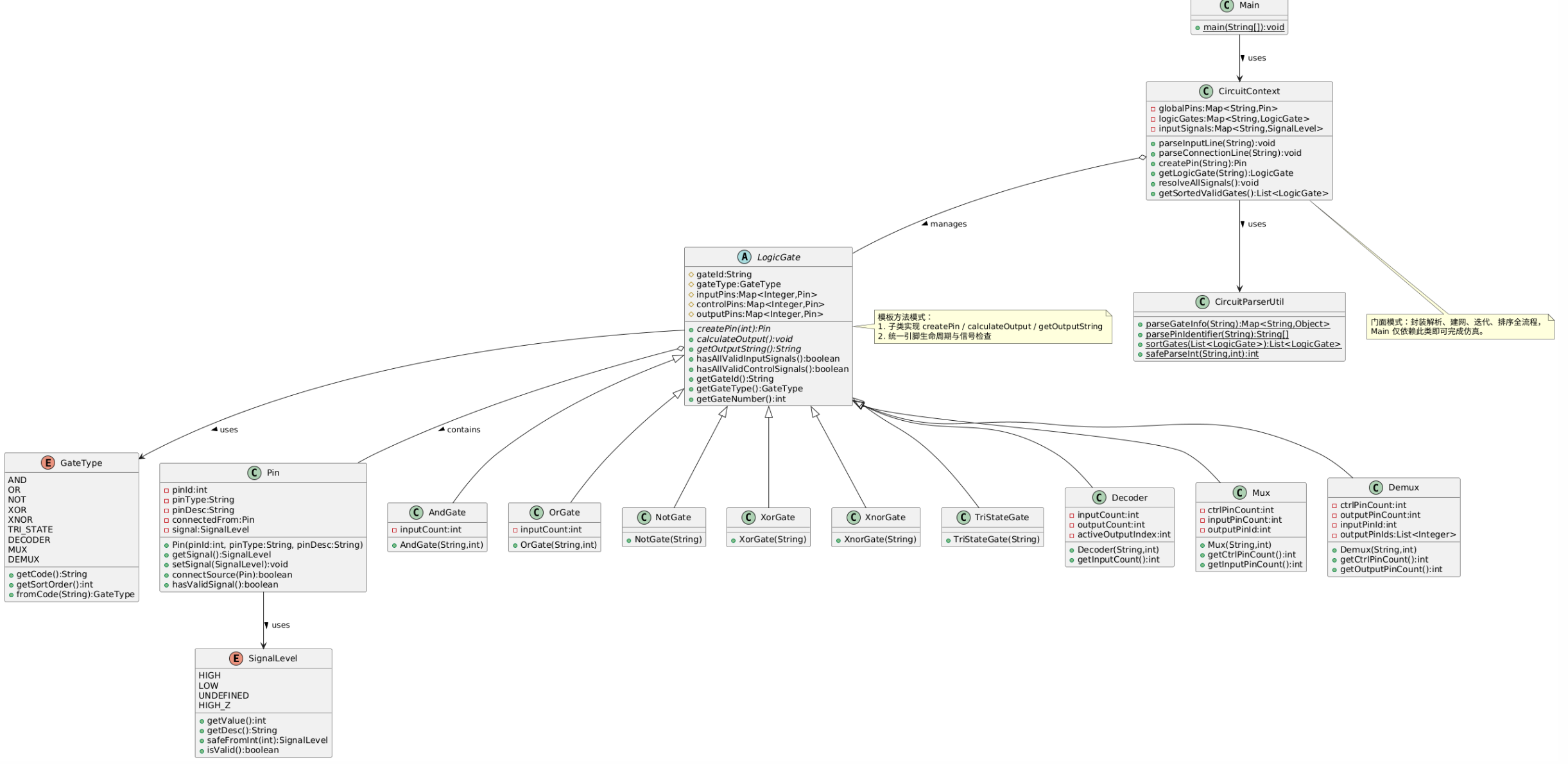

类图设计

![image]()

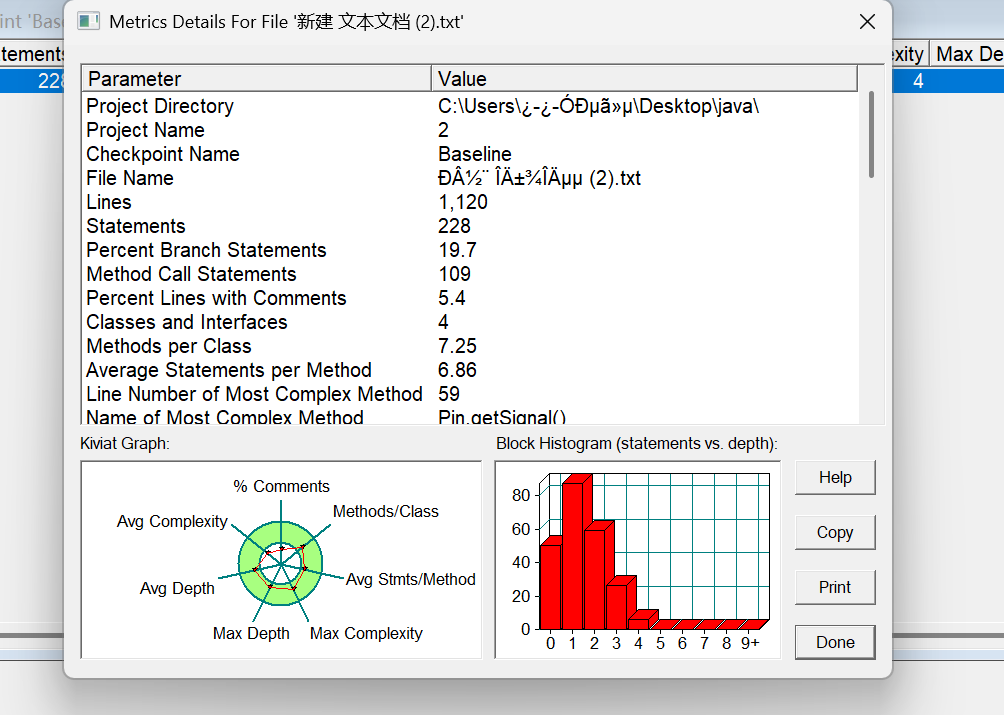

复杂度分析

![屏幕截图 2025-12-14 124414]()

对比第一次,第二次源码的设计有明显的工程化进阶: - 核心变化:从 “单类线性” 到 “多类模块化”

类数量从 1 增加到 4,说明引入了分层设计(例如:Pin类封装引脚信息、Component类封装元件逻辑、Main类负责流程调度);

最复杂方法从 “输入解析” 转为Pin.getSignal(),说明核心逻辑从 “输入处理” 转向 “元件状态计算”,更贴合数字电路模拟的核心(电平信号的传递与计算)。 - 优势点

模块化拆分有效控制复杂度:虽然代码量增加 3.5 倍,但Average Statements per Method从 13 降至 6.86,方法粒度更细,避免了 “超大方法”;

核心逻辑聚焦:将引脚信号的获取封装为Pin.getSignal(),统一管理引脚的电平、状态(有效 / 无效),减少了重复逻辑。

踩坑心得

第一次作业 - 输入解析:引脚与元件名的格式解析漏洞

踩坑场景

最初解析元件名时,仅简单按 “-” 拆分引脚信息(如 “A (2) 1-1” 拆分为元件名 “A (2) 1” 和引脚号 “1”),但未考虑字符串处理的边界:

直接用split("-")拆分时,若元件名中意外包含 “-”(虽题目约束无此情况,但代码鲁棒性不足)会解析错误;

解析与 / 或门的输入引脚数时(如 “A (8) 1” 中的 8),仅通过索引截取数字,未处理 “多位数字”(如 “A (10) 2” 中的 10 会被误解析为 1);

连接信息的中括号处理遗漏,直接按空格拆分时,未先去除首尾的 “[” 和 “]”,导致第一个元素(输出引脚)包含 “[”,最后一个元素包含 “]”,无法匹配引脚格式。

解决思路

采用正则表达式解析元件名和引脚号:用r'^(.+)-(\d+)$'匹配 “元件名 - 引脚号” 格式,确保拆分准确;

用r'([AO])((\d+))(\d+)'专门匹配与 / 或门的元件名(如 “A (8) 1”),精准提取 “类型、输入引脚数、编号”;

解析连接信息时,先通过strip('[]')去除首尾中括号,再按空格拆分,避免符号干扰。 - 逻辑计算:输入引脚完整性校验缺失

踩坑场景

最初编写门电路计算逻辑时,直接遍历已连接的输入引脚电平进行计算,未校验 “元件所有输入引脚是否都接收到有效信号”:

例如异或门 X2 仅连接了 1 号引脚,未连接 2 号引脚,代码仍会按 “仅 1 个输入” 执行异或逻辑,导致输出错误;

与门 A (4) 1 若仅接收到 3 个输入引脚的信号,代码未判断 “输入引脚数是否等于元件定义的引脚数”,直接按现有输入计算,违背题目 “输入不全则忽略该元件” 的要求。

解决思路

为每个元件维护 “定义的输入引脚数”(如 A (4) 1 的输入引脚数为 4)和 “已接收信号的输入引脚集合”;

计算前先校验:已接收的引脚数是否等于定义的引脚数,且所有引脚的电平均为有效(0/1),不满足则跳过该元件的计算。 - 数据存储:全局扁平字典导致状态混乱

踩坑场景

最初用一个全局字典pin_level存储所有引脚的电平(如{"A(2)1-1": 1, "X1-2": 0}),存在两个核心问题:

无法区分 “输入引脚” 和 “输出引脚”,计算元件输出时,误将输出引脚的电平当作输入处理;

不同元件的引脚号重复(如 X1-0 和 Y1-0),易出现数据覆盖;

输出引脚的电平计算后,无法快速关联到对应元件,导致输出排序时需重新遍历字典,效率低。

解决思路

设计分层字典结构:component_info = {元件名: {"input_pins": {引脚号: 电平}, "output_pin": 电平, "type": 类型, "input_count": 定义的输入引脚数}};

按元件类型分类存储(如and_gates = {}、xor_gates = {}),便于后续按 “与→或→非→异或→同或” 的顺序输出。

第二次作业

踩坑场景

新增元件的核心是 “控制引脚决定有效状态”,初期仅关注输入电平计算,忽略了控制条件的校验:

三态门:仅判断输入引脚电平,未校验控制引脚 —— 控制引脚为低电平时仍输出输入电平,未标记为 “无效状态”;

译码器:未校验 “控制引脚 S1=1 且 S2+S3=0” 的条件,直接按输入编码计算输出引脚,导致控制条件不满足时仍输出有效电平;

数据分配器:仅根据控制引脚选择输出引脚,未将未选中的输出引脚标记为 “无效(-)”,全部输出输入电平,违背题目要求。

踩坑场景

开发时未复用第一次作业的基础门电路解析、计算逻辑,而是重新编写,导致:

基础门电路(与 / 或 / 非)的输入完整性校验逻辑重复,且与新增元件的校验规则冲突;

输入解析函数重复编写,第一次的正则表达式解析逻辑未复用,新增元件解析时又出现格式错误;

代码耦合度极高,修改一个元件的解析规则,会影响其他元件的逻辑。

解决思路

提取通用模块:将 “输入解析(INPUT / 连接信息)”“引脚类型判断”“有效性校验” 等通用逻辑封装为独立工具函数,供所有元件调用;

采用 “抽象父类 + 子类” 结构:定义Component抽象父类,包含通用方法(parse_pin()、check_valid()),基础门电路和新增元件作为子类,重写专属的calculate()和format_output()方法;

分类管理元件:按 “与 / 或 / 非 / 异或 / 同或 / 三态 / 译码器 / 选择器 / 分配器” 分类存储,复用第一次的排序逻辑,仅新增后续四类元件的排序。

改进建议 - 重构代码架构,强化抽象与模块化

两次作业的核心问题之一是代码耦合度高,第一次作业以线性代码为主,第二次作业虽拆分少量类但无统一抽象层,导致新增逻辑时易引发连锁错误。建议搭建 “解析 - 计算 - 调度” 三层架构:

解析层:将 INPUT 信息、连接信息的解析逻辑独立封装,统一处理格式校验、字符串拆分、元件名与引脚号提取,避免不同元件模块重复编写解析代码,同时提升解析逻辑的鲁棒性,减少格式错误导致的计算偏差;

计算层:为所有电路元件定义统一的抽象基础逻辑,提炼出 “有效性校验、电平计算、输出格式化” 三类核心行为,各类元件仅需实现自身专属逻辑,复用基础校验规则,比如基础门电路和进阶的三态门、译码器,均先校验输入 / 控制引脚完整性,再执行计算;

调度层:单独封装电路管理逻辑,负责元件实例化、信号传递、计算流程控制和输出排序,解耦 “解析 - 计算 - 输出” 的全流程,让每一层仅聚焦自身职责,降低修改某一环节对整体代码的影响。 - 优化数据管理方式,适配元件特性

第一次作业采用扁平结构存储引脚电平,无法区分引脚类型;第二次作业面对多输出、多控制引脚的元件,数据存储混乱,无效状态标记不清晰。建议按元件特性分层管理数据:

为引脚建立统一的状态描述体系,明确区分控制引脚、输入引脚、输出引脚,记录每个引脚的电平、信号来源,避免多输出引脚连接同一输入引脚导致的信号冲突,也能快速识别引脚是否接收到有效信号;

为每个元件关联 “定义的引脚数量” 与 “已连接的引脚集合”,通过两者的匹配度判断输入是否完整,同时标记元件的 “有效 / 无效” 状态,无效元件直接跳过计算,避免无效数据干扰输出结果。 - 完善注释与文档体系,提升可维护性

第一次作业注释占比虽达标,但核心逻辑注释缺失;第二次作业注释占比不足,新增元件的控制规则、引脚对应关系无说明,导致后续调试和修改时难以快速理解代码逻辑。建议建立标准化的注释规范:

针对类和核心方法,明确说明功能、核心逻辑与使用规则,比如三态门需标注控制引脚的电平规则,译码器需说明控制条件与输出逻辑的对应关系;

针对关键变量和特殊逻辑,补充注释说明设计思路,比如控制引脚编码转换的位权规则、数据分配器无效引脚的标记逻辑;

额外整理元件规则文档,记录每类元件的引脚定义、控制条件、输出格式,作为代码的补充说明,便于后续维护和扩展。 - 构建全覆盖的测试体系,提前规避边界问题

两次作业均未系统设计测试用例,仅依赖题目样例验证,导致输入不全、控制引脚无效等边界场景的错误未被及时发现。建议围绕 “正常场景 - 边界场景 - 异常场景” 构建测试体系:

正常场景验证核心逻辑正确性,比如所有引脚连接正常、控制条件满足时,各类元件的输出是否符合数字电路规则;

边界场景聚焦临界条件,比如输入引脚不全、控制引脚电平无效、编码转换到临界值(如数据选择器控制引脚全 1)时,元件是否能正确标记为无效或输出对应结果;

异常场景预留扩展空间,比如引脚格式错误、信号来源冲突等不符合题目约束的情况,提前设计异常处理逻辑,避免程序崩溃。

总结

本阶段通过两次数字电路模拟程序题目集和课堂测验,完成了从基础逻辑门电路到复杂组合电路模拟的系统性学习,既深化了数字电路专业知识,也提升了工程化编程能力,核心收获体现在以下三方面: - 数字电路知识的深度落地

从第一次聚焦与、或、非等 5 类基础逻辑门的 “输入 - 输出” 二态逻辑,到第二次新增三态门、译码器、数据选择器等 4 类组合电路的 “控制 - 输入 - 输出” 三态逻辑,我完整掌握了组合电路的核心工作原理:理解了控制引脚对电路状态的决定性作用(如三态门的导通 / 高阻、译码器的有效 / 无效),掌握了编码转换(如控制引脚编码对应输入 / 输出选择)、多输出元件状态管理(如数据分配器的有效 / 无效引脚区分)等关键逻辑,实现了从 “理论记忆” 到 “代码建模” 的转化,真正理解了数字电路元件的工程应用逻辑。 - 编程能力的工程化进阶

两次题目集推动编程思维从 “线性功能实现” 转向 “模块化、抽象化设计”:第一次作业中仅能完成基础的输入解析和逻辑计算,但代码耦合度高、冗余多;第二次作业通过拆分类、封装通用方法,初步搭建了分层架构,掌握了 “数据结构化存储”“通用逻辑复用”“特殊场景适配” 等工程化技巧。课堂测验则暴露了边界场景处理、规则细节把控的短板,让我意识到编程不仅要实现核心功能,更要兼顾鲁棒性和规范性,比如输入引脚完整性校验、输出格式精准匹配等细节,都是程序能否符合要求的关键。 - 问题解决与工程思维的养成

开发过程中遇到的引脚规则混淆、控制逻辑遗漏、多输出格式错误等问题,让我形成了 “先建模后编码” 的解决思路:面对复杂元件,先梳理清楚引脚规则、控制条件、输出要求,绘制逻辑真值表或引脚映射关系,再设计数据结构和代码逻辑,而非直接堆砌代码。同时,通过对比 SourceMonitor 代码分析报表,理解了代码复杂度、重复率、注释率等指标的意义,学会了从工程化角度评估代码质量,而非仅关注 “功能是否实现”。

浙公网安备 33010602011771号

浙公网安备 33010602011771号