实验三

3.1

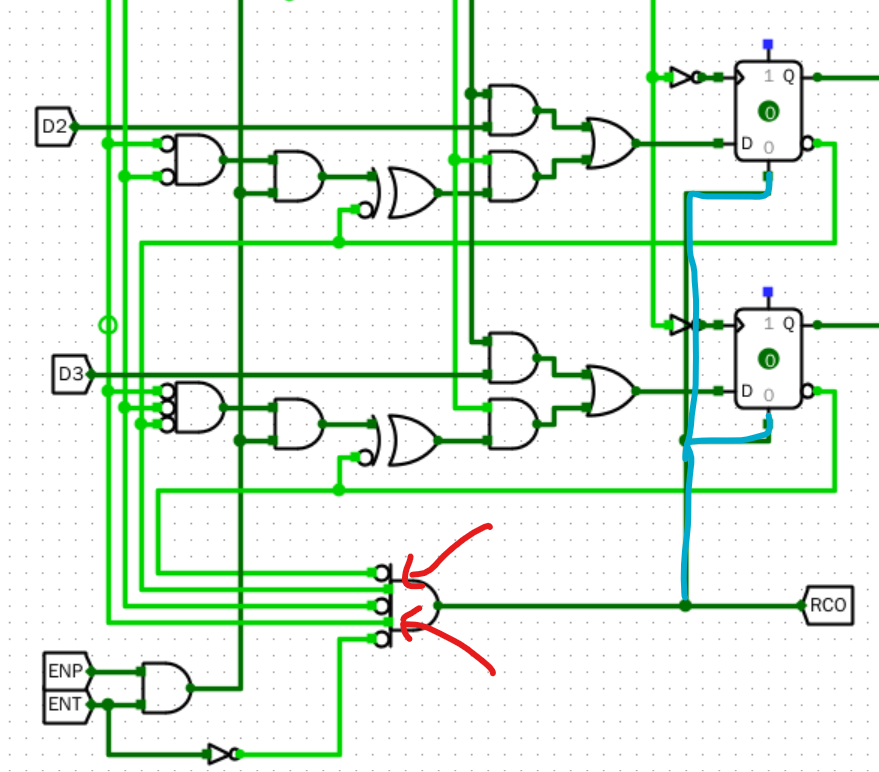

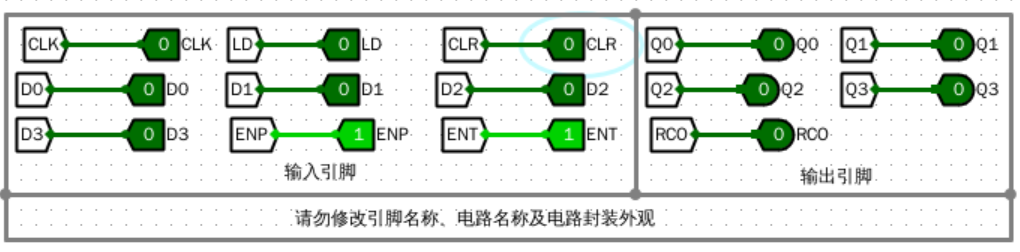

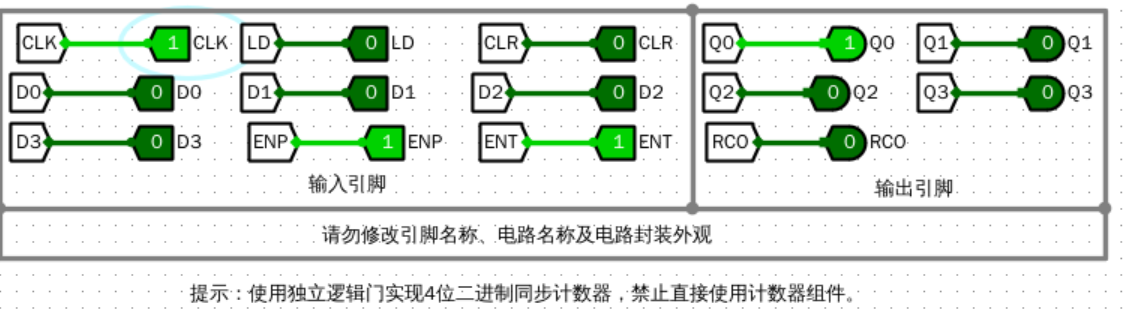

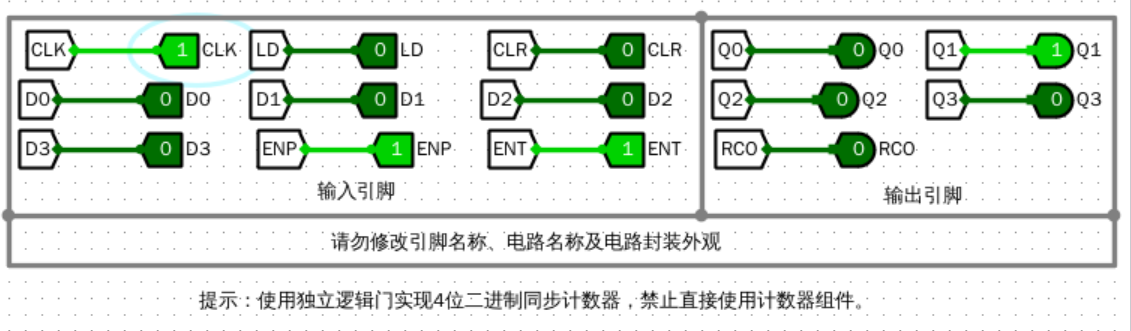

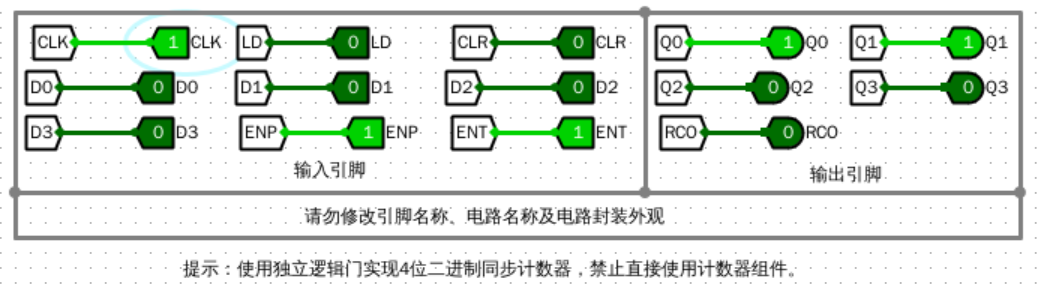

- 构建 4 位同步二进制计数器 CNTR4U子电路。

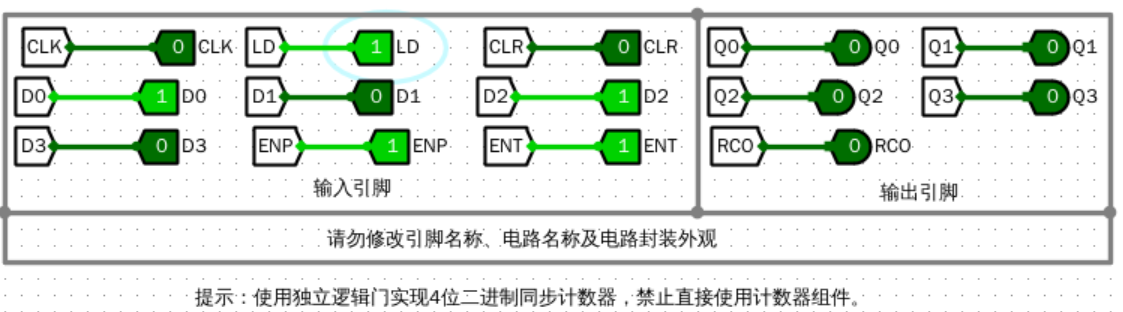

整体方案设计

输入输出引脚

- CLK:时钟

- D0~D3:用于装载的数据,代表计数开始的初始值

- LD:装载标志,即标志是否从初始值开始计数

- CLR:重置标志,表示是否将Q置0

- ENT、ENP:控制是否锁定计数器,即是否自增。两者必须同时为1,计数器才可以计数

- Q:4位输出

- RCO:是否已达最大值,即Q是否全为1

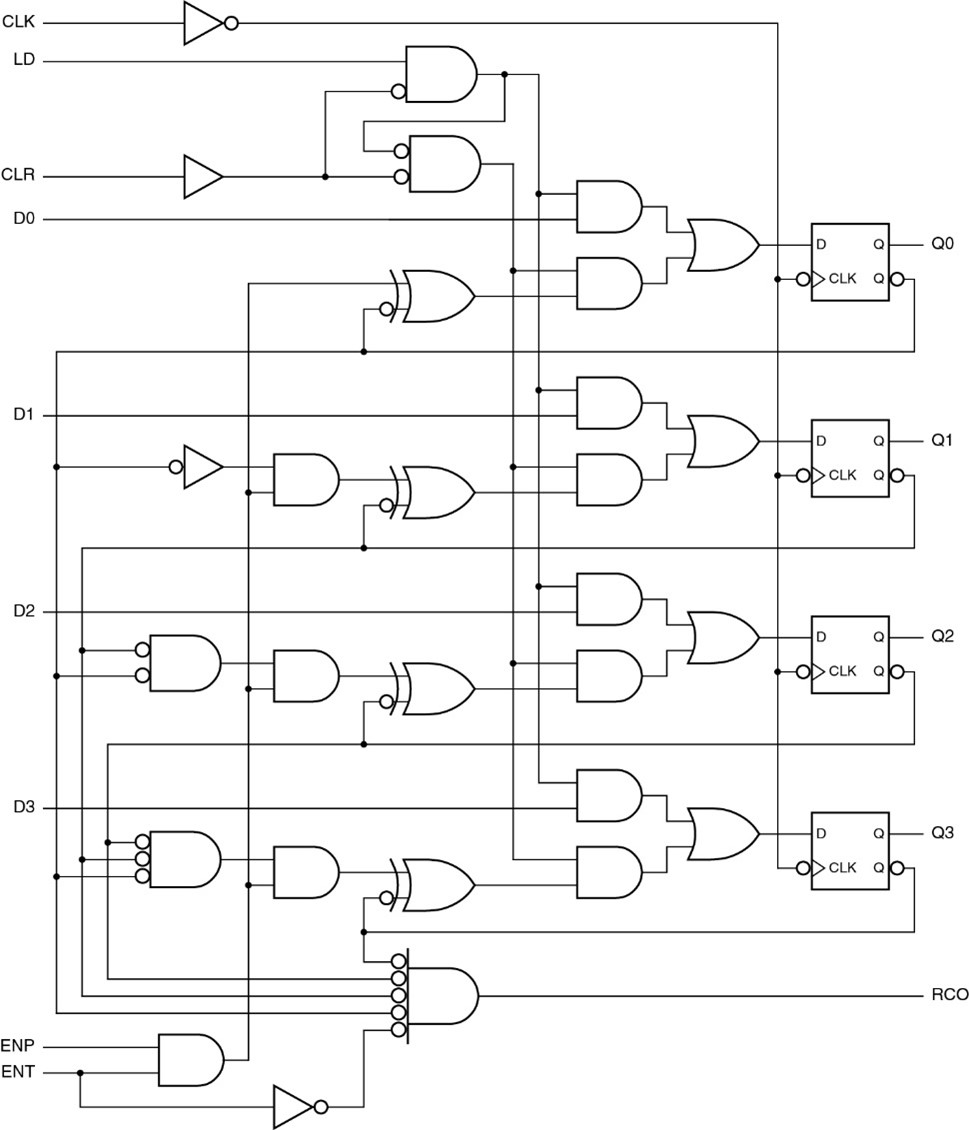

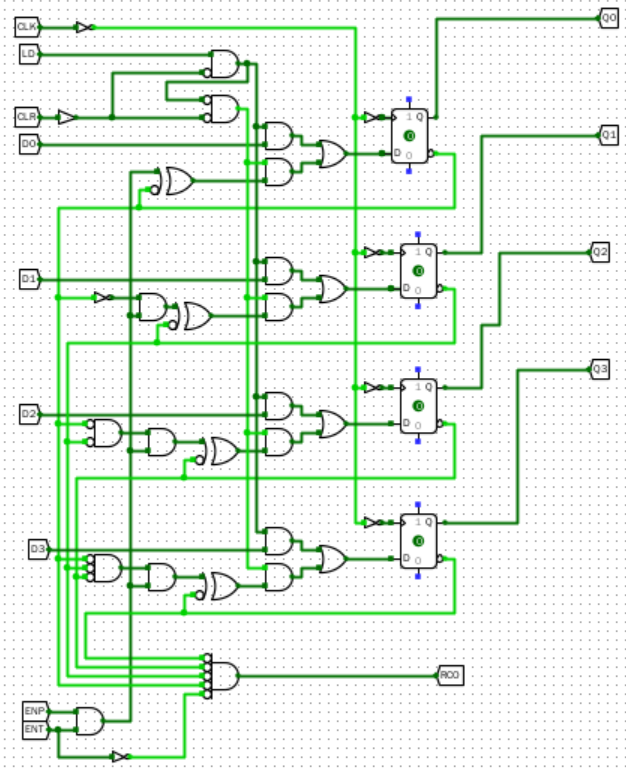

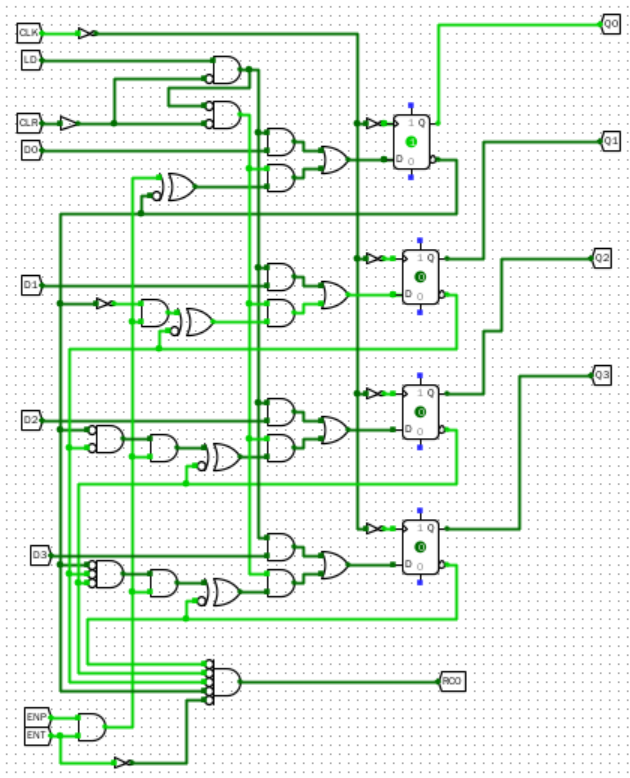

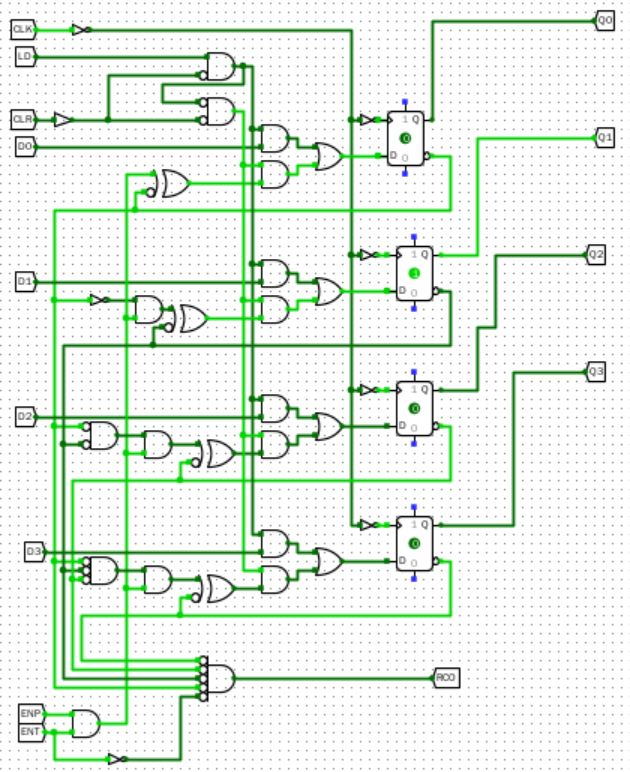

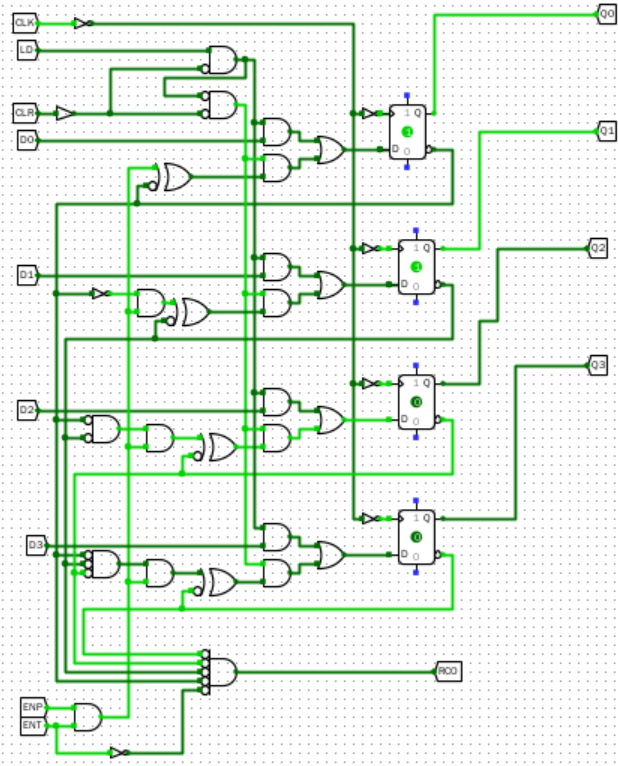

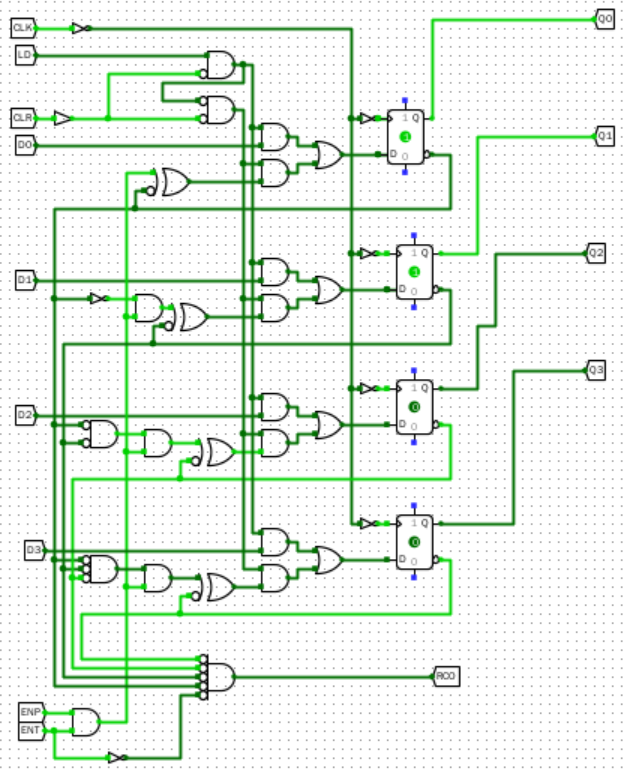

原理图

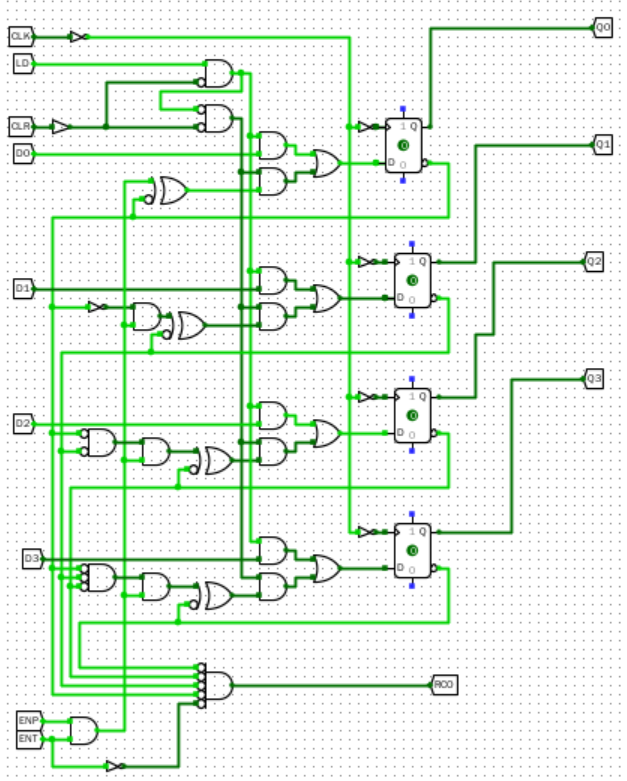

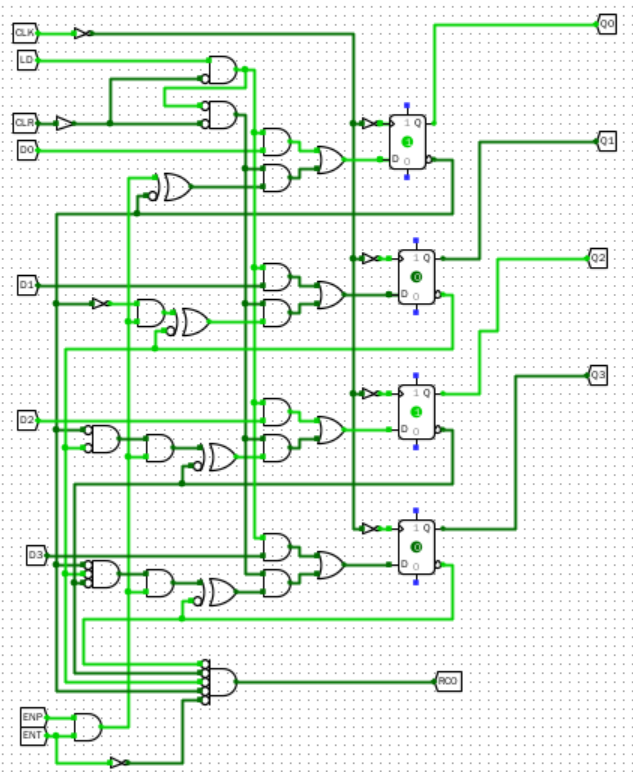

电路图

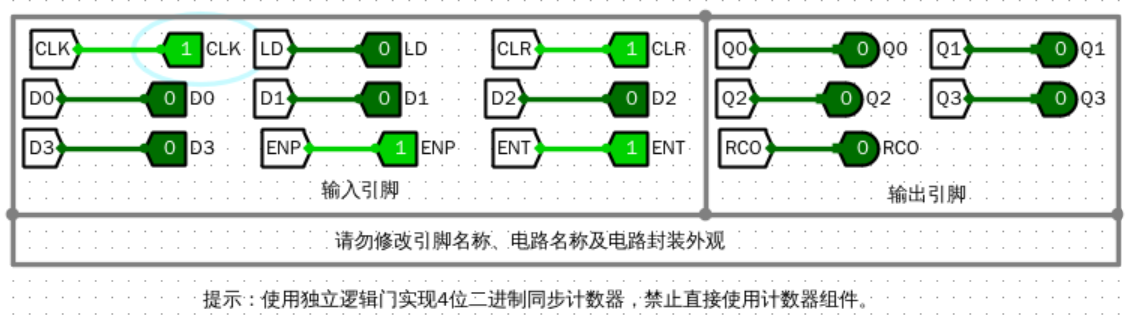

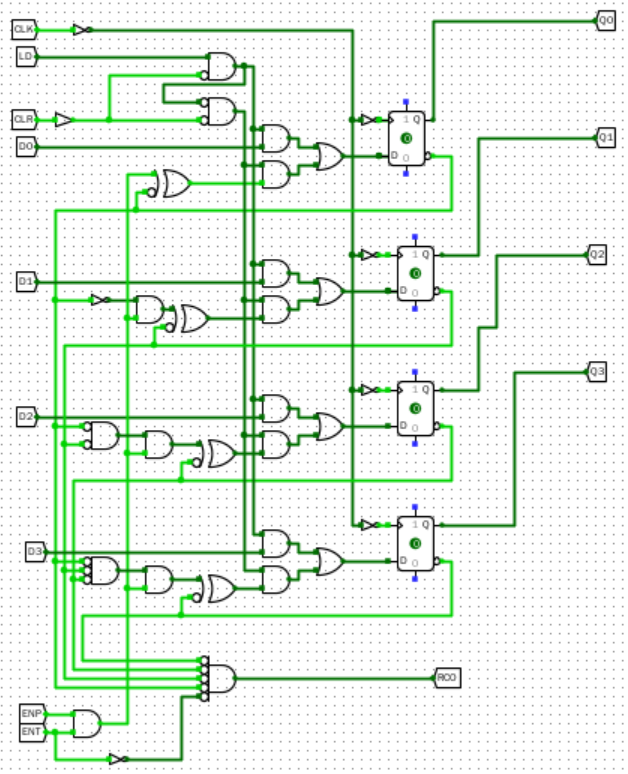

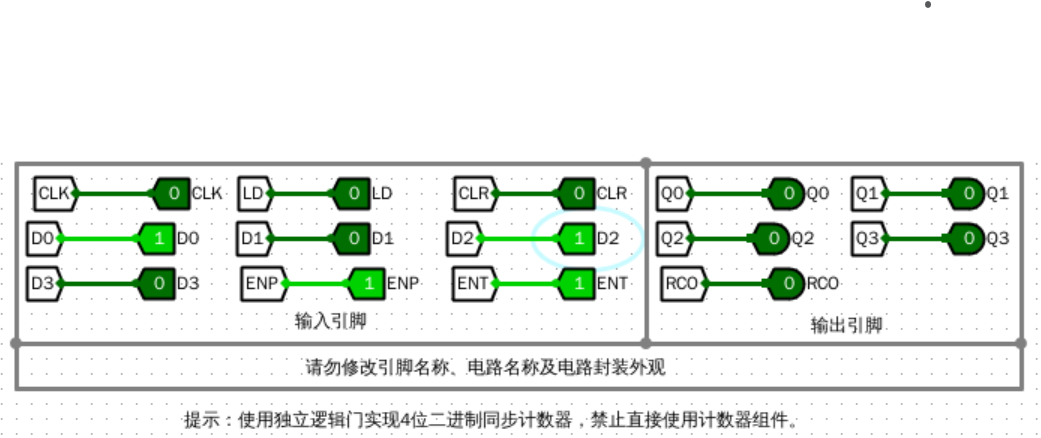

仿真测试

-

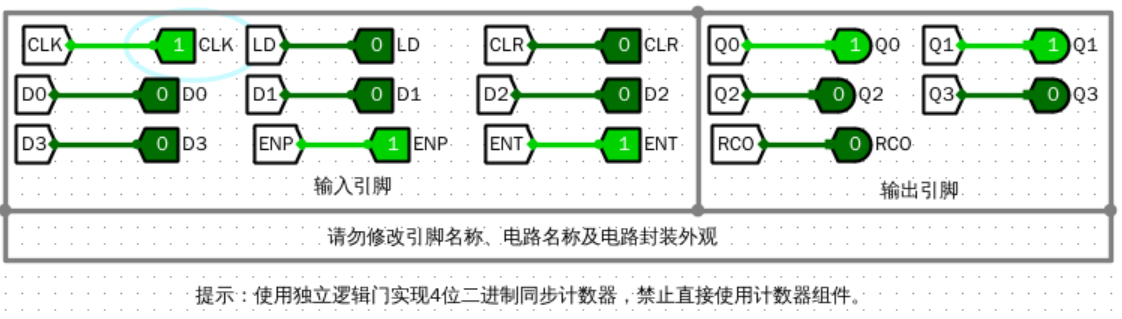

首先进行自增测试,测试enp、ent=1时能否实现每次时钟脉冲结果加1

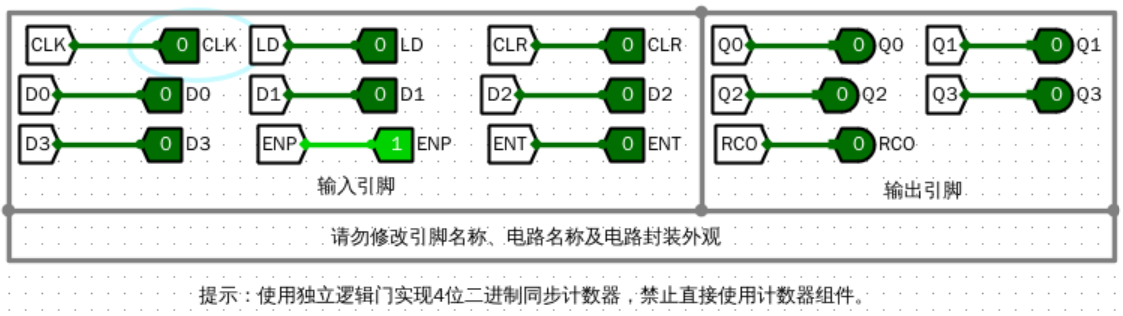

- 初始状态

![image]()

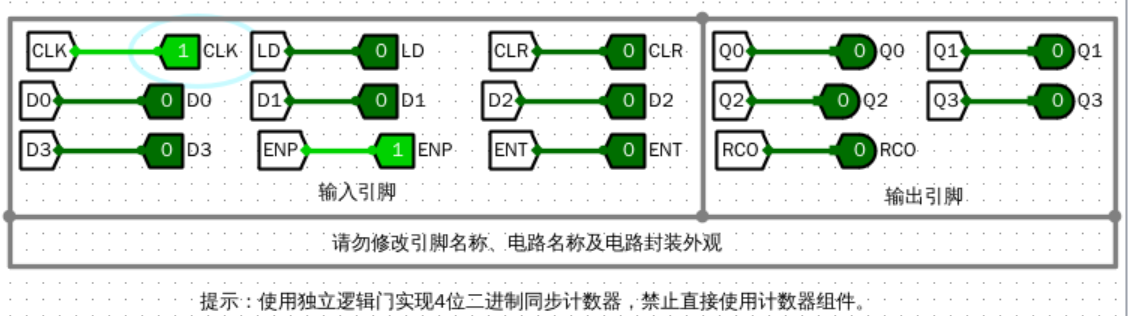

- 加一

![image]()

![image]()

- 加二

![image]()

![image]()

- 加三

![image]()

![image]()

- 初始状态

-

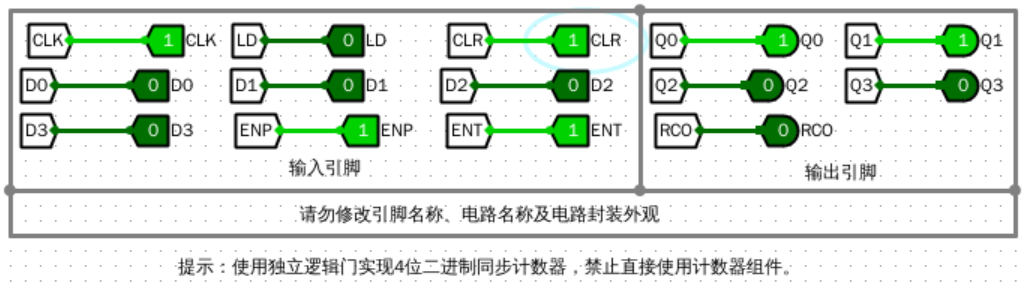

clr测试,将clr置为1,再进行一次时钟脉冲

- 脉冲前

![image]()

- clr置1

![image]()

![image]()

- 进行脉冲后

![image]()

![image]()

- 脉冲前

-

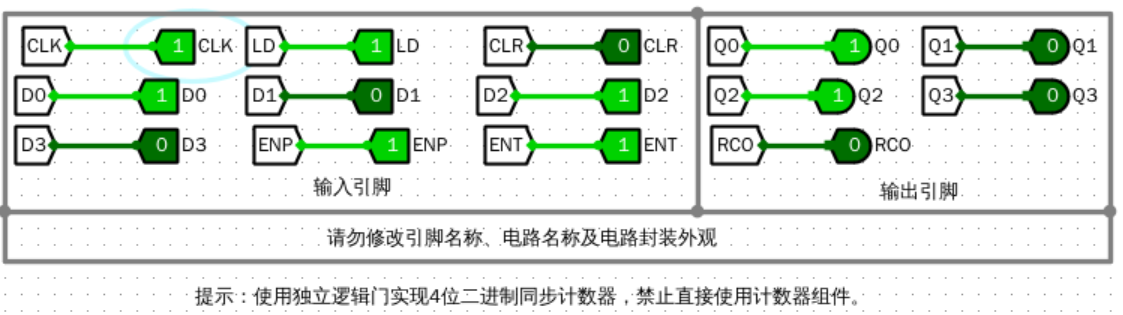

LD测试,将LD设置为true,测试从D进行装载

- 设定初始值

![image]()

- LD置1

![image]()

![image]()

- 进行脉冲

![image]()

![image]()

- 设定初始值

-

测试使用ENP、ENT锁定

- 脉冲前

![image]()

- 脉冲后

![image]()

可以看到没有变化

- 脉冲前

错误现象及分析

没遇到错误

3.2

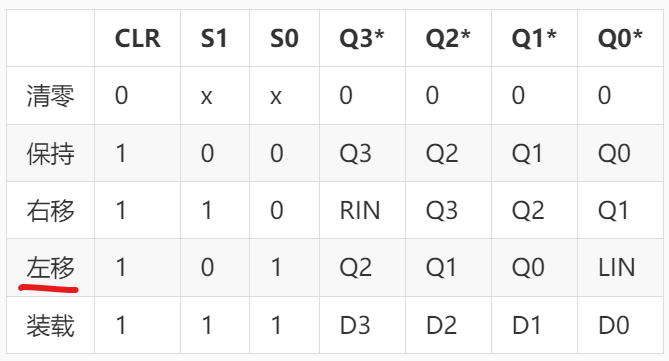

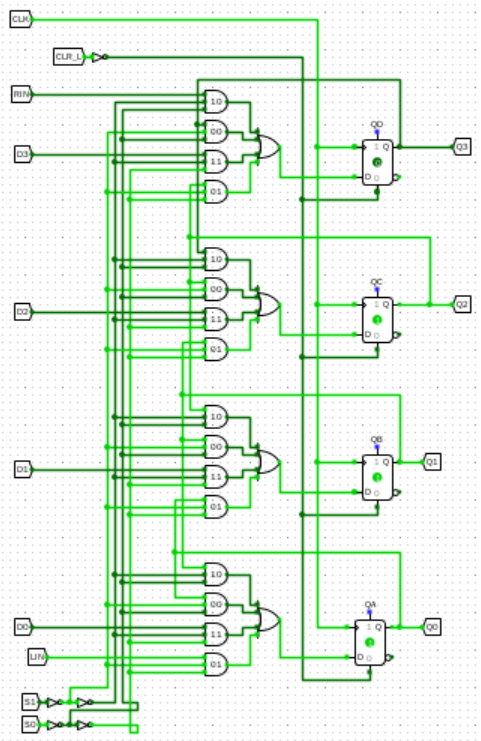

- 构建 4 位通用移位寄存器电路SHRG4U

整体方案设计

输入输出引脚

- CLK:时钟脉冲

- LIN/RIN:左移/右移的移入位

- CLR_L:清0标志位

- D0-D3:要装载的值

- Q0-Q3:输出结果

- S1S0:运算模式的选择

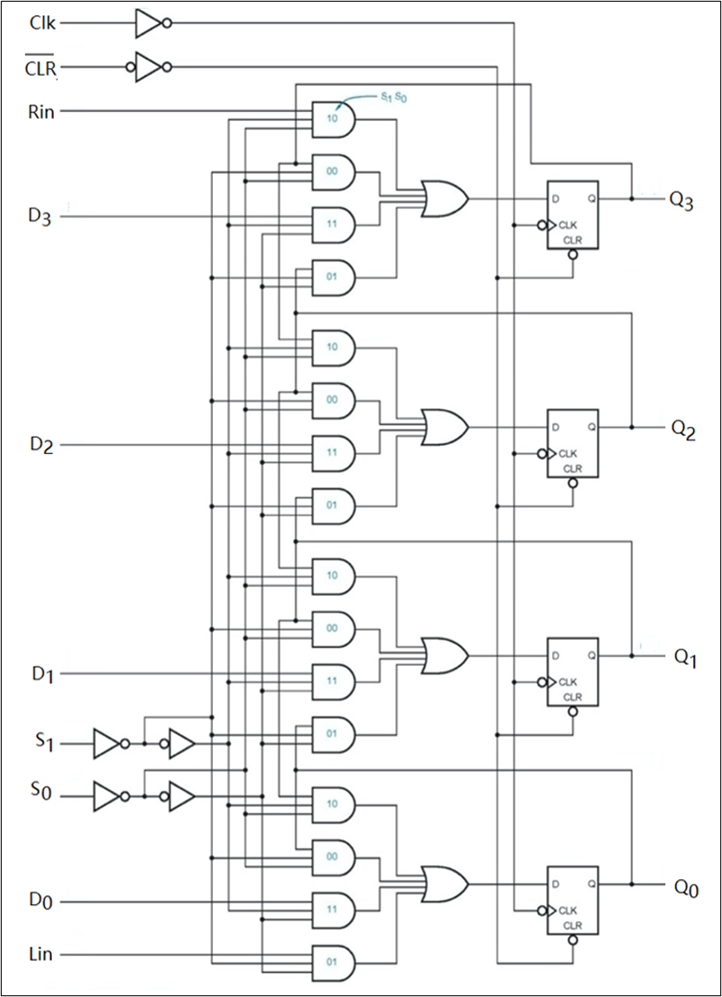

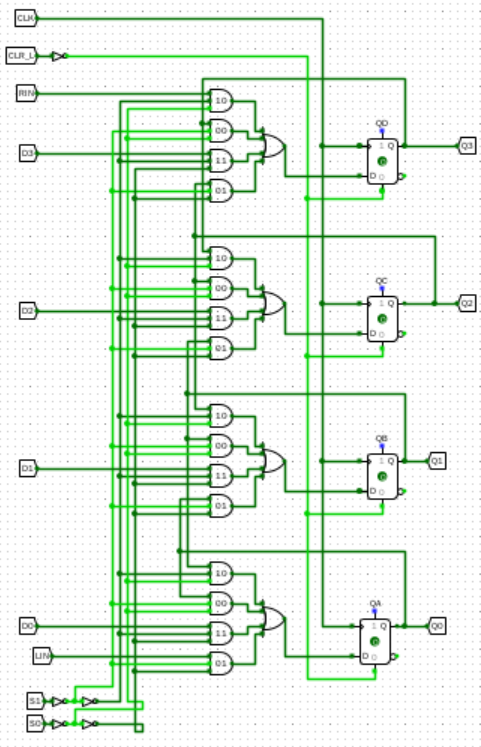

原理图

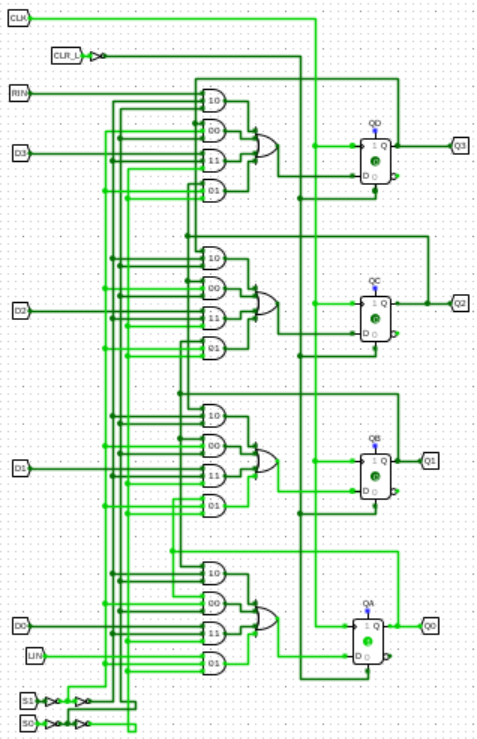

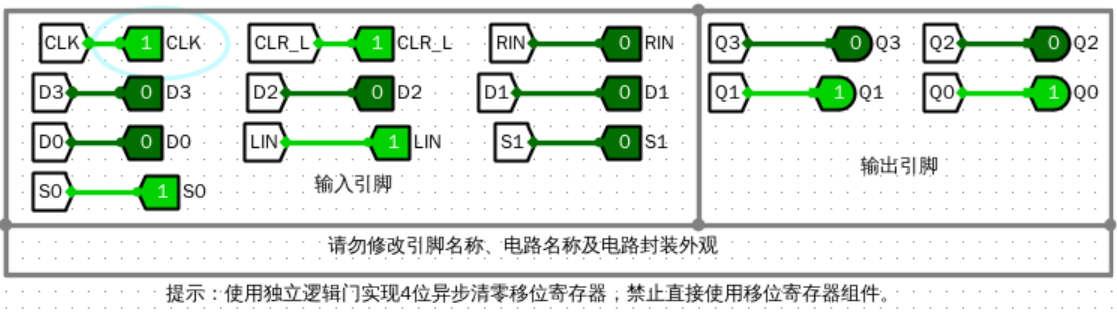

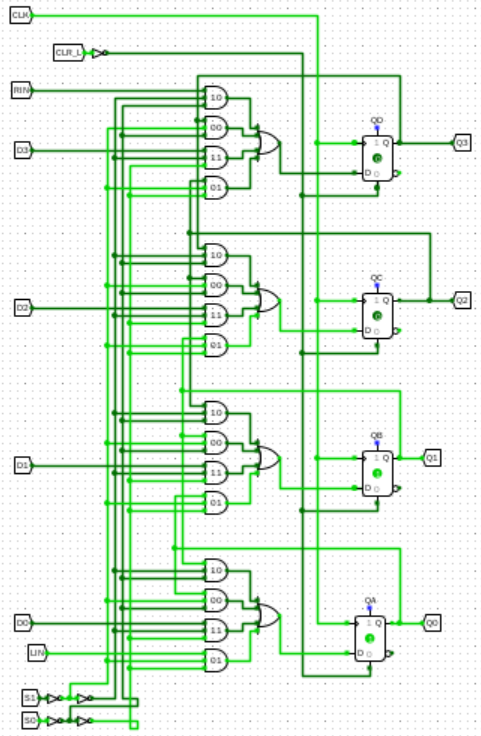

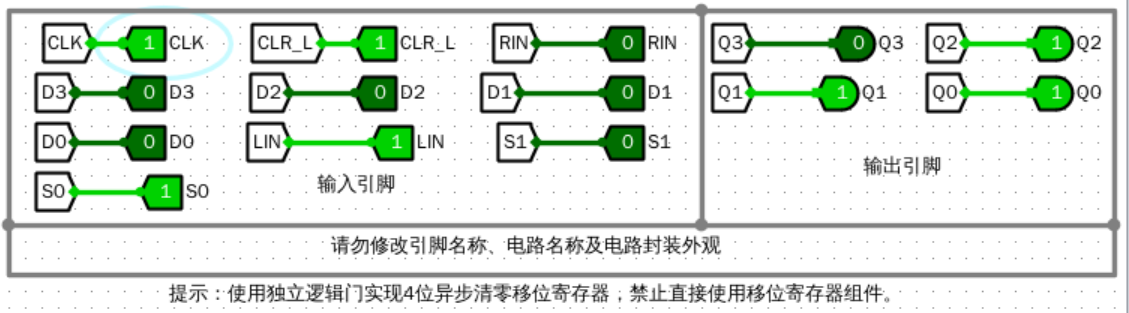

电路图

仿真测试

情况太多了,测试一种左移的

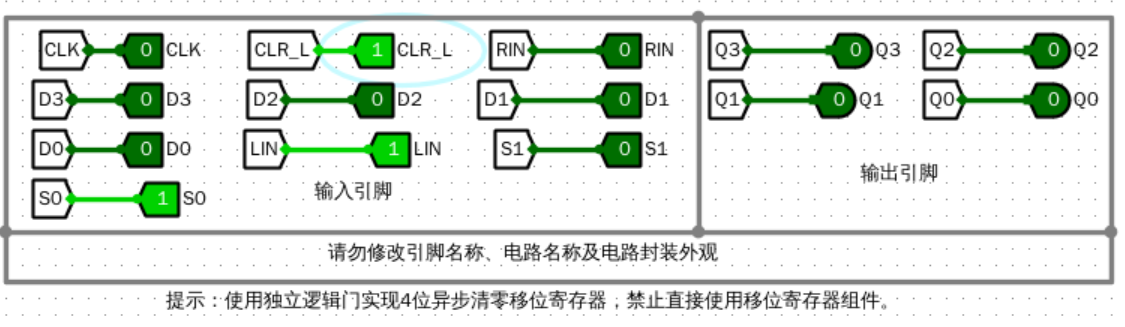

- 初始状态(注意CLR_L是低电平有效)

![image]()

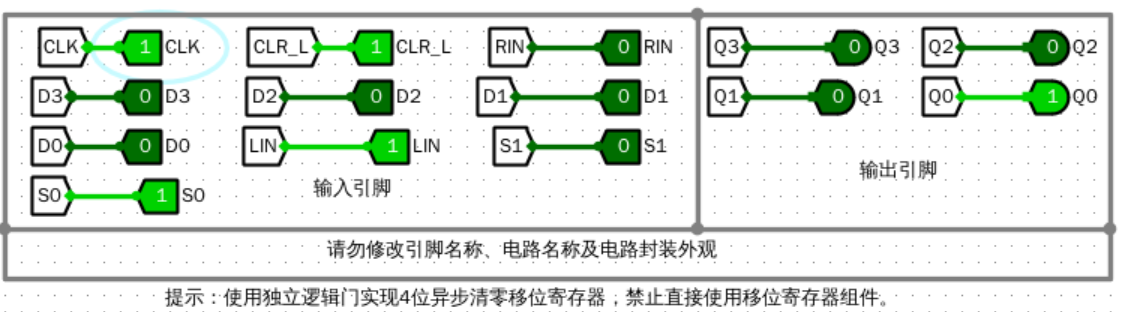

- 移动一位

![image]()

![image]()

- 移动两位

![image]()

![image]()

- 移动三位

![image]()

![image]()

- 移动四位

![image]()

再继续移动输出不会变化,可以看到就使用LIN依次填充

错误现象及分析

没有遇到任何错误

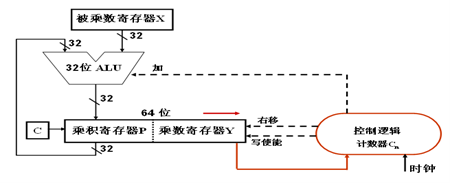

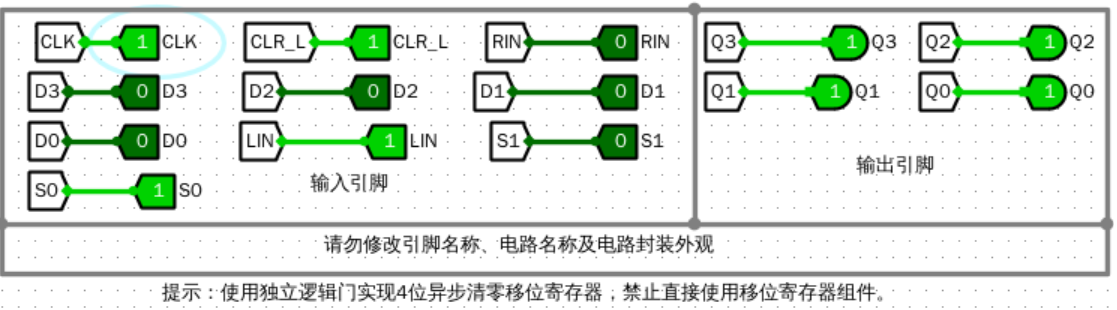

3.3

实现两个四位二进制无符号数相乘的功能

整体方案设计

输入输出引脚

- XY:乘数和被乘数

- CLK:时钟

- Z:计算结果

- RST:重置电路,并加载新的乘数和被乘数

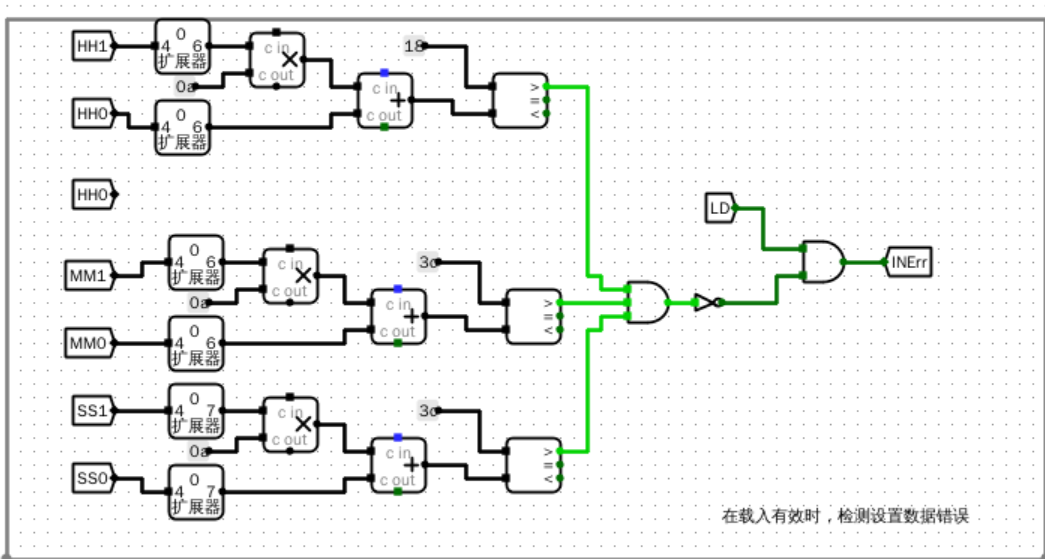

原理图

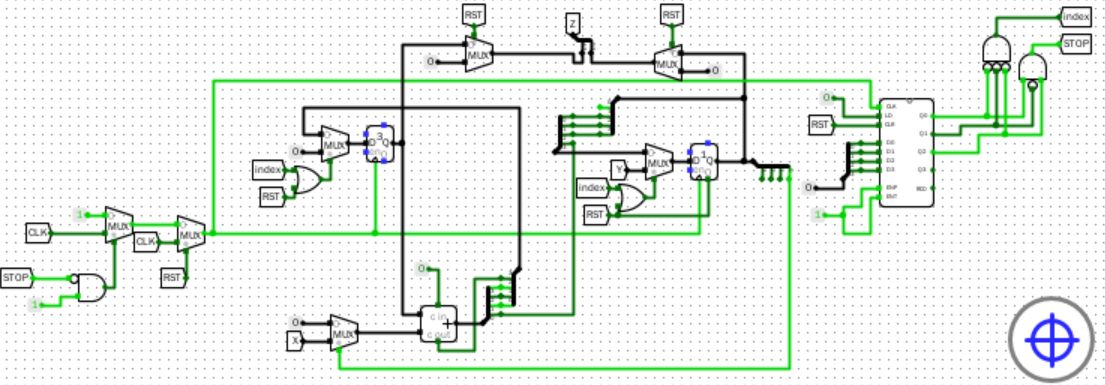

电路图

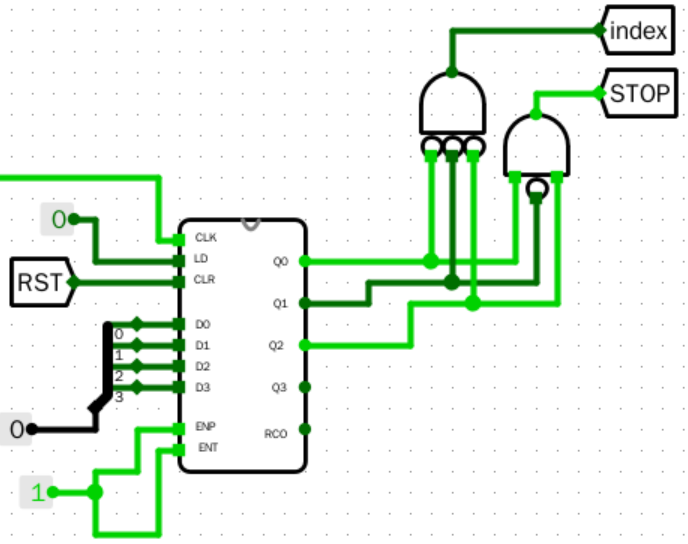

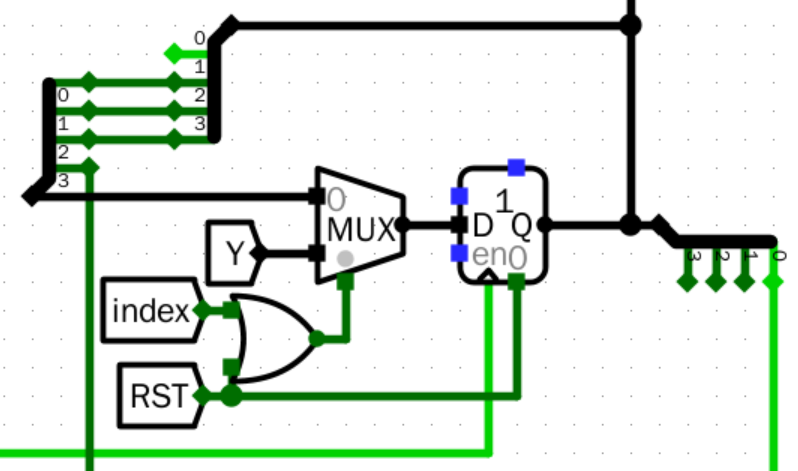

这个图初看容易懵,讲下在做什么

- 计数器

![image]()

我们从0开始计数,所以STOP为1的时候,是我们计数到5的时候,此时就不会再移动位了(最多移动4位) ![image]()

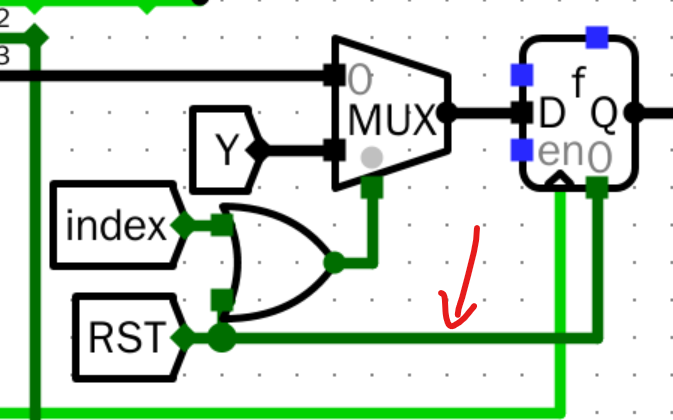

这部分每次将累加结果舍弃掉最低一位,然后与X相加,跟竖式计算有一点不一样。我最开始实现了一个竖式计算的emmm但是没有认真读题,发现题目不能像竖式计算那么做。不知道这是什么原因?像竖式计算那样子做不是更简单更直观吗?![image]()

这部分根据Y的最低位判断是否加上一个X;同时把Y的最高位用来存储上一次累加结果的最低位。这样子做的目的是可以节省空间,最后运算完的时候寄存器里面存储的就是最终的运算结果,于是就可以直接送到Z了![image]()

这一部分就是构造Z,有了前面的讲解这一部分应该不难![image]()

这一部分是控制Reset的

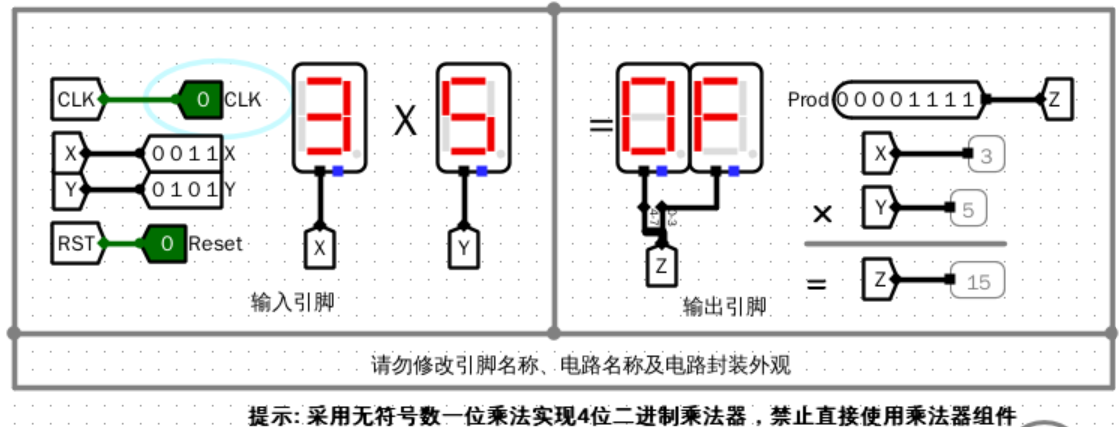

仿真测试

- 3*5=15

![image]()

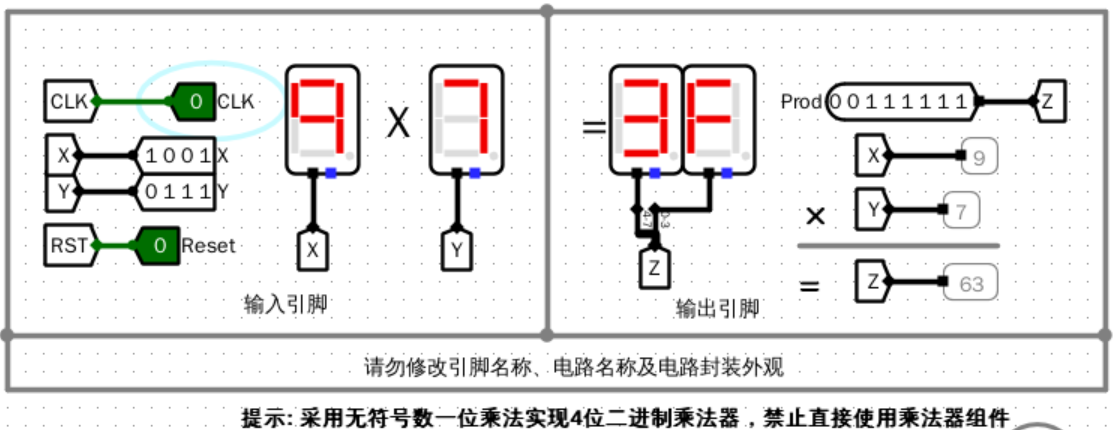

- 9*7=63

![image]()

错误现象及分析

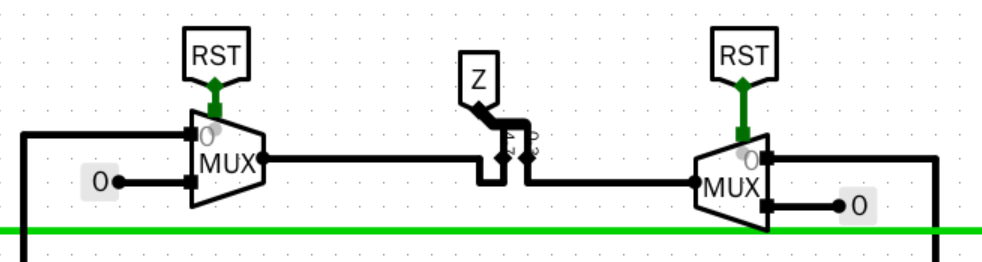

没有考虑清零的问题,最开始设置了RST为1之后再变成0,Z会直接加载成Y;虽然不影响最终结果,但是过不了实验。考虑增加清零功能,只需要在RST为1的时候将寄存器的值变为0就可以了,如下

增加红色箭头指向的这一根线,这样就可以在RST置1的时候将寄存器清零了

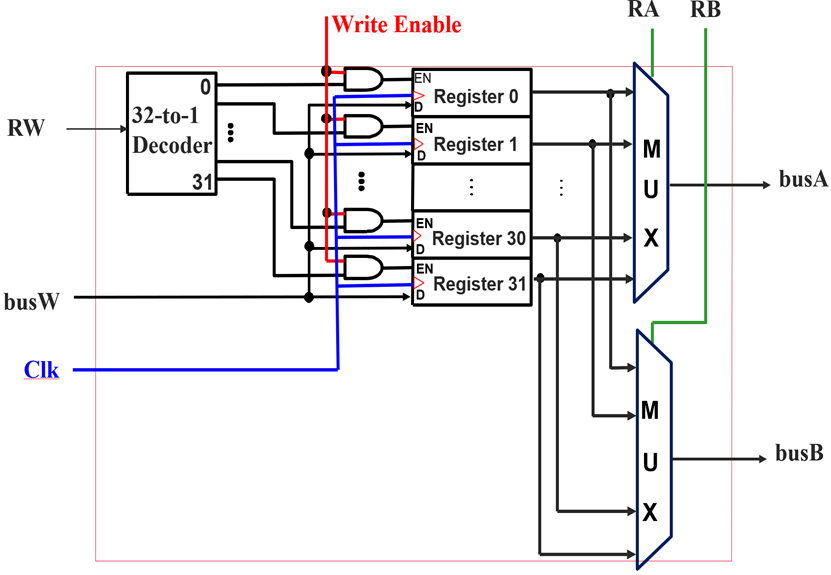

3.4

构建含有32个32位寄存器的寄存器堆Regfile的读写电路,包含两个读数据端口和一个写数据端口,并封装成子电路

整体方案设计

输入输出引脚

- RW:指示要写入的寄存器,经过译码器

- CLK:时钟脉冲

- RA:要读取的寄存器A

- RB:要读取的寄存器B

- RDA:寄存器A的读取结果

- RDB:寄存器B的读取结果

- Din:要写入的数据

- WE:是否开启写入

原理图

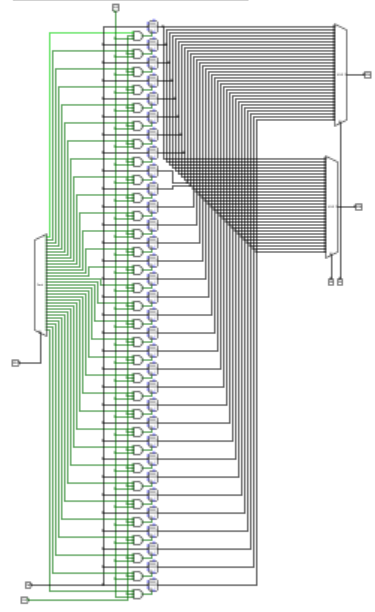

电路图

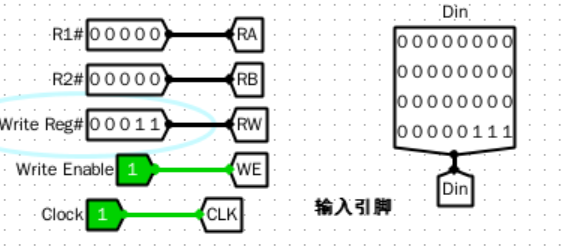

仿真测试

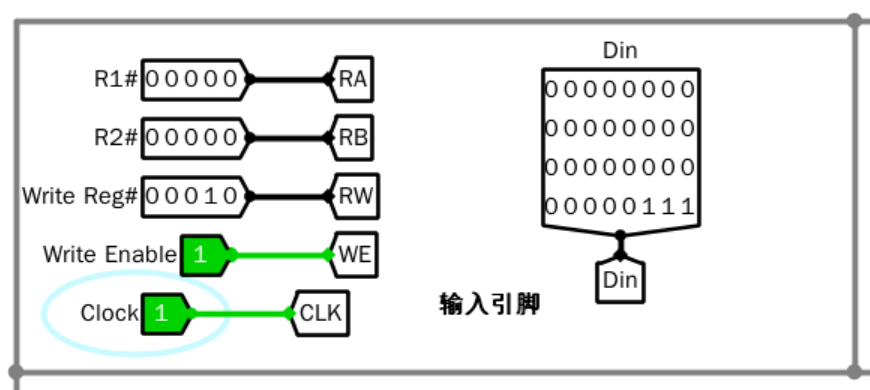

-

将7写入寄存器2

![image]()

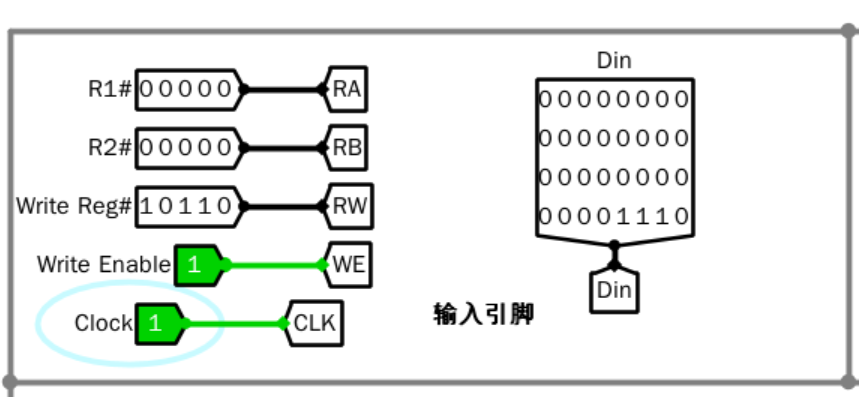

-

13写入寄存器22

![image]()

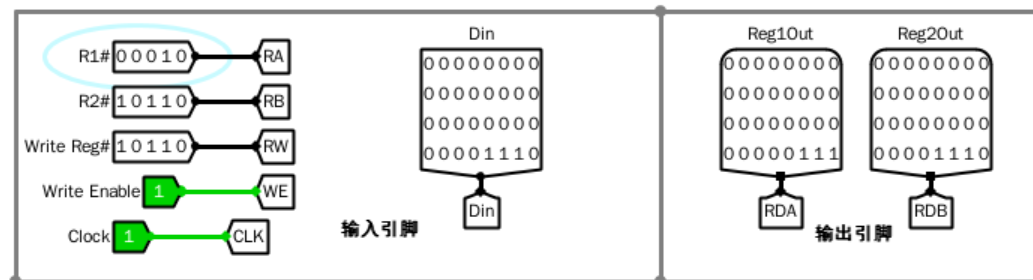

-

读取进行验证

![image]()

下面进行锁存器存储测试

将所有寄存器调整到高电平有效,然后将7写入寄存器1

然后变化寄存器编号到3

可以发现在变化后的一瞬间,寄存器3就存储了7

这实际上是不对的,因为这只是改变了目标寄存器,并没有说就要加载数据了

我们应该把写使能关掉,然后变换寄存器编号,这样就没有问题了

错误现象及分析

这个比较简单,照着原理图进行连接就好了

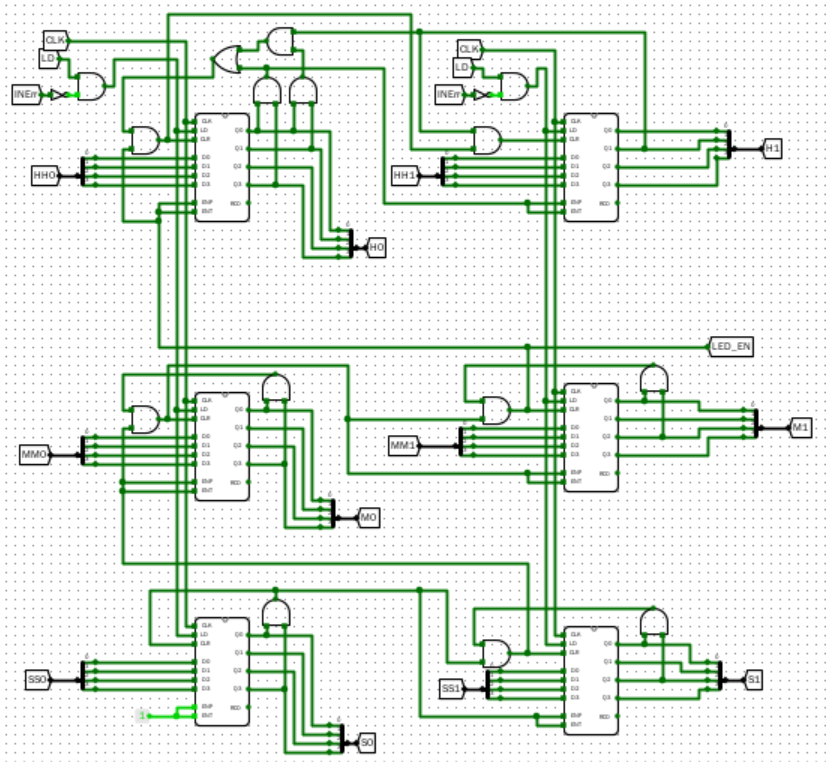

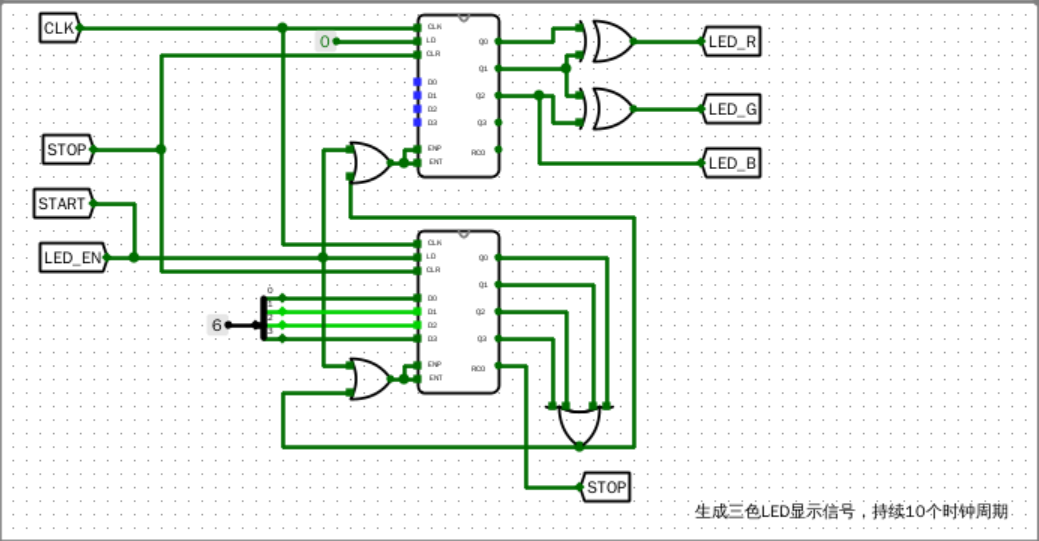

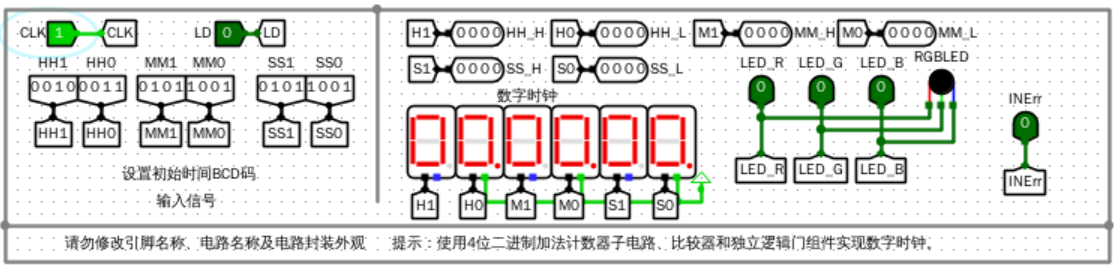

3.5

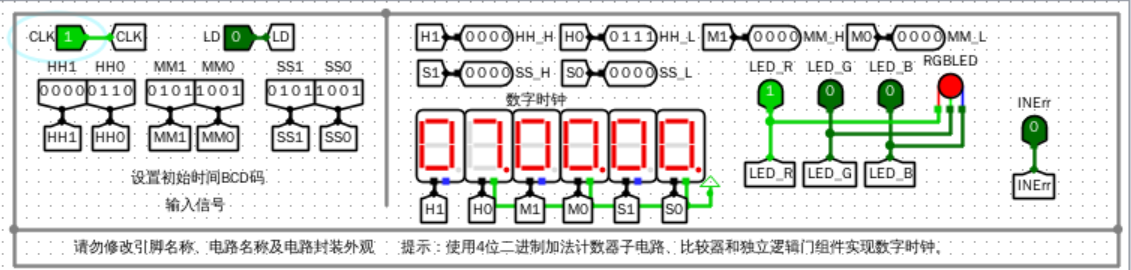

数字时钟实验

整体方案设计

输入输出引脚

- CLK:时钟脉冲

- LD:读取

- hh-sl:输入的初始时间

- h1-s0:当前的时间

电路图

仿真测试

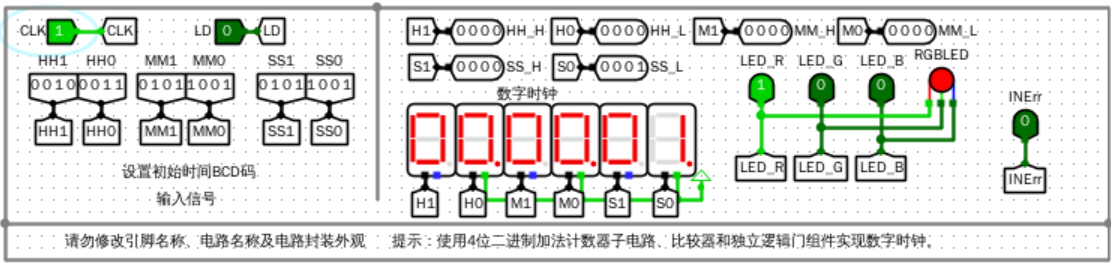

- 23:59:59进位测试:

- 初始状态

![image]()

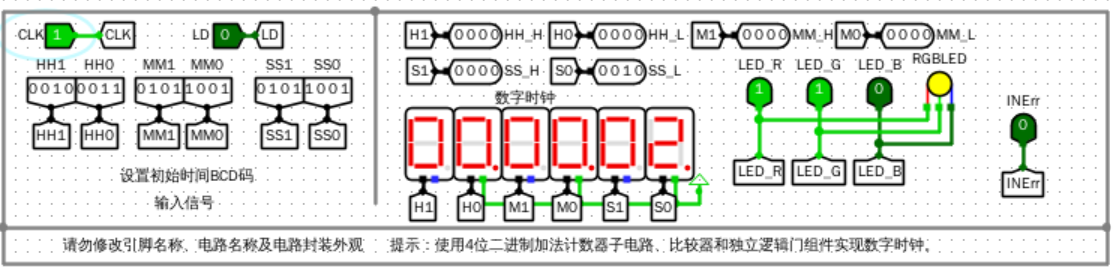

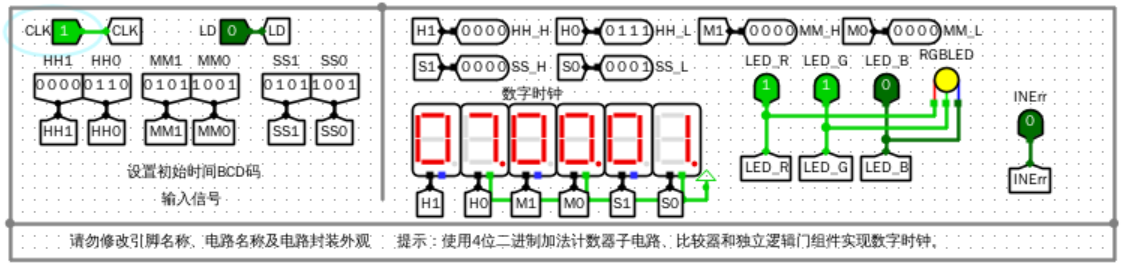

- 进位

![image]()

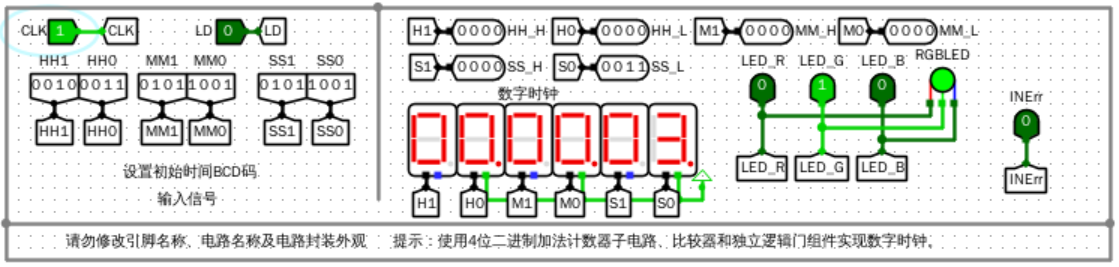

- 继续加

![image]()

![image]()

![image]()

- 初始状态

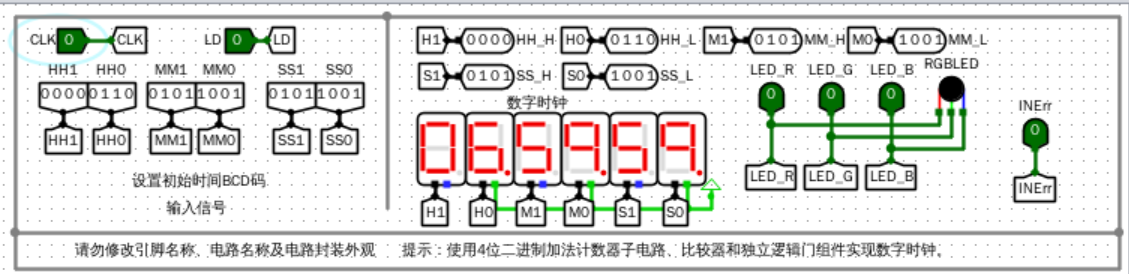

- 整点测试:

- 初始状态

![image]()

- 加一次

![image]()

- 再加一次

![image]()

- 初始状态

错误现象及分析

- 在完成实验的过程中,没有遇到任何错误。

思考题

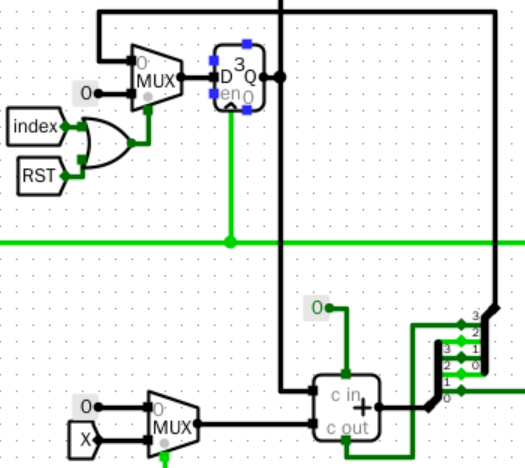

修改同步计数器电路设计,实现异步清零和异步置数的 4 位计数器,并说明该计数器的应用特性

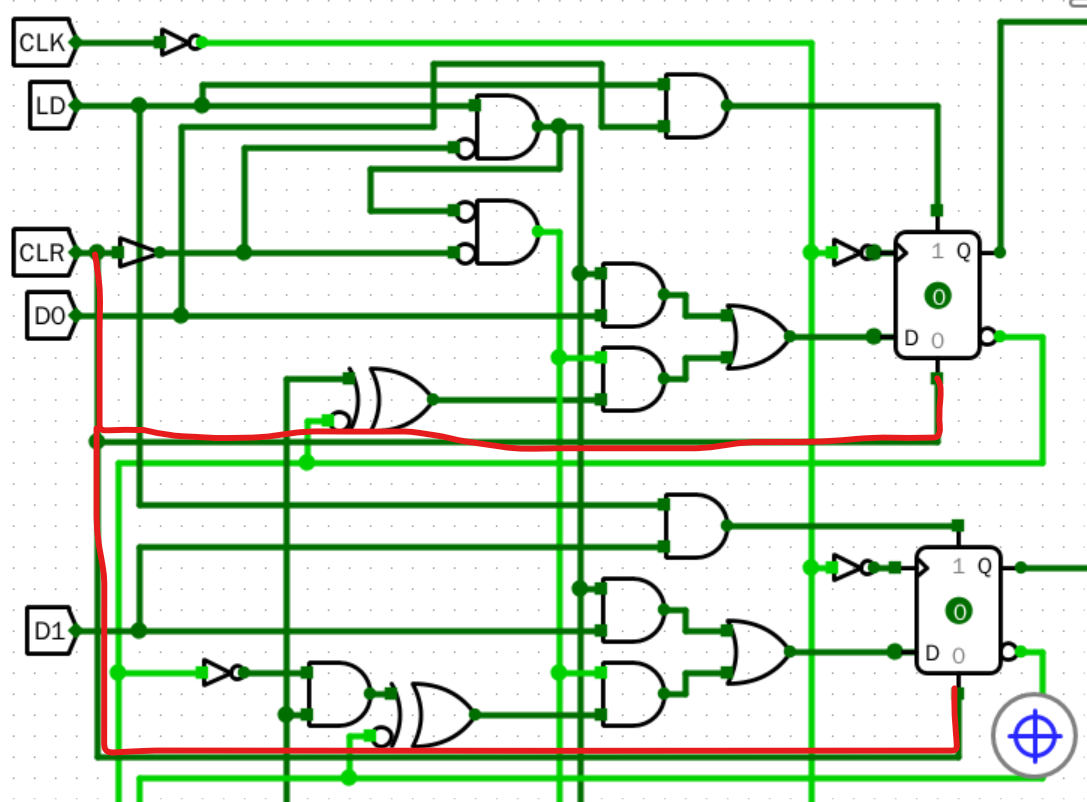

由于D触发器有清零端和置位端,所以我们直接利用这两个端口即可(下面的电路以前两个触发器为例)

- 对于异步清零,我们直接将CLR连接到D触发器的清零端,就无需再等待时钟信号(下图中红线)

![image]()

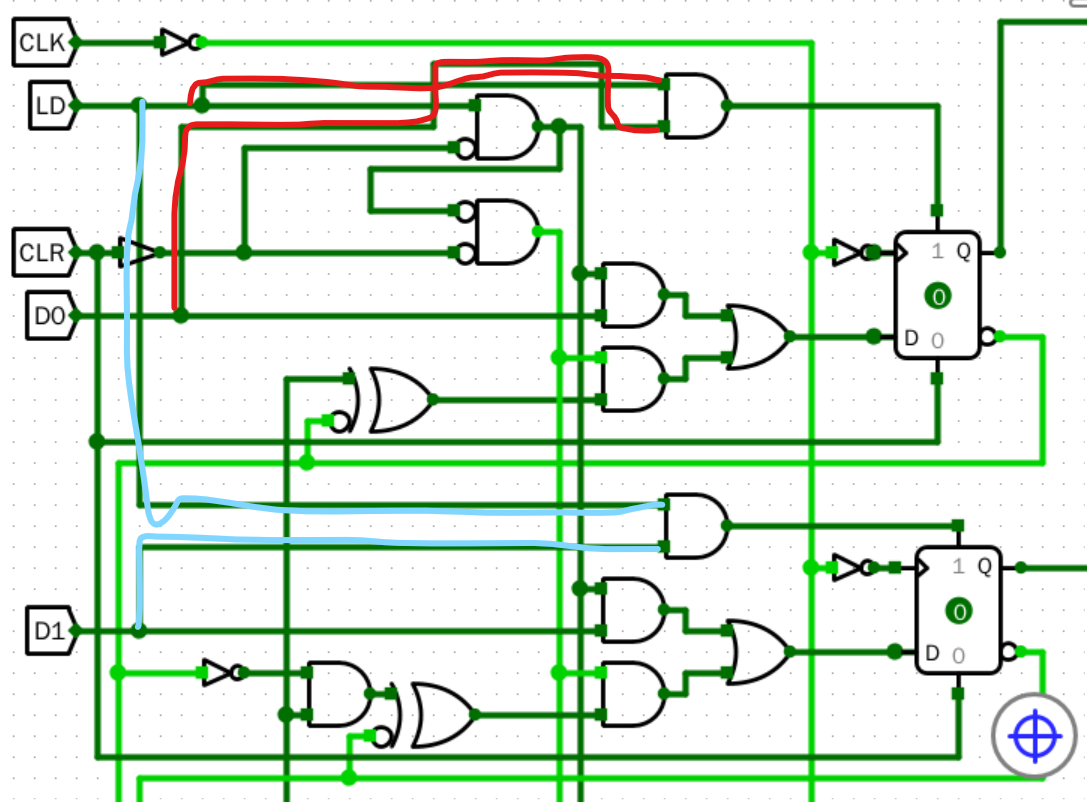

- 对于异步置位,首先LD要为1,在此基础上,第i个触发器取决于Di的值,所以使用一个与门连接即可(下图中的红线和蓝线)

![image]()

如何仅利用4位同步加法计数器在不增加其它逻辑门的情况下,实现模10计数器

由于RCO表示的是是否已经达到最大值,我们将这个最大值设置为10即可

10的二进制表示是1010,取反的0101(以最后两个触发器为例)

- 将连接RCO的与门的反转修改成与0101相适配的情况,于是当计数到10的时候,RCO就变成1

- 将RCO连接到各个触发器的清零端,当RCO为1的时候,就将所有计数器清零

利用 4 位移位寄存器设计 8 位二进制伪随机序列电路,写出输出序列值

前置知识有点多,先介绍一下

这个思考题的目的是生成一个伪随机序列,这个序列的每个值都是0和1

介绍一下反馈多项式。我们必须按照反馈多项式去生成才可以得到伪随机序列,不然的话周期非常短,一下子就陷入了循环

反馈多项式经过严格的证明,我们这里选择\(x^4+x+1\),这里\(x^i\)就代表\(Q_{i-1}\)

所以我们选择的反馈多项式就是\(Q_3\)和\(Q_0\)做异或

具体过程如下(输出序列从 \(Q_0\) 取位)

- 初始状态: 0001, 输出: 1

- 状态: 0011, 输出: 1

- 状态: 0111, 输出: 1

- 状态: 1111, 输出: 1

- 状态: 1110, 输出: 0

- 状态: 1101, 输出: 1

- 状态: 1010, 输出: 0

- 状态: 0101, 输出: 1

最后生成的输出序列值为 11110101

可以看到上面的过程只需要移位寄存器

如何实现寄存器堆的写后读功能

寄存器堆的写后读、功能是指在同一时钟周期内,当写入和读取同一寄存器时,读取操作能够获取到刚刚写入的新值而非旧值

于是我们只需要判断当前的写入地址和读取地址是否相同

如果相同的话,我们需要进行一些处理

具体来说:

- 用一个比较器比较写入地址和读取地址

- 读取不再是直接从目标寄存器中读取,而是从一个多路选择器中读取

- 这个多路选择器有两个输入,分别是目标寄存器和写入值(也就是写入线路分一个分支直接连接到这个多路选择器)

- 如果比较器发现写入地址和读取地址不同,那么多路选择器的输出是目标寄存器的值

- 否则的话是写入值(这里就是写后读)

浙公网安备 33010602011771号

浙公网安备 33010602011771号