实验一

1.1

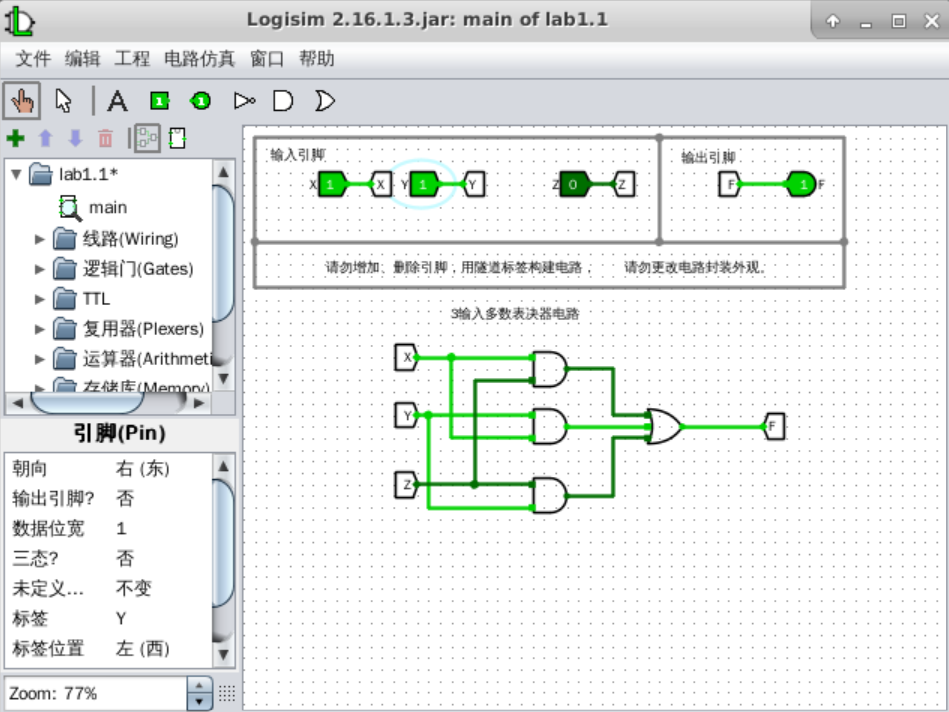

3 输入多数表决器。

整体方案设计

数据

- 输入信号\(XYZ\):三个表决数据

- 输出信号\(F\):输出项,表示多数表决数据

输入输出引脚

需要 3 个输入引脚和 1 个输出引脚

模块

三个与门和一个或门,具体见下

原理图和电路图

原理图

电路图

仿真测试

代表性输入输出

- \(X=1 \ Y=0 \ Z=0\)

- \(X=1 \ Y=1 \ Z=0\)

可以看到都没问题

错误现象及分析

- 没遇到错误

1.2

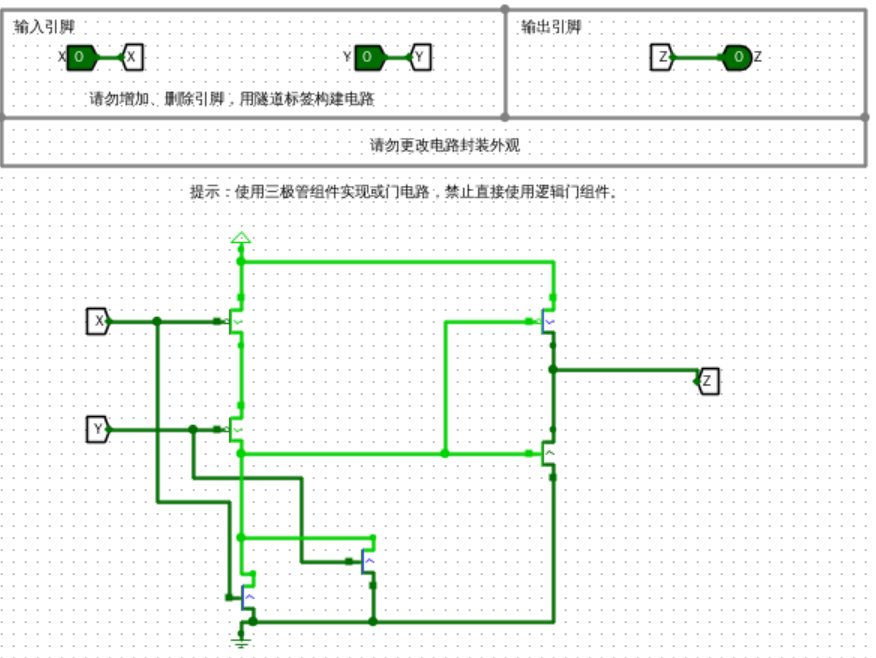

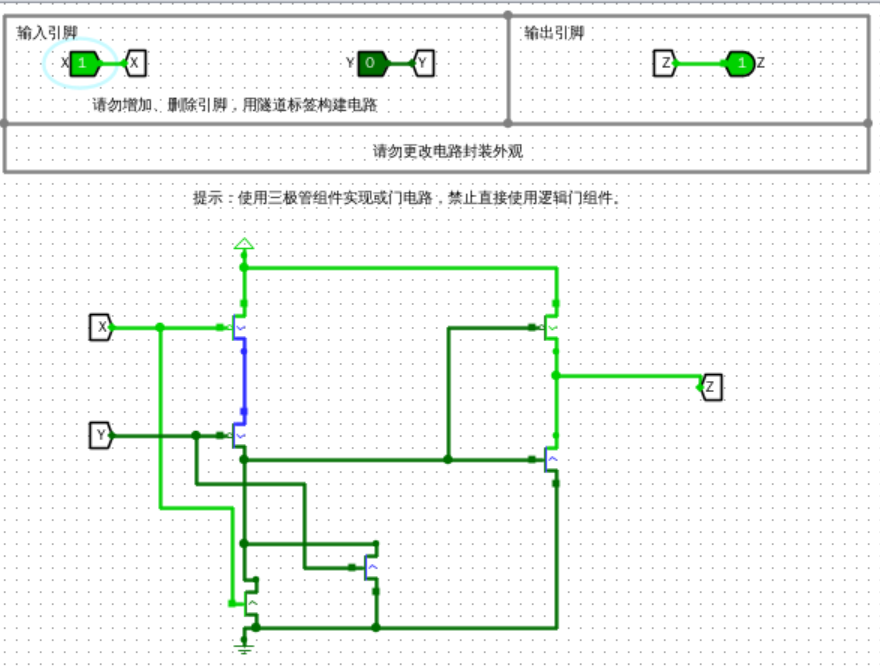

利用 CMOS 晶体管构建两输入或门。

整体方案设计

数据

- \(XY\):两个输入

- \(F\):或结果输出

输入输出引脚

两个输入引脚、1 个输出引脚

模块

3 对 CMOS 晶体管

原理图和电路图

- 原理图

- 电路图

仿真测试

代表性输入输出

- \(X=0 \ Y=0\)

- \(X=1 \ Y=0\)

错误现象及分析

- 没有遇到错误

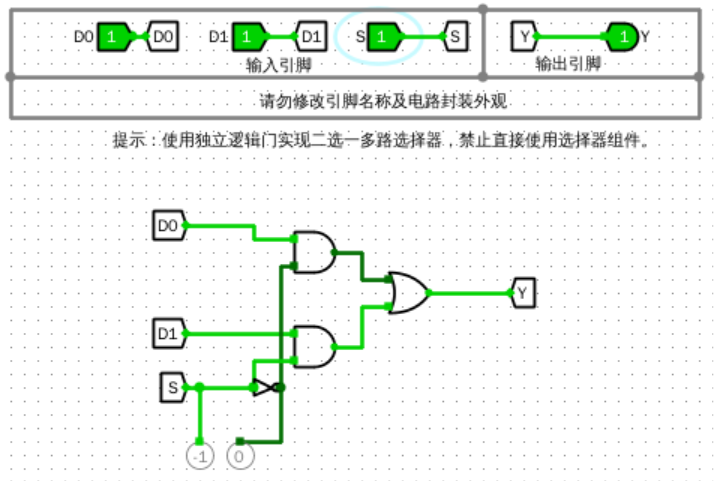

1.3

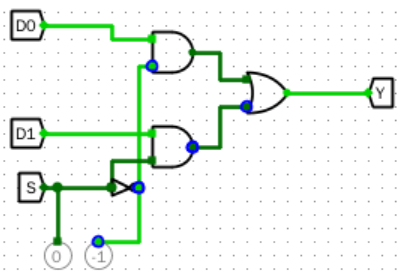

利用基本逻辑门和 CMOS 晶体管实现多路选择器。

整体方案设计

数据

- \(D0,D1\):两个输入端

- \(S\):控制端,用于从D1,D2中选择作为结果

输入输出引脚

3 个输入端和 1 个输出端

部件

两个 2 输入与门、1 个 2 输入或门、1 个非门

原理图和电路图

仿真测试

冒险检测

- 设置\(D_0=D_1=S=1\),观察输出值

![image]()

两个探针处还是保持原状态,分别是 1 和 0,说明非门的输入端并没有随着 S 的改变而立即发生变化 - 第一次单步仿真

![image]()

此时非门输入端发生变化,但其输出端没有立即发生变化 - 第二次单步仿真

![image]()

此时非门输出为 1,但上面的与门的输出没有变化 - 第三次单步仿真

![image]()

- 第四次单步仿真

![image]()

直到第 4 次单步仿真后每个逻辑门才都转变为正确的输入/输出状态

单步仿真过程反映了信号在电路中的延迟情况。第1 次点击进行单步仿真后,经过后续 3 次单步仿真后整个电路得到正确的输入/输出状态,即从输入到输出共经过了非门、与门和或门 3 级逻辑门延迟

错误现象及分析

- 没有遇到错误

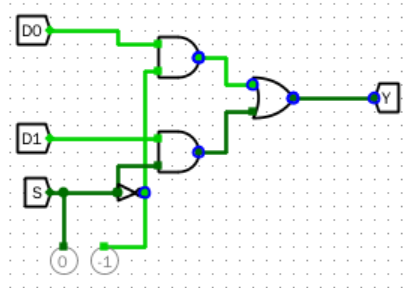

1.4

- 使用传输门实现选择器

整体方案设计

输入输出引脚

- \(D0,D1\):两个输入端

- \(S\):控制端,用于从D1,D2中选择作为结果

原理图和电路图

原理图

电路图

仿真测试

代表性输入输出

- \(D0=1 \ D2=0 \ S=0\)

- \(D0=0 \ D2=1 \ S=1\)

错误现象及分析

没有遇到错误

1.5

整体方案设计

输入输出引脚

- \(D(D0~D3)\):四位输入

- \(S(S0~S1)\):两位控制信号,用于选择输入作为结果

原理图和电路图

- 4-1 MUX

![image]()

- 2-1 MUX

![image]()

仿真测试

代表性输入输出

- \(D=0001 \ S=00\)

- \(D=0100 \ S=01\)

错误现象及分析

没有遇到错误

思考题

根据 2 选 1 多路选择器的与-或电路,替换成与非-与非电路,并分析两种电路的特性。

只需要证明与门,或门和非门都可以通过与非门实现

实际上,我们有:\(\overline{S}=S \text{NAND} S, A+B=\overline{\overline{A}\cdot\overline{B}}=(A\space NAND\space A)\space NAND\space (B \space NAND\space B)A\cdot B=\overline{\overline{A\cdot B}}=\overline{\overline{A}+\overline{B}}\)(然后套入前面一个公式即可)

特性:

- 与-或电路直观,但晶体管数较多导致功耗和面积较高

- 与非-与非电路反之

实现 4 位二进制数转换成格雷码的转换电路。

实现 4 位二进制数的奇偶校验位生成电路。

浙公网安备 33010602011771号

浙公网安备 33010602011771号