lfsr

与上层模块之间的关系

lfsr是一个参数化的组合逻辑并行 LFSR/CRC 模块,支持在单周期内并行处理 DATA_WIDTH 位数据

万兆以太网帧结构以及校验机制如下

而如果我们把FCS也放入CRC校验时,会得到固定结果

下面则是不同情况下crc的固定值,crc_valid[7]代表从MAC开是到FCS结束,crc_valid[6]则是在上面的基础上加一个终止字符校验,crc_valid[5]除了加一个终止字符校验,还加了一个IDLE字符,后面依次类推。但实际值好像有点不对劲,后面试试仿真结果。

这里给出一个仿真:可以看到终止字符在字节1,在蓝色框内,crc_next来自于crc_state和xgmii_rxd_d0的组合逻辑,当前xgmii_rxd_d0中包含fcs(32'hdb7fac5d)和最后四个有效字节(32'h00000063),crc_next为32'hdebb20e3,取反则为32'h2144df1c。

这里给出第二个仿真:可以看到终止字符在字节6,在紫色框内,crc_next来自于crc_state和xgmii_rxd_d0的组合逻辑,当前xgmii_rxd_d0中包含fcs(32'h466535f8)和最后1个有效字节(8'h63),crc_next为32'h62932081,取反则为32'h9d6cdf7e,符合逻辑,这里纠正一下错误,crc_valid判断的crc_next正确值应该是与term_lane_reg的值有关,0代表没有多余8'h00被校验,1则有1个,2则有两个,依次类推。

这里推荐一个公众号的解析

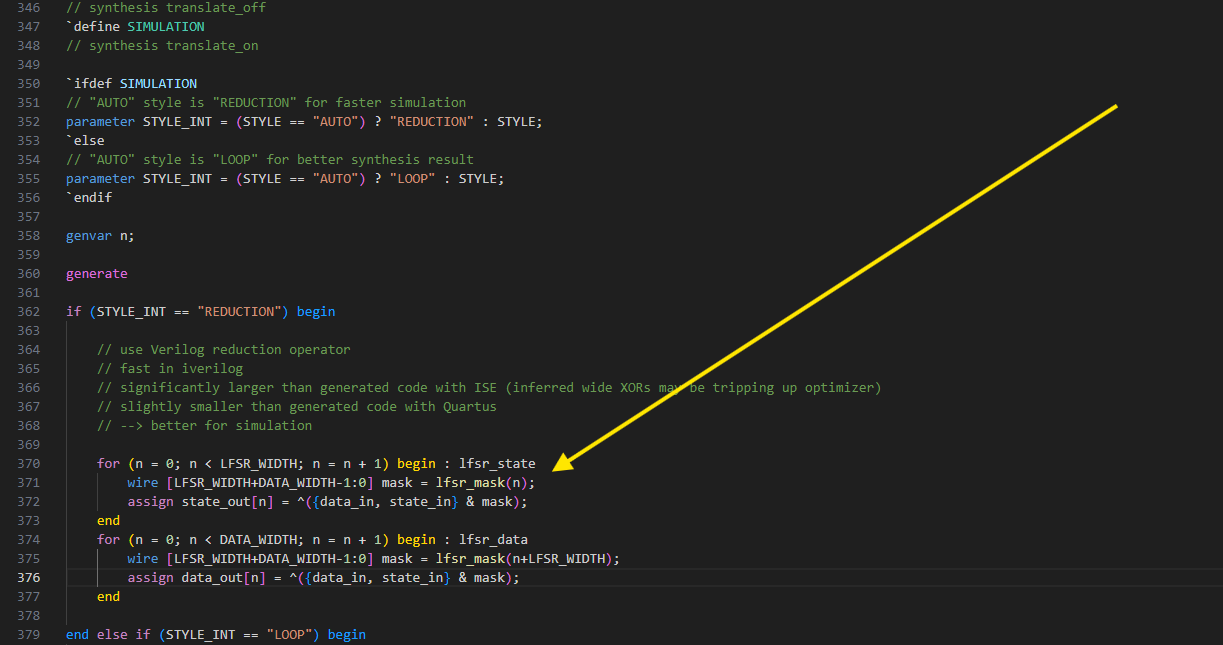

关于lfsr线性反馈移位寄存器,他的难点在于高频高位宽处理下如何满足时序要求。

其中lfsr_mask为矩阵掩膜,有兴趣的可以查阅相关资料,简单来讲state_out的每一位都与data_in和state_in的所有位息息相关,通过掩膜矩阵,可以快速得到state_out的计算结果,降低延迟

还有一种,但这种是串行的,应该会比上一种延迟多很多。

点击查看代码

/*

Copyright (c) 2015-2017 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* AXI4-Stream XGMII frame receiver (XGMII in, AXI out)

*/

module axis_xgmii_rx_64 #

(

parameter DATA_WIDTH = 64,

parameter KEEP_WIDTH = (DATA_WIDTH/8),

parameter CTRL_WIDTH = (DATA_WIDTH/8),

parameter PTP_TS_ENABLE = 0,

parameter PTP_TS_FMT_TOD = 1,

parameter PTP_TS_WIDTH = PTP_TS_FMT_TOD ? 96 : 64,

parameter USER_WIDTH = (PTP_TS_ENABLE ? PTP_TS_WIDTH : 0) + 1

)

(

input wire clk,

input wire rst,

/*

* XGMII input

*/

input wire [DATA_WIDTH-1:0] xgmii_rxd,

input wire [CTRL_WIDTH-1:0] xgmii_rxc,

/*

* AXI output

*/

output wire [DATA_WIDTH-1:0] m_axis_tdata,

output wire [KEEP_WIDTH-1:0] m_axis_tkeep,

output wire m_axis_tvalid,

output wire m_axis_tlast,

output wire [USER_WIDTH-1:0] m_axis_tuser,

/*

* PTP

*/

input wire [PTP_TS_WIDTH-1:0] ptp_ts,

/*

* Configuration

*/

input wire cfg_rx_enable,

/*

* Status

*/

output wire [1:0] start_packet,

output wire error_bad_frame,

output wire error_bad_fcs

);

// bus width assertions

initial begin

if (DATA_WIDTH != 64) begin

$error("Error: Interface width must be 64");

$finish;

end

if (KEEP_WIDTH * 8 != DATA_WIDTH || CTRL_WIDTH * 8 != DATA_WIDTH) begin

$error("Error: Interface requires byte (8-bit) granularity");

$finish;

end

end

localparam [7:0]

ETH_PRE = 8'h55,

ETH_SFD = 8'hD5;

localparam [7:0]

XGMII_IDLE = 8'h07,

XGMII_START = 8'hfb,

XGMII_TERM = 8'hfd,

XGMII_ERROR = 8'hfe;

localparam [1:0]

STATE_IDLE = 2'd0,

STATE_PAYLOAD = 2'd1,

STATE_LAST = 2'd2;

reg [1:0] state_reg = STATE_IDLE, state_next;

// datapath control signals

reg reset_crc;

reg lanes_swapped = 1'b0;

reg [31:0] swap_rxd = 32'd0;

reg [3:0] swap_rxc = 4'd0;

reg [3:0] swap_rxc_term = 4'd0;

reg [DATA_WIDTH-1:0] xgmii_rxd_masked = {DATA_WIDTH{1'b0}};

reg [CTRL_WIDTH-1:0] xgmii_term = {CTRL_WIDTH{1'b0}};

reg [2:0] term_lane_reg = 0, term_lane_d0_reg = 0;

reg term_present_reg = 1'b0;

reg framing_error_reg = 1'b0, framing_error_d0_reg = 1'b0;

reg [DATA_WIDTH-1:0] xgmii_rxd_d0 = {DATA_WIDTH{1'b0}};

reg [DATA_WIDTH-1:0] xgmii_rxd_d1 = {DATA_WIDTH{1'b0}};

reg [CTRL_WIDTH-1:0] xgmii_rxc_d0 = {CTRL_WIDTH{1'b0}};

reg xgmii_start_swap = 1'b0;

reg xgmii_start_d0 = 1'b0;

reg xgmii_start_d1 = 1'b0;

reg [DATA_WIDTH-1:0] m_axis_tdata_reg = {DATA_WIDTH{1'b0}}, m_axis_tdata_next;

reg [KEEP_WIDTH-1:0] m_axis_tkeep_reg = {KEEP_WIDTH{1'b0}}, m_axis_tkeep_next;

reg m_axis_tvalid_reg = 1'b0, m_axis_tvalid_next;

reg m_axis_tlast_reg = 1'b0, m_axis_tlast_next;

reg [USER_WIDTH-1:0] m_axis_tuser_reg = {USER_WIDTH{1'b0}}, m_axis_tuser_next;

reg [1:0] start_packet_reg = 2'b00;

reg error_bad_frame_reg = 1'b0, error_bad_frame_next;

reg error_bad_fcs_reg = 1'b0, error_bad_fcs_next;

reg [PTP_TS_WIDTH-1:0] ptp_ts_reg = 0;

reg [PTP_TS_WIDTH-1:0] ptp_ts_adj_reg = 0;

reg ptp_ts_borrow_reg = 0;

reg [31:0] crc_state = 32'hFFFFFFFF;

wire [31:0] crc_next;

wire [7:0] crc_valid;

reg [7:0] crc_valid_save;

assign crc_valid[7] = crc_next == ~32'h2144df1c;

assign crc_valid[6] = crc_next == ~32'hc622f71d;

assign crc_valid[5] = crc_next == ~32'hb1c2a1a3;

assign crc_valid[4] = crc_next == ~32'h9d6cdf7e;

assign crc_valid[3] = crc_next == ~32'h6522df69;

assign crc_valid[2] = crc_next == ~32'he60914ae;

assign crc_valid[1] = crc_next == ~32'he38a6876;

assign crc_valid[0] = crc_next == ~32'h6b87b1ec;

reg [4+16-1:0] last_ts_reg = 0;

reg [4+16-1:0] ts_inc_reg = 0;

assign m_axis_tdata = m_axis_tdata_reg;

assign m_axis_tkeep = m_axis_tkeep_reg;

assign m_axis_tvalid = m_axis_tvalid_reg;

assign m_axis_tlast = m_axis_tlast_reg;

assign m_axis_tuser = m_axis_tuser_reg;

assign start_packet = start_packet_reg;

assign error_bad_frame = error_bad_frame_reg;

assign error_bad_fcs = error_bad_fcs_reg;

lfsr #(

.LFSR_WIDTH(32),

.LFSR_POLY(32'h4c11db7),

.LFSR_CONFIG("GALOIS"),

.LFSR_FEED_FORWARD(0),

.REVERSE(1),

.DATA_WIDTH(64),

.STYLE("AUTO")

)

eth_crc (

.data_in(xgmii_rxd_d0),

.state_in(crc_state),

.data_out(),

.state_out(crc_next)

);

// Mask input data

integer j;

always @* begin

for (j = 0; j < 8; j = j + 1) begin

xgmii_rxd_masked[j*8 +: 8] = xgmii_rxc[j] ? 8'd0 : xgmii_rxd[j*8 +: 8];

xgmii_term[j] = xgmii_rxc[j] && (xgmii_rxd[j*8 +: 8] == XGMII_TERM);

end

end

always @* begin

state_next = STATE_IDLE;

reset_crc = 1'b0;

m_axis_tdata_next = xgmii_rxd_d1;

m_axis_tkeep_next = {KEEP_WIDTH{1'b1}};

m_axis_tvalid_next = 1'b0;

m_axis_tlast_next = 1'b0;

m_axis_tuser_next = m_axis_tuser_reg;

m_axis_tuser_next[0] = 1'b0;

error_bad_frame_next = 1'b0;

error_bad_fcs_next = 1'b0;

case (state_reg)

STATE_IDLE: begin

// idle state - wait for packet

reset_crc = 1'b1;

if (xgmii_start_d1 && cfg_rx_enable) begin

// start condition

reset_crc = 1'b0;

state_next = STATE_PAYLOAD;

end else begin

state_next = STATE_IDLE;

end

end

STATE_PAYLOAD: begin

// read payload

m_axis_tdata_next = xgmii_rxd_d1;

m_axis_tkeep_next = {KEEP_WIDTH{1'b1}};

m_axis_tvalid_next = 1'b1;

m_axis_tlast_next = 1'b0;

m_axis_tuser_next[0] = 1'b0;

if (PTP_TS_ENABLE) begin

m_axis_tuser_next[1 +: PTP_TS_WIDTH] = (!PTP_TS_FMT_TOD || ptp_ts_borrow_reg) ? ptp_ts_reg : ptp_ts_adj_reg;

end

if (framing_error_reg || framing_error_d0_reg) begin

// control or error characters in packet

m_axis_tlast_next = 1'b1;

m_axis_tuser_next[0] = 1'b1;

error_bad_frame_next = 1'b1;

reset_crc = 1'b1;

state_next = STATE_IDLE;

end else if (term_present_reg) begin

reset_crc = 1'b1;

if (term_lane_reg <= 4) begin

// end this cycle

m_axis_tkeep_next = {KEEP_WIDTH{1'b1}} >> (CTRL_WIDTH-4-term_lane_reg);

m_axis_tlast_next = 1'b1;

if ((term_lane_reg == 0 && crc_valid_save[7]) ||

(term_lane_reg == 1 && crc_valid[0]) ||

(term_lane_reg == 2 && crc_valid[1]) ||

(term_lane_reg == 3 && crc_valid[2]) ||

(term_lane_reg == 4 && crc_valid[3])) begin

// CRC valid

end else begin

m_axis_tuser_next[0] = 1'b1;

error_bad_frame_next = 1'b1;

error_bad_fcs_next = 1'b1;

end

state_next = STATE_IDLE;

end else begin

// need extra cycle

state_next = STATE_LAST;

end

end else begin

state_next = STATE_PAYLOAD;

end

end

STATE_LAST: begin

// last cycle of packet

m_axis_tdata_next = xgmii_rxd_d1;

m_axis_tkeep_next = {KEEP_WIDTH{1'b1}} >> (CTRL_WIDTH+4-term_lane_d0_reg);

m_axis_tvalid_next = 1'b1;

m_axis_tlast_next = 1'b1;

m_axis_tuser_next[0] = 1'b0;

reset_crc = 1'b1;

if ((term_lane_d0_reg == 5 && crc_valid_save[4]) ||

(term_lane_d0_reg == 6 && crc_valid_save[5]) ||

(term_lane_d0_reg == 7 && crc_valid_save[6])) begin

// CRC valid

end else begin

m_axis_tuser_next[0] = 1'b1;

error_bad_frame_next = 1'b1;

error_bad_fcs_next = 1'b1;

end

if (xgmii_start_d1 && cfg_rx_enable) begin

// start condition

reset_crc = 1'b0;

state_next = STATE_PAYLOAD;

end else begin

state_next = STATE_IDLE;

end

end

endcase

end

integer i;

always @(posedge clk) begin

state_reg <= state_next;

m_axis_tdata_reg <= m_axis_tdata_next;

m_axis_tkeep_reg <= m_axis_tkeep_next;

m_axis_tvalid_reg <= m_axis_tvalid_next;

m_axis_tlast_reg <= m_axis_tlast_next;

m_axis_tuser_reg <= m_axis_tuser_next;

start_packet_reg <= 2'b00;

error_bad_frame_reg <= error_bad_frame_next;

error_bad_fcs_reg <= error_bad_fcs_next;

swap_rxd <= xgmii_rxd_masked[63:32];

swap_rxc <= xgmii_rxc[7:4];

swap_rxc_term <= xgmii_term[7:4];

xgmii_start_swap <= 1'b0;

xgmii_start_d0 <= xgmii_start_swap;

if (PTP_TS_ENABLE && PTP_TS_FMT_TOD) begin

// ns field rollover

ptp_ts_adj_reg[15:0] <= ptp_ts_reg[15:0];

{ptp_ts_borrow_reg, ptp_ts_adj_reg[45:16]} <= $signed({1'b0, ptp_ts_reg[45:16]}) - $signed(31'd1000000000);

ptp_ts_adj_reg[47:46] <= 0;

ptp_ts_adj_reg[95:48] <= ptp_ts_reg[95:48] + 1;

end

// lane swapping and termination character detection

if (lanes_swapped) begin

xgmii_rxd_d0 <= {xgmii_rxd_masked[31:0], swap_rxd};

xgmii_rxc_d0 <= {xgmii_rxc[3:0], swap_rxc};

term_lane_reg <= 0;

term_present_reg <= 1'b0;

framing_error_reg <= {xgmii_rxc[3:0], swap_rxc} != 0;

for (i = CTRL_WIDTH-1; i >= 0; i = i - 1) begin

if ({xgmii_term[3:0], swap_rxc_term} & (1 << i)) begin

term_lane_reg <= i;

term_present_reg <= 1'b1;

framing_error_reg <= ({xgmii_rxc[3:0], swap_rxc} & ({CTRL_WIDTH{1'b1}} >> (CTRL_WIDTH-i))) != 0;

lanes_swapped <= 1'b0;

end

end

end else begin

xgmii_rxd_d0 <= xgmii_rxd_masked;

xgmii_rxc_d0 <= xgmii_rxc;

term_lane_reg <= 0;

term_present_reg <= 1'b0;

framing_error_reg <= xgmii_rxc != 0;

for (i = CTRL_WIDTH-1; i >= 0; i = i - 1) begin

if (xgmii_rxc[i] && (xgmii_rxd[i*8 +: 8] == XGMII_TERM)) begin

term_lane_reg <= i;

term_present_reg <= 1'b1;

framing_error_reg <= (xgmii_rxc & ({CTRL_WIDTH{1'b1}} >> (CTRL_WIDTH-i))) != 0;

lanes_swapped <= 1'b0;

end

end

end

// start control character detection

if (xgmii_rxc[0] && xgmii_rxd[7:0] == XGMII_START) begin

lanes_swapped <= 1'b0;

xgmii_start_d0 <= 1'b1;

term_lane_reg <= 0;

term_present_reg <= 1'b0;

framing_error_reg <= xgmii_rxc[7:1] != 0;

end else if (xgmii_rxc[4] && xgmii_rxd[39:32] == XGMII_START) begin

lanes_swapped <= 1'b1;

xgmii_start_swap <= 1'b1;

term_lane_reg <= 0;

term_present_reg <= 1'b0;

framing_error_reg <= xgmii_rxc[7:5] != 0;

end

// capture timestamps

if (xgmii_start_swap) begin

start_packet_reg <= 2'b10;

if (PTP_TS_FMT_TOD) begin

ptp_ts_reg[45:0] <= ptp_ts[45:0] + (ts_inc_reg >> 1);

ptp_ts_reg[95:48] <= ptp_ts[95:48];

end else begin

ptp_ts_reg <= ptp_ts + (ts_inc_reg >> 1);

end

end

if (xgmii_start_d0) begin

if (!lanes_swapped) begin

start_packet_reg <= 2'b01;

ptp_ts_reg <= ptp_ts;

end

end

term_lane_d0_reg <= term_lane_reg;

framing_error_d0_reg <= framing_error_reg;

if (reset_crc) begin

crc_state <= 32'hFFFFFFFF;

end else begin

crc_state <= crc_next;

end

crc_valid_save <= crc_valid;

xgmii_rxd_d1 <= xgmii_rxd_d0;

xgmii_start_d1 <= xgmii_start_d0;

last_ts_reg <= ptp_ts;

ts_inc_reg <= ptp_ts - last_ts_reg;

if (rst) begin

state_reg <= STATE_IDLE;

m_axis_tvalid_reg <= 1'b0;

start_packet_reg <= 2'b00;

error_bad_frame_reg <= 1'b0;

error_bad_fcs_reg <= 1'b0;

xgmii_rxc_d0 <= {CTRL_WIDTH{1'b0}};

xgmii_start_swap <= 1'b0;

xgmii_start_d0 <= 1'b0;

xgmii_start_d1 <= 1'b0;

lanes_swapped <= 1'b0;

end

end

endmodule

`resetall

点击查看代码

/*

Copyright (c) 2015-2017 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* AXI4-Stream XGMII frame transmitter (AXI in, XGMII out)

*/

module axis_xgmii_tx_64 #

(

parameter DATA_WIDTH = 64,

parameter KEEP_WIDTH = (DATA_WIDTH/8),

parameter CTRL_WIDTH = (DATA_WIDTH/8),

parameter ENABLE_PADDING = 1,

parameter ENABLE_DIC = 1,

parameter MIN_FRAME_LENGTH = 64,

parameter PTP_TS_ENABLE = 0,

parameter PTP_TS_FMT_TOD = 1,

parameter PTP_TS_WIDTH = PTP_TS_FMT_TOD ? 96 : 64,

parameter PTP_TS_CTRL_IN_TUSER = 0,

parameter PTP_TAG_ENABLE = PTP_TS_ENABLE,

parameter PTP_TAG_WIDTH = 16,

parameter USER_WIDTH = (PTP_TS_ENABLE ? (PTP_TAG_ENABLE ? PTP_TAG_WIDTH : 0) + (PTP_TS_CTRL_IN_TUSER ? 1 : 0) : 0) + 1

)

(

input wire clk,

input wire rst,

/*

* AXI input

*/

input wire [DATA_WIDTH-1:0] s_axis_tdata,

input wire [KEEP_WIDTH-1:0] s_axis_tkeep,

input wire s_axis_tvalid,

output wire s_axis_tready,

input wire s_axis_tlast,

input wire [USER_WIDTH-1:0] s_axis_tuser,

/*

* XGMII output

*/

output wire [DATA_WIDTH-1:0] xgmii_txd,

output wire [CTRL_WIDTH-1:0] xgmii_txc,

/*

* PTP

*/

input wire [PTP_TS_WIDTH-1:0] ptp_ts,

output wire [PTP_TS_WIDTH-1:0] m_axis_ptp_ts,

output wire [PTP_TAG_WIDTH-1:0] m_axis_ptp_ts_tag,

output wire m_axis_ptp_ts_valid,

/*

* Configuration

*/

input wire [7:0] cfg_ifg,

input wire cfg_tx_enable,

/*

* Status

*/

output wire [1:0] start_packet,

output wire error_underflow

);

parameter EMPTY_WIDTH = $clog2(KEEP_WIDTH);

parameter MIN_LEN_WIDTH = $clog2(MIN_FRAME_LENGTH-4-CTRL_WIDTH+1);

// bus width assertions

initial begin

if (DATA_WIDTH != 64) begin

$error("Error: Interface width must be 64");

$finish;

end

if (KEEP_WIDTH * 8 != DATA_WIDTH || CTRL_WIDTH * 8 != DATA_WIDTH) begin

$error("Error: Interface requires byte (8-bit) granularity");

$finish;

end

end

localparam [7:0]

ETH_PRE = 8'h55,

ETH_SFD = 8'hD5;

localparam [7:0]

XGMII_IDLE = 8'h07,

XGMII_START = 8'hfb,

XGMII_TERM = 8'hfd,

XGMII_ERROR = 8'hfe;

localparam [2:0]

STATE_IDLE = 3'd0,

STATE_PAYLOAD = 3'd1,

STATE_PAD = 3'd2,

STATE_FCS_1 = 3'd3,

STATE_FCS_2 = 3'd4,

STATE_ERR = 3'd5,

STATE_IFG = 3'd6;

reg [2:0] state_reg = STATE_IDLE, state_next;

// datapath control signals

reg reset_crc;

reg update_crc;

reg swap_lanes_reg = 1'b0, swap_lanes_next;

reg [31:0] swap_txd = 32'd0;

reg [3:0] swap_txc = 4'd0;

reg [DATA_WIDTH-1:0] s_axis_tdata_masked;

reg [DATA_WIDTH-1:0] s_tdata_reg = 0, s_tdata_next;

reg [EMPTY_WIDTH-1:0] s_empty_reg = 0, s_empty_next;

reg [DATA_WIDTH-1:0] fcs_output_txd_0;

reg [DATA_WIDTH-1:0] fcs_output_txd_1;

reg [CTRL_WIDTH-1:0] fcs_output_txc_0;

reg [CTRL_WIDTH-1:0] fcs_output_txc_1;

reg [7:0] ifg_offset;

reg frame_start_reg = 1'b0, frame_start_next;

reg frame_reg = 1'b0, frame_next;

reg frame_error_reg = 1'b0, frame_error_next;

reg [MIN_LEN_WIDTH-1:0] frame_min_count_reg = 0, frame_min_count_next;

reg [7:0] ifg_count_reg = 8'd0, ifg_count_next;

reg [1:0] deficit_idle_count_reg = 2'd0, deficit_idle_count_next;

reg s_axis_tready_reg = 1'b0, s_axis_tready_next;

reg [PTP_TS_WIDTH-1:0] m_axis_ptp_ts_reg = 0;

reg [PTP_TS_WIDTH-1:0] m_axis_ptp_ts_adj_reg = 0;

reg [PTP_TAG_WIDTH-1:0] m_axis_ptp_ts_tag_reg = 0;

reg m_axis_ptp_ts_valid_reg = 1'b0;

reg m_axis_ptp_ts_valid_int_reg = 1'b0;

reg m_axis_ptp_ts_borrow_reg = 1'b0;

reg [31:0] crc_state_reg[7:0];

wire [31:0] crc_state_next[7:0];

reg [4+16-1:0] last_ts_reg = 0;

reg [4+16-1:0] ts_inc_reg = 0;

reg [DATA_WIDTH-1:0] xgmii_txd_reg = {CTRL_WIDTH{XGMII_IDLE}}, xgmii_txd_next;

reg [CTRL_WIDTH-1:0] xgmii_txc_reg = {CTRL_WIDTH{1'b1}}, xgmii_txc_next;

reg start_packet_reg = 2'b00;

reg error_underflow_reg = 1'b0, error_underflow_next;

assign s_axis_tready = s_axis_tready_reg;

assign xgmii_txd = xgmii_txd_reg;

assign xgmii_txc = xgmii_txc_reg;

assign m_axis_ptp_ts = PTP_TS_ENABLE ? ((!PTP_TS_FMT_TOD || m_axis_ptp_ts_borrow_reg) ? m_axis_ptp_ts_reg : m_axis_ptp_ts_adj_reg) : 0;

assign m_axis_ptp_ts_tag = PTP_TAG_ENABLE ? m_axis_ptp_ts_tag_reg : 0;

assign m_axis_ptp_ts_valid = PTP_TS_ENABLE || PTP_TAG_ENABLE ? m_axis_ptp_ts_valid_reg : 1'b0;

assign start_packet = start_packet_reg;

assign error_underflow = error_underflow_reg;

generate

genvar n;

for (n = 0; n < 8; n = n + 1) begin : crc

lfsr #(

.LFSR_WIDTH(32),

.LFSR_POLY(32'h4c11db7),

.LFSR_CONFIG("GALOIS"),

.LFSR_FEED_FORWARD(0),

.REVERSE(1),

.DATA_WIDTH(8*(n+1)),

.STYLE("AUTO")

)

eth_crc (

.data_in(s_tdata_reg[0 +: 8*(n+1)]),

.state_in(crc_state_reg[7]),

.data_out(),

.state_out(crc_state_next[n])

);

end

endgenerate

function [2:0] keep2empty;

input [7:0] k;

casez (k)

8'bzzzzzzz0: keep2empty = 3'd7;

8'bzzzzzz01: keep2empty = 3'd7;

8'bzzzzz011: keep2empty = 3'd6;

8'bzzzz0111: keep2empty = 3'd5;

8'bzzz01111: keep2empty = 3'd4;

8'bzz011111: keep2empty = 3'd3;

8'bz0111111: keep2empty = 3'd2;

8'b01111111: keep2empty = 3'd1;

8'b11111111: keep2empty = 3'd0;

endcase

endfunction

// Mask input data

integer j;

always @* begin

for (j = 0; j < 8; j = j + 1) begin

s_axis_tdata_masked[j*8 +: 8] = s_axis_tkeep[j] ? s_axis_tdata[j*8 +: 8] : 8'd0;

end

end

// FCS cycle calculation

always @* begin

casez (s_empty_reg)

3'd7: begin

fcs_output_txd_0 = {{2{XGMII_IDLE}}, XGMII_TERM, ~crc_state_next[0][31:0], s_tdata_reg[7:0]};

fcs_output_txd_1 = {8{XGMII_IDLE}};

fcs_output_txc_0 = 8'b11100000;

fcs_output_txc_1 = 8'b11111111;

ifg_offset = 8'd3;

end

3'd6: begin

fcs_output_txd_0 = {XGMII_IDLE, XGMII_TERM, ~crc_state_next[1][31:0], s_tdata_reg[15:0]};

fcs_output_txd_1 = {8{XGMII_IDLE}};

fcs_output_txc_0 = 8'b11000000;

fcs_output_txc_1 = 8'b11111111;

ifg_offset = 8'd2;

end

3'd5: begin

fcs_output_txd_0 = {XGMII_TERM, ~crc_state_next[2][31:0], s_tdata_reg[23:0]};

fcs_output_txd_1 = {8{XGMII_IDLE}};

fcs_output_txc_0 = 8'b10000000;

fcs_output_txc_1 = 8'b11111111;

ifg_offset = 8'd1;

end

3'd4: begin

fcs_output_txd_0 = {~crc_state_next[3][31:0], s_tdata_reg[31:0]};

fcs_output_txd_1 = {{7{XGMII_IDLE}}, XGMII_TERM};

fcs_output_txc_0 = 8'b00000000;

fcs_output_txc_1 = 8'b11111111;

ifg_offset = 8'd8;

end

3'd3: begin

fcs_output_txd_0 = {~crc_state_next[4][23:0], s_tdata_reg[39:0]};

fcs_output_txd_1 = {{6{XGMII_IDLE}}, XGMII_TERM, ~crc_state_reg[4][31:24]};

fcs_output_txc_0 = 8'b00000000;

fcs_output_txc_1 = 8'b11111110;

ifg_offset = 8'd7;

end

3'd2: begin

fcs_output_txd_0 = {~crc_state_next[5][15:0], s_tdata_reg[47:0]};

fcs_output_txd_1 = {{5{XGMII_IDLE}}, XGMII_TERM, ~crc_state_reg[5][31:16]};

fcs_output_txc_0 = 8'b00000000;

fcs_output_txc_1 = 8'b11111100;

ifg_offset = 8'd6;

end

3'd1: begin

fcs_output_txd_0 = {~crc_state_next[6][7:0], s_tdata_reg[55:0]};

fcs_output_txd_1 = {{4{XGMII_IDLE}}, XGMII_TERM, ~crc_state_reg[6][31:8]};

fcs_output_txc_0 = 8'b00000000;

fcs_output_txc_1 = 8'b11111000;

ifg_offset = 8'd5;

end

3'd0: begin

fcs_output_txd_0 = s_tdata_reg;

fcs_output_txd_1 = {{3{XGMII_IDLE}}, XGMII_TERM, ~crc_state_reg[7][31:0]};

fcs_output_txc_0 = 8'b00000000;

fcs_output_txc_1 = 8'b11110000;

ifg_offset = 8'd4;

end

endcase

end

always @* begin

state_next = STATE_IDLE;

reset_crc = 1'b0;

update_crc = 1'b0;

swap_lanes_next = swap_lanes_reg;

frame_start_next = 1'b0;

frame_next = frame_reg;

frame_error_next = frame_error_reg;

frame_min_count_next = frame_min_count_reg;

ifg_count_next = ifg_count_reg;

deficit_idle_count_next = deficit_idle_count_reg;

s_axis_tready_next = 1'b0;

s_tdata_next = s_tdata_reg;

s_empty_next = s_empty_reg;

// XGMII idle

xgmii_txd_next = {CTRL_WIDTH{XGMII_IDLE}};

xgmii_txc_next = {CTRL_WIDTH{1'b1}};

error_underflow_next = 1'b0;

if (s_axis_tvalid && s_axis_tready) begin

frame_next = !s_axis_tlast;

end

case (state_reg)

STATE_IDLE: begin

// idle state - wait for data

frame_error_next = 1'b0;

frame_min_count_next = MIN_FRAME_LENGTH-4-CTRL_WIDTH;

reset_crc = 1'b1;

s_axis_tready_next = cfg_tx_enable;

// XGMII idle

xgmii_txd_next = {CTRL_WIDTH{XGMII_IDLE}};

xgmii_txc_next = {CTRL_WIDTH{1'b1}};

s_tdata_next = s_axis_tdata_masked;

s_empty_next = keep2empty(s_axis_tkeep);

if (s_axis_tvalid && s_axis_tready) begin

// XGMII start, preamble, and SFD

xgmii_txd_next = {ETH_SFD, {6{ETH_PRE}}, XGMII_START};

xgmii_txc_next = 8'b00000001;

frame_start_next = 1'b1;

s_axis_tready_next = 1'b1;

state_next = STATE_PAYLOAD;

end else begin

swap_lanes_next = 1'b0;

ifg_count_next = 8'd0;

deficit_idle_count_next = 2'd0;

state_next = STATE_IDLE;

end

end

STATE_PAYLOAD: begin

// transfer payload

update_crc = 1'b1;

s_axis_tready_next = 1'b1;

if (frame_min_count_reg > CTRL_WIDTH) begin

frame_min_count_next = frame_min_count_reg - CTRL_WIDTH;

end else begin

frame_min_count_next = 0;

end

xgmii_txd_next = s_tdata_reg;

xgmii_txc_next = {CTRL_WIDTH{1'b0}};

s_tdata_next = s_axis_tdata_masked;

s_empty_next = keep2empty(s_axis_tkeep);

if (!s_axis_tvalid || s_axis_tlast) begin

s_axis_tready_next = frame_next; // drop frame

frame_error_next = !s_axis_tvalid || s_axis_tuser[0];

error_underflow_next = !s_axis_tvalid;

if (ENABLE_PADDING && frame_min_count_reg) begin

if (frame_min_count_reg > CTRL_WIDTH) begin

s_empty_next = 0;

state_next = STATE_PAD;

end else begin

if (keep2empty(s_axis_tkeep) > CTRL_WIDTH-frame_min_count_reg) begin

s_empty_next = CTRL_WIDTH-frame_min_count_reg;

end

if (frame_error_next) begin

state_next = STATE_ERR;

end else begin

state_next = STATE_FCS_1;

end

end

end else begin

if (frame_error_next) begin

state_next = STATE_ERR;

end else begin

state_next = STATE_FCS_1;

end

end

end else begin

state_next = STATE_PAYLOAD;

end

end

STATE_PAD: begin

// pad frame to MIN_FRAME_LENGTH

s_axis_tready_next = frame_next; // drop frame

xgmii_txd_next = s_tdata_reg;

xgmii_txc_next = {CTRL_WIDTH{1'b0}};

s_tdata_next = 64'd0;

s_empty_next = 0;

update_crc = 1'b1;

if (frame_min_count_reg > CTRL_WIDTH) begin

frame_min_count_next = frame_min_count_reg - CTRL_WIDTH;

state_next = STATE_PAD;

end else begin

frame_min_count_next = 0;

s_empty_next = CTRL_WIDTH-frame_min_count_reg;

if (frame_error_reg) begin

state_next = STATE_ERR;

end else begin

state_next = STATE_FCS_1;

end

end

end

STATE_FCS_1: begin

// last cycle

s_axis_tready_next = frame_next; // drop frame

xgmii_txd_next = fcs_output_txd_0;

xgmii_txc_next = fcs_output_txc_0;

update_crc = 1'b1;

ifg_count_next = (cfg_ifg > 8'd12 ? cfg_ifg : 8'd12) - ifg_offset + (swap_lanes_reg ? 8'd4 : 8'd0) + deficit_idle_count_reg;

if (s_empty_reg <= 4) begin

state_next = STATE_FCS_2;

end else begin

state_next = STATE_IFG;

end

end

STATE_FCS_2: begin

// last cycle

s_axis_tready_next = frame_next; // drop frame

xgmii_txd_next = fcs_output_txd_1;

xgmii_txc_next = fcs_output_txc_1;

if (ENABLE_DIC) begin

if (ifg_count_next > 8'd7) begin

state_next = STATE_IFG;

end else begin

if (ifg_count_next >= 8'd4) begin

deficit_idle_count_next = ifg_count_next - 8'd4;

swap_lanes_next = 1'b1;

end else begin

deficit_idle_count_next = ifg_count_next;

ifg_count_next = 8'd0;

swap_lanes_next = 1'b0;

end

s_axis_tready_next = cfg_tx_enable;

state_next = STATE_IDLE;

end

end else begin

if (ifg_count_next > 8'd4) begin

state_next = STATE_IFG;

end else begin

s_axis_tready_next = cfg_tx_enable;

swap_lanes_next = ifg_count_next != 0;

state_next = STATE_IDLE;

end

end

end

STATE_ERR: begin

// terminate packet with error

s_axis_tready_next = frame_next; // drop frame

// XGMII error

xgmii_txd_next = {XGMII_TERM, {7{XGMII_ERROR}}};

xgmii_txc_next = {CTRL_WIDTH{1'b1}};

ifg_count_next = 8'd12;

state_next = STATE_IFG;

end

STATE_IFG: begin

// send IFG

s_axis_tready_next = frame_next; // drop frame

// XGMII idle

xgmii_txd_next = {CTRL_WIDTH{XGMII_IDLE}};

xgmii_txc_next = {CTRL_WIDTH{1'b1}};

if (ifg_count_reg > 8'd8) begin

ifg_count_next = ifg_count_reg - 8'd8;

end else begin

ifg_count_next = 8'd0;

end

if (ENABLE_DIC) begin

if (ifg_count_next > 8'd7 || frame_reg) begin

state_next = STATE_IFG;

end else begin

if (ifg_count_next >= 8'd4) begin

deficit_idle_count_next = ifg_count_next - 8'd4;

swap_lanes_next = 1'b1;

end else begin

deficit_idle_count_next = ifg_count_next;

ifg_count_next = 8'd0;

swap_lanes_next = 1'b0;

end

s_axis_tready_next = cfg_tx_enable;

state_next = STATE_IDLE;

end

end else begin

if (ifg_count_next > 8'd4 || frame_reg) begin

state_next = STATE_IFG;

end else begin

s_axis_tready_next = cfg_tx_enable;

swap_lanes_next = ifg_count_next != 0;

state_next = STATE_IDLE;

end

end

end

endcase

end

always @(posedge clk) begin

state_reg <= state_next;

swap_lanes_reg <= swap_lanes_next;

frame_start_reg <= frame_start_next;

frame_reg <= frame_next;

frame_error_reg <= frame_error_next;

frame_min_count_reg <= frame_min_count_next;

ifg_count_reg <= ifg_count_next;

deficit_idle_count_reg <= deficit_idle_count_next;

s_tdata_reg <= s_tdata_next;

s_empty_reg <= s_empty_next;

s_axis_tready_reg <= s_axis_tready_next;

m_axis_ptp_ts_valid_reg <= 1'b0;

m_axis_ptp_ts_valid_int_reg <= 1'b0;

start_packet_reg <= 2'b00;

error_underflow_reg <= error_underflow_next;

if (PTP_TS_ENABLE && PTP_TS_FMT_TOD) begin

m_axis_ptp_ts_valid_reg <= m_axis_ptp_ts_valid_int_reg;

m_axis_ptp_ts_adj_reg[15:0] <= m_axis_ptp_ts_reg[15:0];

{m_axis_ptp_ts_borrow_reg, m_axis_ptp_ts_adj_reg[45:16]} <= $signed({1'b0, m_axis_ptp_ts_reg[45:16]}) - $signed(31'd1000000000);

m_axis_ptp_ts_adj_reg[47:46] <= 0;

m_axis_ptp_ts_adj_reg[95:48] <= m_axis_ptp_ts_reg[95:48] + 1;

end

if (frame_start_reg) begin

if (swap_lanes_reg) begin

if (PTP_TS_ENABLE) begin

if (PTP_TS_FMT_TOD) begin

m_axis_ptp_ts_reg[45:0] <= ptp_ts[45:0] + (ts_inc_reg >> 1);

m_axis_ptp_ts_reg[95:48] <= ptp_ts[95:48];

end else begin

m_axis_ptp_ts_reg <= ptp_ts + (ts_inc_reg >> 1);

end

end

start_packet_reg <= 2'b10;

end else begin

if (PTP_TS_ENABLE) begin

m_axis_ptp_ts_reg <= ptp_ts;

end

start_packet_reg <= 2'b01;

end

if (PTP_TS_ENABLE) begin

if (PTP_TS_CTRL_IN_TUSER) begin

m_axis_ptp_ts_tag_reg <= s_axis_tuser >> 2;

if (PTP_TS_FMT_TOD) begin

m_axis_ptp_ts_valid_int_reg <= s_axis_tuser[1];

end else begin

m_axis_ptp_ts_valid_reg <= s_axis_tuser[1];

end

end else begin

m_axis_ptp_ts_tag_reg <= s_axis_tuser >> 1;

if (PTP_TS_FMT_TOD) begin

m_axis_ptp_ts_valid_int_reg <= 1'b1;

end else begin

m_axis_ptp_ts_valid_reg <= 1'b1;

end

end

end

end

crc_state_reg[0] <= crc_state_next[0];

crc_state_reg[1] <= crc_state_next[1];

crc_state_reg[2] <= crc_state_next[2];

crc_state_reg[3] <= crc_state_next[3];

crc_state_reg[4] <= crc_state_next[4];

crc_state_reg[5] <= crc_state_next[5];

crc_state_reg[6] <= crc_state_next[6];

if (update_crc) begin

crc_state_reg[7] <= crc_state_next[7];

end

if (reset_crc) begin

crc_state_reg[7] <= 32'hFFFFFFFF;

end

swap_txd <= xgmii_txd_next[63:32];

swap_txc <= xgmii_txc_next[7:4];

if (swap_lanes_reg) begin

xgmii_txd_reg <= {xgmii_txd_next[31:0], swap_txd};

xgmii_txc_reg <= {xgmii_txc_next[3:0], swap_txc};

end else begin

xgmii_txd_reg <= xgmii_txd_next;

xgmii_txc_reg <= xgmii_txc_next;

end

last_ts_reg <= ptp_ts;

ts_inc_reg <= ptp_ts - last_ts_reg;

if (rst) begin

state_reg <= STATE_IDLE;

frame_start_reg <= 1'b0;

frame_reg <= 1'b0;

swap_lanes_reg <= 1'b0;

ifg_count_reg <= 8'd0;

deficit_idle_count_reg <= 2'd0;

s_axis_tready_reg <= 1'b0;

m_axis_ptp_ts_valid_reg <= 1'b0;

m_axis_ptp_ts_valid_int_reg <= 1'b0;

xgmii_txd_reg <= {CTRL_WIDTH{XGMII_IDLE}};

xgmii_txc_reg <= {CTRL_WIDTH{1'b1}};

start_packet_reg <= 2'b00;

error_underflow_reg <= 1'b0;

end

end

endmodule

`resetall

点击查看代码

/*

Copyright (c) 2016-2023 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* Parametrizable combinatorial parallel LFSR/CRC

*/

module lfsr #

(

// width of LFSR

parameter LFSR_WIDTH = 31,

// LFSR polynomial

parameter LFSR_POLY = 31'h10000001,

// LFSR configuration: "GALOIS", "FIBONACCI"

parameter LFSR_CONFIG = "FIBONACCI",

// LFSR feed forward enable

parameter LFSR_FEED_FORWARD = 0,

// bit-reverse input and output

parameter REVERSE = 0,

// width of data input

parameter DATA_WIDTH = 8,

// implementation style: "AUTO", "LOOP", "REDUCTION"

parameter STYLE = "AUTO"

)

(

input wire [DATA_WIDTH-1:0] data_in,

input wire [LFSR_WIDTH-1:0] state_in,

output wire [DATA_WIDTH-1:0] data_out,

output wire [LFSR_WIDTH-1:0] state_out

);

/*

Fully parametrizable combinatorial parallel LFSR/CRC module. Implements an unrolled LFSR

next state computation, shifting DATA_WIDTH bits per pass through the module. Input data

is XORed with LFSR feedback path, tie data_in to zero if this is not required.

Works in two parts: statically computes a set of bit masks, then uses these bit masks to

select bits for XORing to compute the next state.

Ports:

data_in

Data bits to be shifted through the LFSR (DATA_WIDTH bits)

state_in

LFSR/CRC current state input (LFSR_WIDTH bits)

data_out

Data bits shifted out of LFSR (DATA_WIDTH bits)

state_out

LFSR/CRC next state output (LFSR_WIDTH bits)

Parameters:

LFSR_WIDTH

Specify width of LFSR/CRC register

LFSR_POLY

Specify the LFSR/CRC polynomial in hex format. For example, the polynomial

x^32 + x^26 + x^23 + x^22 + x^16 + x^12 + x^11 + x^10 + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1

would be represented as

32'h04c11db7

Note that the largest term (x^32) is suppressed. This term is generated automatically based

on LFSR_WIDTH.

LFSR_CONFIG

Specify the LFSR configuration, either Fibonacci or Galois. Fibonacci is generally used

for linear-feedback shift registers (LFSR) for pseudorandom binary sequence (PRBS) generators,

scramblers, and descrambers, while Galois is generally used for cyclic redundancy check

generators and checkers.

Fibonacci style (example for 64b66b scrambler, 0x8000000001)

DIN (LSB first)

|

V

(+)<---------------------------(+)<-----------------------------.

| ^ |

| .----. .----. .----. | .----. .----. .----. |

+->| 0 |->| 1 |->...->| 38 |-+->| 39 |->...->| 56 |->| 57 |--'

| '----' '----' '----' '----' '----' '----'

V

DOUT

Galois style (example for CRC16, 0x8005)

,-------------------+-------------------------+----------(+)<-- DIN (MSB first)

| | | ^

| .----. .----. V .----. .----. V .----. |

`->| 0 |->| 1 |->(+)->| 2 |->...->| 14 |->(+)->| 15 |--+---> DOUT

'----' '----' '----' '----' '----'

LFSR_FEED_FORWARD

Generate feed forward instead of feed back LFSR. Enable this for PRBS checking and self-

synchronous descrambling.

Fibonacci feed-forward style (example for 64b66b descrambler, 0x8000000001)

DIN (LSB first)

|

| .----. .----. .----. .----. .----. .----.

+->| 0 |->| 1 |->...->| 38 |-+->| 39 |->...->| 56 |->| 57 |--.

| '----' '----' '----' | '----' '----' '----' |

| V |

(+)<---------------------------(+)------------------------------'

|

V

DOUT

Galois feed-forward style

,-------------------+-------------------------+------------+--- DIN (MSB first)

| | | |

| .----. .----. V .----. .----. V .----. V

`->| 0 |->| 1 |->(+)->| 2 |->...->| 14 |->(+)->| 15 |->(+)-> DOUT

'----' '----' '----' '----' '----'

REVERSE

Bit-reverse LFSR input and output. Shifts MSB first by default, set REVERSE for LSB first.

DATA_WIDTH

Specify width of input and output data bus. The module will perform one shift per input

data bit, so if the input data bus is not required tie data_in to zero and set DATA_WIDTH

to the required number of shifts per clock cycle.

STYLE

Specify implementation style. Can be "AUTO", "LOOP", or "REDUCTION". When "AUTO"

is selected, implemenation will be "LOOP" or "REDUCTION" based on synthesis translate

directives. "REDUCTION" and "LOOP" are functionally identical, however they simulate

and synthesize differently. "REDUCTION" is implemented with a loop over a Verilog

reduction operator. "LOOP" is implemented as a doubly-nested loop with no reduction

operator. "REDUCTION" is very fast for simulation in iverilog and synthesizes well in

Quartus but synthesizes poorly in ISE, likely due to large inferred XOR gates causing

problems with the optimizer. "LOOP" synthesizes will in both ISE and Quartus. "AUTO"

will default to "REDUCTION" when simulating and "LOOP" for synthesizers that obey

synthesis translate directives.

Settings for common LFSR/CRC implementations:

Name Configuration Length Polynomial Initial value Notes

CRC16-IBM Galois, bit-reverse 16 16'h8005 16'hffff

CRC16-CCITT Galois 16 16'h1021 16'h1d0f

CRC32 Galois, bit-reverse 32 32'h04c11db7 32'hffffffff Ethernet FCS; invert final output

CRC32C Galois, bit-reverse 32 32'h1edc6f41 32'hffffffff iSCSI, Intel CRC32 instruction; invert final output

PRBS6 Fibonacci 6 6'h21 any

PRBS7 Fibonacci 7 7'h41 any

PRBS9 Fibonacci 9 9'h021 any ITU V.52

PRBS10 Fibonacci 10 10'h081 any ITU

PRBS11 Fibonacci 11 11'h201 any ITU O.152

PRBS15 Fibonacci, inverted 15 15'h4001 any ITU O.152

PRBS17 Fibonacci 17 17'h04001 any

PRBS20 Fibonacci 20 20'h00009 any ITU V.57

PRBS23 Fibonacci, inverted 23 23'h040001 any ITU O.151

PRBS29 Fibonacci, inverted 29 29'h08000001 any

PRBS31 Fibonacci, inverted 31 31'h10000001 any

64b66b Fibonacci, bit-reverse 58 58'h8000000001 any 10G Ethernet

128b130b Galois, bit-reverse 23 23'h210125 any PCIe gen 3

*/

function [LFSR_WIDTH+DATA_WIDTH-1:0] lfsr_mask(input [31:0] index);

reg [LFSR_WIDTH-1:0] lfsr_mask_state[LFSR_WIDTH-1:0];

reg [DATA_WIDTH-1:0] lfsr_mask_data[LFSR_WIDTH-1:0];

reg [LFSR_WIDTH-1:0] output_mask_state[DATA_WIDTH-1:0];

reg [DATA_WIDTH-1:0] output_mask_data[DATA_WIDTH-1:0];

reg [LFSR_WIDTH-1:0] state_val;

reg [DATA_WIDTH-1:0] data_val;

reg [DATA_WIDTH-1:0] data_mask;

integer i, j;

begin

// init bit masks

for (i = 0; i < LFSR_WIDTH; i = i + 1) begin

lfsr_mask_state[i] = 0;

lfsr_mask_state[i][i] = 1'b1;

lfsr_mask_data[i] = 0;

end

for (i = 0; i < DATA_WIDTH; i = i + 1) begin

output_mask_state[i] = 0;

if (i < LFSR_WIDTH) begin

output_mask_state[i][i] = 1'b1;

end

output_mask_data[i] = 0;

end

// simulate shift register

if (LFSR_CONFIG == "FIBONACCI") begin

// Fibonacci configuration

for (data_mask = {1'b1, {DATA_WIDTH-1{1'b0}}}; data_mask != 0; data_mask = data_mask >> 1) begin

// determine shift in value

// current value in last FF, XOR with input data bit (MSB first)

state_val = lfsr_mask_state[LFSR_WIDTH-1];

data_val = lfsr_mask_data[LFSR_WIDTH-1];

data_val = data_val ^ data_mask;

// add XOR inputs from correct indicies

for (j = 1; j < LFSR_WIDTH; j = j + 1) begin

if ((LFSR_POLY >> j) & 1) begin

state_val = lfsr_mask_state[j-1] ^ state_val;

data_val = lfsr_mask_data[j-1] ^ data_val;

end

end

// shift

for (j = LFSR_WIDTH-1; j > 0; j = j - 1) begin

lfsr_mask_state[j] = lfsr_mask_state[j-1];

lfsr_mask_data[j] = lfsr_mask_data[j-1];

end

for (j = DATA_WIDTH-1; j > 0; j = j - 1) begin

output_mask_state[j] = output_mask_state[j-1];

output_mask_data[j] = output_mask_data[j-1];

end

output_mask_state[0] = state_val;

output_mask_data[0] = data_val;

if (LFSR_FEED_FORWARD) begin

// only shift in new input data

state_val = {LFSR_WIDTH{1'b0}};

data_val = data_mask;

end

lfsr_mask_state[0] = state_val;

lfsr_mask_data[0] = data_val;

end

end else if (LFSR_CONFIG == "GALOIS") begin

// Galois configuration

for (data_mask = {1'b1, {DATA_WIDTH-1{1'b0}}}; data_mask != 0; data_mask = data_mask >> 1) begin

// determine shift in value

// current value in last FF, XOR with input data bit (MSB first)

state_val = lfsr_mask_state[LFSR_WIDTH-1];

data_val = lfsr_mask_data[LFSR_WIDTH-1];

data_val = data_val ^ data_mask;

// shift

for (j = LFSR_WIDTH-1; j > 0; j = j - 1) begin

lfsr_mask_state[j] = lfsr_mask_state[j-1];

lfsr_mask_data[j] = lfsr_mask_data[j-1];

end

for (j = DATA_WIDTH-1; j > 0; j = j - 1) begin

output_mask_state[j] = output_mask_state[j-1];

output_mask_data[j] = output_mask_data[j-1];

end

output_mask_state[0] = state_val;

output_mask_data[0] = data_val;

if (LFSR_FEED_FORWARD) begin

// only shift in new input data

state_val = {LFSR_WIDTH{1'b0}};

data_val = data_mask;

end

lfsr_mask_state[0] = state_val;

lfsr_mask_data[0] = data_val;

// add XOR inputs at correct indicies

for (j = 1; j < LFSR_WIDTH; j = j + 1) begin

if ((LFSR_POLY >> j) & 1) begin

lfsr_mask_state[j] = lfsr_mask_state[j] ^ state_val;

lfsr_mask_data[j] = lfsr_mask_data[j] ^ data_val;

end

end

end

end else begin

$error("Error: unknown configuration setting!");

$finish;

end

// reverse bits if selected

if (REVERSE) begin

if (index < LFSR_WIDTH) begin

state_val = 0;

for (i = 0; i < LFSR_WIDTH; i = i + 1) begin

state_val[i] = lfsr_mask_state[LFSR_WIDTH-index-1][LFSR_WIDTH-i-1];

end

data_val = 0;

for (i = 0; i < DATA_WIDTH; i = i + 1) begin

data_val[i] = lfsr_mask_data[LFSR_WIDTH-index-1][DATA_WIDTH-i-1];

end

end else begin

state_val = 0;

for (i = 0; i < LFSR_WIDTH; i = i + 1) begin

state_val[i] = output_mask_state[DATA_WIDTH-(index-LFSR_WIDTH)-1][LFSR_WIDTH-i-1];

end

data_val = 0;

for (i = 0; i < DATA_WIDTH; i = i + 1) begin

data_val[i] = output_mask_data[DATA_WIDTH-(index-LFSR_WIDTH)-1][DATA_WIDTH-i-1];

end

end

end else begin

if (index < LFSR_WIDTH) begin

state_val = lfsr_mask_state[index];

data_val = lfsr_mask_data[index];

end else begin

state_val = output_mask_state[index-LFSR_WIDTH];

data_val = output_mask_data[index-LFSR_WIDTH];

end

end

lfsr_mask = {data_val, state_val};

end

endfunction

// synthesis translate_off

`define SIMULATION

// synthesis translate_on

`ifdef SIMULATION

// "AUTO" style is "REDUCTION" for faster simulation

parameter STYLE_INT = (STYLE == "AUTO") ? "REDUCTION" : STYLE;

`else

// "AUTO" style is "LOOP" for better synthesis result

parameter STYLE_INT = (STYLE == "AUTO") ? "LOOP" : STYLE;

`endif

genvar n;

generate

if (STYLE_INT == "REDUCTION") begin

// use Verilog reduction operator

// fast in iverilog

// significantly larger than generated code with ISE (inferred wide XORs may be tripping up optimizer)

// slightly smaller than generated code with Quartus

// --> better for simulation

for (n = 0; n < LFSR_WIDTH; n = n + 1) begin : lfsr_state

wire [LFSR_WIDTH+DATA_WIDTH-1:0] mask = lfsr_mask(n);

assign state_out[n] = ^({data_in, state_in} & mask);

end

for (n = 0; n < DATA_WIDTH; n = n + 1) begin : lfsr_data

wire [LFSR_WIDTH+DATA_WIDTH-1:0] mask = lfsr_mask(n+LFSR_WIDTH);

assign data_out[n] = ^({data_in, state_in} & mask);

end

end else if (STYLE_INT == "LOOP") begin

// use nested loops

// very slow in iverilog

// slightly smaller than generated code with ISE

// same size as generated code with Quartus

// --> better for synthesis

for (n = 0; n < LFSR_WIDTH; n = n + 1) begin : lfsr_state

wire [LFSR_WIDTH+DATA_WIDTH-1:0] mask = lfsr_mask(n);

reg state_reg;

assign state_out[n] = state_reg;

integer i;

always @* begin

state_reg = 1'b0;

for (i = 0; i < LFSR_WIDTH; i = i + 1) begin

if (mask[i]) begin

state_reg = state_reg ^ state_in[i];

end

end

for (i = 0; i < DATA_WIDTH; i = i + 1) begin

if (mask[i+LFSR_WIDTH]) begin

state_reg = state_reg ^ data_in[i];

end

end

end

end

for (n = 0; n < DATA_WIDTH; n = n + 1) begin : lfsr_data

wire [LFSR_WIDTH+DATA_WIDTH-1:0] mask = lfsr_mask(n+LFSR_WIDTH);

reg data_reg;

assign data_out[n] = data_reg;

integer i;

always @* begin

data_reg = 1'b0;

for (i = 0; i < LFSR_WIDTH; i = i + 1) begin

if (mask[i]) begin

data_reg = data_reg ^ state_in[i];

end

end

for (i = 0; i < DATA_WIDTH; i = i + 1) begin

if (mask[i+LFSR_WIDTH]) begin

data_reg = data_reg ^ data_in[i];

end

end

end

end

end else begin

initial begin

$error("Error: unknown style setting!");

$finish;

end

end

endgenerate

endmodule

`resetall

点击查看代码

`timescale 1ns / 1ps

module tb_axis_xgmii_rx_64()

;

// 模块参数

parameter DATA_WIDTH = 64;

parameter KEEP_WIDTH = DATA_WIDTH/8;

parameter CTRL_WIDTH = DATA_WIDTH/8;

// 时钟和复位信号

reg clk;

reg rst;

// XGMII输入接口

wire [DATA_WIDTH-1:0] xgmii_rxd;

wire [CTRL_WIDTH-1:0] xgmii_rxc;

wire [DATA_WIDTH-1:0] xgmii_txd;

wire [CTRL_WIDTH-1:0] xgmii_txc;

// AXI输出接口

wire [DATA_WIDTH-1:0] m_axis_tdata;

wire [KEEP_WIDTH-1:0] m_axis_tkeep;

wire m_axis_tvalid;

wire m_axis_tlast;

wire [0:0] m_axis_tuser;

reg [DATA_WIDTH-1:0] axis_tdata ;

reg [KEEP_WIDTH-1:0] axis_tkeep ;

reg axis_tvalid;

wire axis_tready;

reg axis_tlast ;

reg [0:0] axis_tuser = 0 ;

wire [1:0] start_packet_tx;

wire error_underflow;

// 配置和状态信号

wire [1:0] start_packet_rx;

wire error_bad_frame;

wire error_bad_fcs;

// 实例化被测模块

axis_xgmii_rx_64 #(

.DATA_WIDTH(DATA_WIDTH),

.PTP_TS_ENABLE(0)

) u_axis_xgmii_rx_64 (

.clk(clk),

.rst(rst),

.xgmii_rxd(xgmii_rxd),

.xgmii_rxc(xgmii_rxc),

.m_axis_tdata(m_axis_tdata),

.m_axis_tkeep(m_axis_tkeep),

.m_axis_tvalid(m_axis_tvalid),

.m_axis_tlast(m_axis_tlast),

.m_axis_tuser(m_axis_tuser),

.ptp_ts(32'd0),

.cfg_rx_enable(1'b1),

.start_packet(start_packet_rx),

.error_bad_frame(error_bad_frame),

.error_bad_fcs(error_bad_fcs)

);

axis_xgmii_tx_64#(

.DATA_WIDTH ( 64 ),

.ENABLE_PADDING ( 1 ),

.ENABLE_DIC ( 0 ),

.MIN_FRAME_LENGTH ( 64 ),

.PTP_TS_ENABLE ( 0 ),

.PTP_TS_FMT_TOD ( 1 )

)u_axis_xgmii_tx_64(

.clk ( clk ),

.rst ( rst ),

.s_axis_tdata ( axis_tdata ),

.s_axis_tkeep ( axis_tkeep ),

.s_axis_tvalid ( axis_tvalid ),

.s_axis_tready ( axis_tready ),

.s_axis_tlast ( axis_tlast ),

.s_axis_tuser ( axis_tuser ),

.xgmii_txd ( xgmii_txd ),

.xgmii_txc ( xgmii_txc ),

.ptp_ts ( 32'd0 ),

.m_axis_ptp_ts ( ),

.m_axis_ptp_ts_tag ( ),

.m_axis_ptp_ts_valid ( ),

.cfg_ifg ( 32'd12 ),

.cfg_tx_enable ( 1'b1 ),

.start_packet ( start_packet_tx ),

.error_underflow ( error_underflow )

);

// 时钟生成 (156.25MHz for 10G Ethernet)

initial begin

clk = 1'b0;

forever #3.2 clk = ~clk;

end

// 测试主程序

initial begin

// 初始化输入

rst = 1'b1;

#20 rst = 1'b1;

#200 rst = 1'b0;

end

assign xgmii_rxd = xgmii_txd;

assign xgmii_rxc = xgmii_txc;

reg [7:0] cycle_count;

always @(posedge clk or negedge rst) begin

if (rst) begin

cycle_count <= 8'd0;

axis_tdata <= 64'd0;

axis_tkeep <= 8'hFF; // 默认保持所有字节有效

axis_tvalid <= 1'b0;

axis_tlast <= 1'b0;

end

else begin

if (cycle_count < 8'd100) begin

// 只有在tready有效或没有背压时才增加计数

if (axis_tvalid && axis_tready || !axis_tvalid) begin

axis_tvalid <= 1'b1;

axis_tdata <= {56'd0, cycle_count}; // 数据内容为周期计数

// 在第100个周期设置tlast

if (cycle_count == 8'd99) begin

axis_tlast <= 1'b1;

axis_tkeep <= 8'h1;//1对应终止字符在第六字节,F对应种植字符在第1字节

end

else begin

axis_tlast <= 1'b0;

end

cycle_count <= cycle_count + 8'd1;

end

end

else begin

// 完成100个周期后停止发送

axis_tvalid <= 1'b0;

axis_tlast <= 1'b0;

end

end

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号