eth_mac_10g_fifo

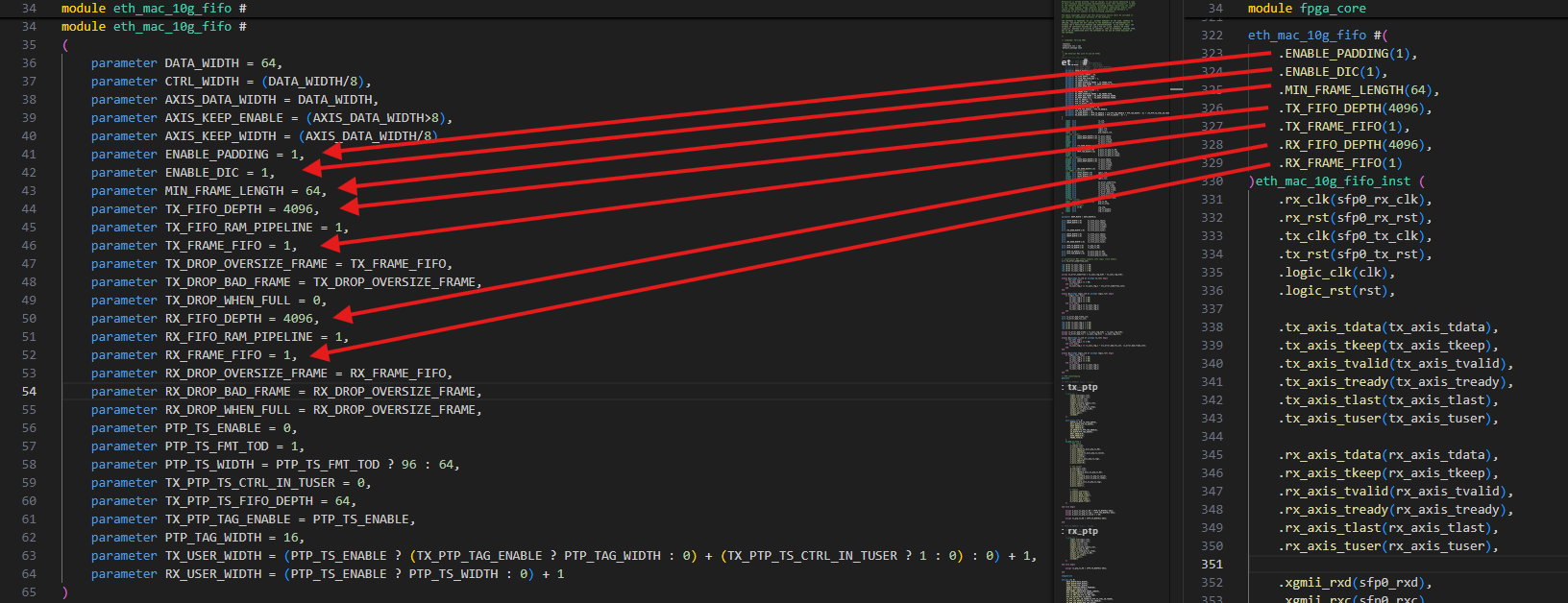

这里给出了上层fpga_core模块里eth_mac_10g_fifo的例化和eth_mac_10g_fifo的实际情况,具体例化的参数用箭头标出。

parameter ENABLE_PADDING = 1, parameter ENABLE_DIC = 1, parameter MIN_FRAME_LENGTH = 64,这三个参数关联到了里面的eth_mac_10g模块,后续再分析。

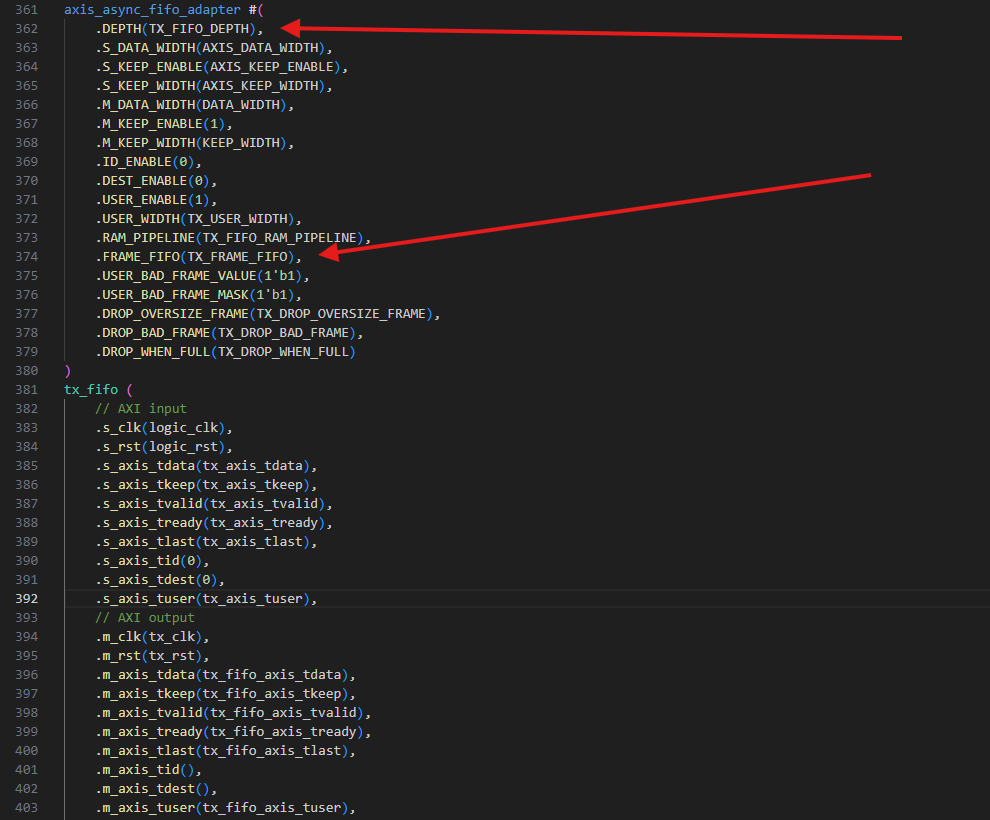

parameter TX_FIFO_DEPTH = 4096, parameter TX_FRAME_FIFO = 1, parameter RX_FIFO_DEPTH = 4096,parameter RX_FRAME_FIFO = 1,则是关联到了axis_async_fifo_adapter的参数例化,axis_async_fifo_adapter是异步fifo,用于时钟域切换。

所以结合上层fpga_core模块里eth_mac_10g_fifo的例化可以得到结论为,rx、tx异步fifo的数据位宽为64,启动KEEP选项,位宽为8,深度都为4096,流水线级数为1,适量提高延迟以提高频率,开启帧fifo模式,但rx fifo在fifo满时丢弃新帧,tx_fifo则会反压,坏帧与超长帧两者都是丢弃,不使能PTP同步,TX_USER_WIDTH和RX_USER_WIDTH都为1,PTP同步可以上网查询,是一个降低延迟的方法。

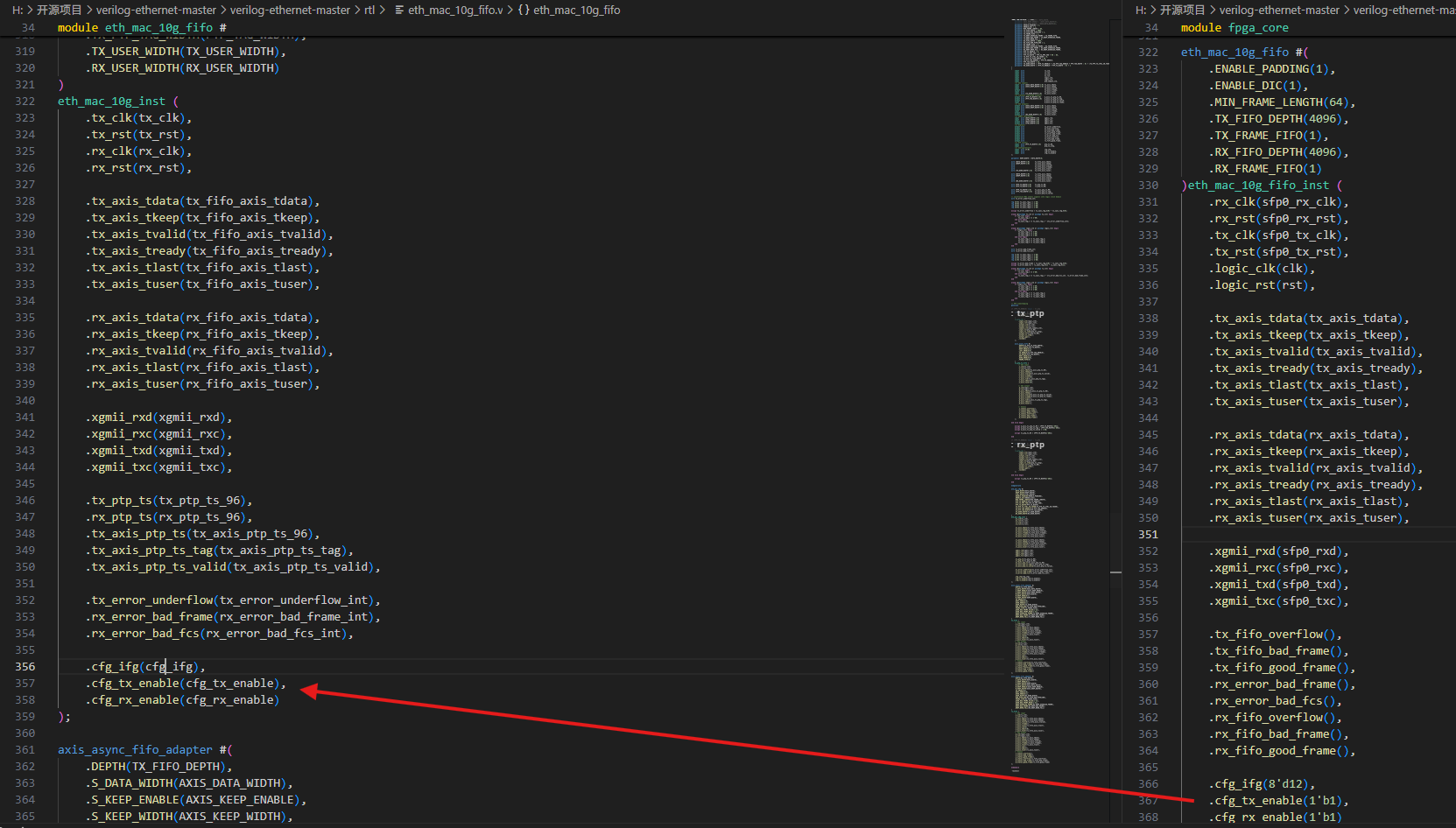

下面整体上形成了一个带接收发送FIFO的万兆mac层。

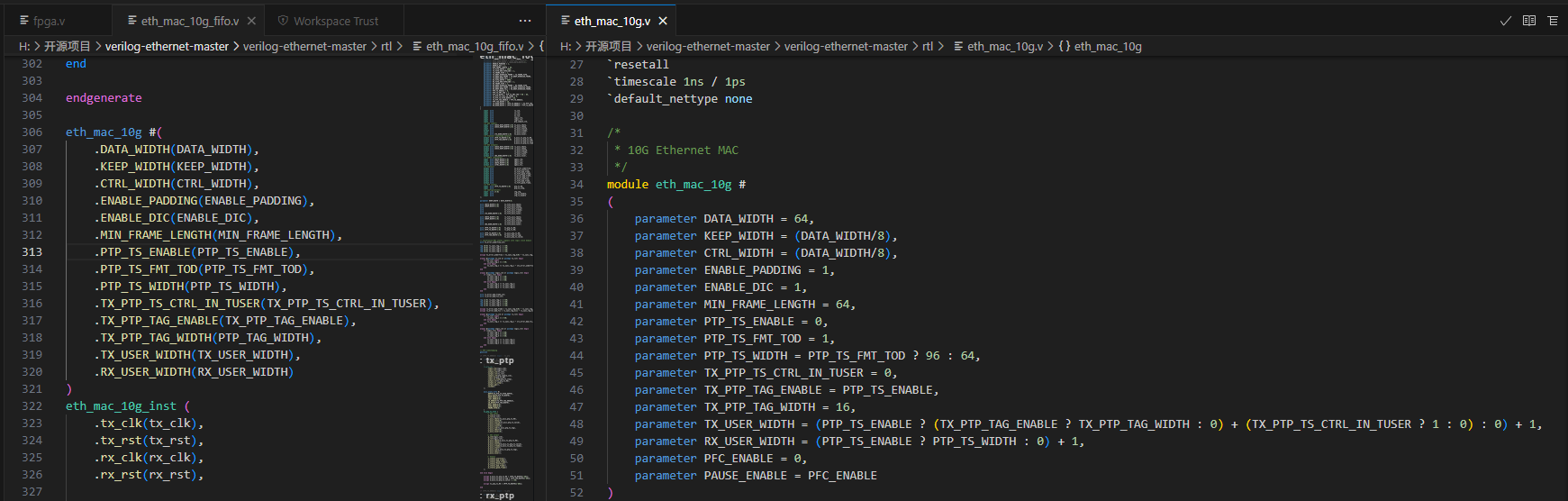

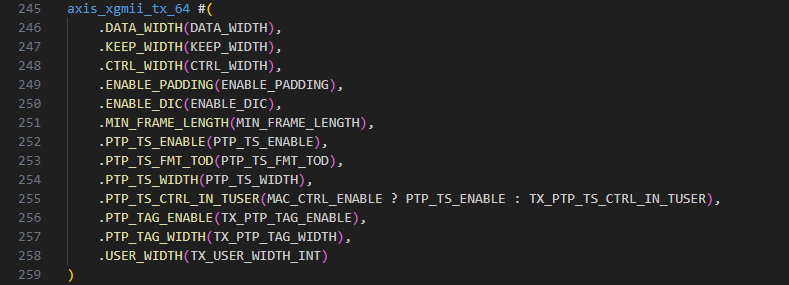

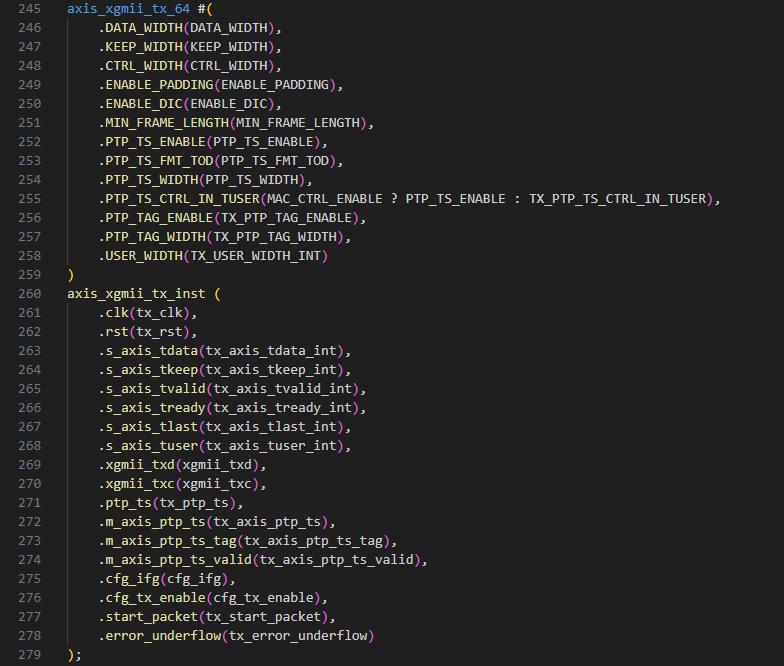

eth_mac_10g的例化比较简单。parameter ENABLE_PADDING = 1, parameter ENABLE_DIC = 1, parameter MIN_FRAME_LENGTH = 64,这三个参数关联到了axis_xgmii_tx_64模块,后续分析。PTP不启用,故其他参数不需要注意。

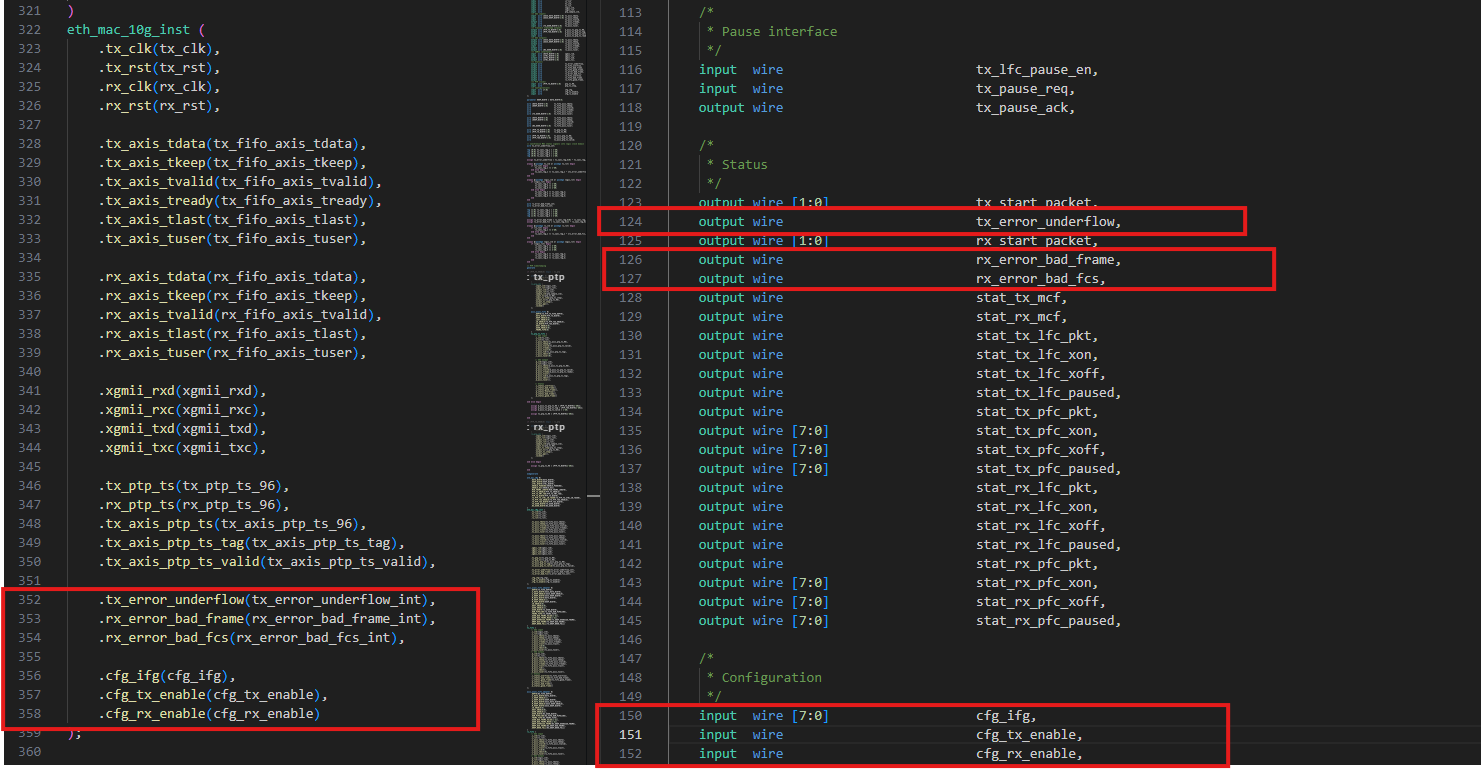

与上层eth_mac_10g_fifo有用的输入输出接口如下图

eth_mac_10g有用的大部分逻辑如下图

完整代码如下。

点击查看代码

/*

Copyright (c) 2015-2018 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* 10G Ethernet MAC with TX and RX FIFOs

*/

module eth_mac_10g_fifo #

(

parameter DATA_WIDTH = 64,

parameter CTRL_WIDTH = (DATA_WIDTH/8),

parameter AXIS_DATA_WIDTH = DATA_WIDTH,

parameter AXIS_KEEP_ENABLE = (AXIS_DATA_WIDTH>8),

parameter AXIS_KEEP_WIDTH = (AXIS_DATA_WIDTH/8),

parameter ENABLE_PADDING = 1,

parameter ENABLE_DIC = 1,

parameter MIN_FRAME_LENGTH = 64,

parameter TX_FIFO_DEPTH = 4096,

parameter TX_FIFO_RAM_PIPELINE = 1,

parameter TX_FRAME_FIFO = 1,

parameter TX_DROP_OVERSIZE_FRAME = TX_FRAME_FIFO,

parameter TX_DROP_BAD_FRAME = TX_DROP_OVERSIZE_FRAME,

parameter TX_DROP_WHEN_FULL = 0,

parameter RX_FIFO_DEPTH = 4096,

parameter RX_FIFO_RAM_PIPELINE = 1,

parameter RX_FRAME_FIFO = 1,

parameter RX_DROP_OVERSIZE_FRAME = RX_FRAME_FIFO,

parameter RX_DROP_BAD_FRAME = RX_DROP_OVERSIZE_FRAME,

parameter RX_DROP_WHEN_FULL = RX_DROP_OVERSIZE_FRAME,

parameter PTP_TS_ENABLE = 0,

parameter PTP_TS_FMT_TOD = 1,

parameter PTP_TS_WIDTH = PTP_TS_FMT_TOD ? 96 : 64,

parameter TX_PTP_TS_CTRL_IN_TUSER = 0,

parameter TX_PTP_TS_FIFO_DEPTH = 64,

parameter TX_PTP_TAG_ENABLE = PTP_TS_ENABLE,

parameter PTP_TAG_WIDTH = 16,

parameter TX_USER_WIDTH = (PTP_TS_ENABLE ? (TX_PTP_TAG_ENABLE ? PTP_TAG_WIDTH : 0) + (TX_PTP_TS_CTRL_IN_TUSER ? 1 : 0) : 0) + 1,

parameter RX_USER_WIDTH = (PTP_TS_ENABLE ? PTP_TS_WIDTH : 0) + 1

)

(

input wire rx_clk,

input wire rx_rst,

input wire tx_clk,

input wire tx_rst,

input wire logic_clk,

input wire logic_rst,

input wire ptp_sample_clk,

/** AXI input*/

input wire [AXIS_DATA_WIDTH-1:0] tx_axis_tdata,

input wire [AXIS_KEEP_WIDTH-1:0] tx_axis_tkeep,

input wire tx_axis_tvalid,

output wire tx_axis_tready,

input wire tx_axis_tlast,

input wire [TX_USER_WIDTH-1:0] tx_axis_tuser,

/** Transmit timestamp output*/

output wire [PTP_TS_WIDTH-1:0] m_axis_tx_ptp_ts_96,

output wire [PTP_TAG_WIDTH-1:0] m_axis_tx_ptp_ts_tag,

output wire m_axis_tx_ptp_ts_valid,

input wire m_axis_tx_ptp_ts_ready,

/** AXI output*/

output wire [AXIS_DATA_WIDTH-1:0] rx_axis_tdata,

output wire [AXIS_KEEP_WIDTH-1:0] rx_axis_tkeep,

output wire rx_axis_tvalid,

input wire rx_axis_tready,

output wire rx_axis_tlast,

output wire [RX_USER_WIDTH-1:0] rx_axis_tuser,

/** XGMII interface*/

input wire [DATA_WIDTH-1:0] xgmii_rxd,

input wire [CTRL_WIDTH-1:0] xgmii_rxc,

output wire [DATA_WIDTH-1:0] xgmii_txd,

output wire [CTRL_WIDTH-1:0] xgmii_txc,

/** Status*/

output wire tx_error_underflow,

output wire tx_fifo_overflow,

output wire tx_fifo_bad_frame,

output wire tx_fifo_good_frame,

output wire rx_error_bad_frame,

output wire rx_error_bad_fcs,

output wire rx_fifo_overflow,

output wire rx_fifo_bad_frame,

output wire rx_fifo_good_frame,

/** PTP clock*/

input wire [PTP_TS_WIDTH-1:0] ptp_ts_96,

input wire ptp_ts_step,

/** Configuration*/

input wire [7:0] cfg_ifg,

input wire cfg_tx_enable,

input wire cfg_rx_enable

);

parameter KEEP_WIDTH = DATA_WIDTH/8;

wire [DATA_WIDTH-1:0] tx_fifo_axis_tdata;

wire [KEEP_WIDTH-1:0] tx_fifo_axis_tkeep;

wire tx_fifo_axis_tvalid;

wire tx_fifo_axis_tready;

wire tx_fifo_axis_tlast;

wire [TX_USER_WIDTH-1:0] tx_fifo_axis_tuser;

wire [DATA_WIDTH-1:0] rx_fifo_axis_tdata;

wire [KEEP_WIDTH-1:0] rx_fifo_axis_tkeep;

wire rx_fifo_axis_tvalid;

wire rx_fifo_axis_tlast;

wire [RX_USER_WIDTH-1:0] rx_fifo_axis_tuser;

wire [PTP_TS_WIDTH-1:0] tx_ptp_ts_96;

wire [PTP_TS_WIDTH-1:0] rx_ptp_ts_96;

wire [PTP_TS_WIDTH-1:0] tx_axis_ptp_ts_96;

wire [PTP_TAG_WIDTH-1:0] tx_axis_ptp_ts_tag;

wire tx_axis_ptp_ts_valid;

// synchronize MAC status signals into logic clock domain

wire tx_error_underflow_int;

reg [0:0] tx_sync_reg_1 = 1'b0;

reg [0:0] tx_sync_reg_2 = 1'b0;

reg [0:0] tx_sync_reg_3 = 1'b0;

reg [0:0] tx_sync_reg_4 = 1'b0;

assign tx_error_underflow = tx_sync_reg_3[0] ^ tx_sync_reg_4[0];

always @(posedge tx_clk or posedge tx_rst) begin

if (tx_rst) begin

tx_sync_reg_1 <= 1'b0;

end else begin

tx_sync_reg_1 <= tx_sync_reg_1 ^ {tx_error_underflow_int};

end

end

always @(posedge logic_clk or posedge logic_rst) begin

if (logic_rst) begin

tx_sync_reg_2 <= 1'b0;

tx_sync_reg_3 <= 1'b0;

tx_sync_reg_4 <= 1'b0;

end else begin

tx_sync_reg_2 <= tx_sync_reg_1;

tx_sync_reg_3 <= tx_sync_reg_2;

tx_sync_reg_4 <= tx_sync_reg_3;

end

end

wire rx_error_bad_frame_int;

wire rx_error_bad_fcs_int;

reg [1:0] rx_sync_reg_1 = 2'd0;

reg [1:0] rx_sync_reg_2 = 2'd0;

reg [1:0] rx_sync_reg_3 = 2'd0;

reg [1:0] rx_sync_reg_4 = 2'd0;

assign rx_error_bad_frame = rx_sync_reg_3[0] ^ rx_sync_reg_4[0];

assign rx_error_bad_fcs = rx_sync_reg_3[1] ^ rx_sync_reg_4[1];

always @(posedge rx_clk or posedge rx_rst) begin

if (rx_rst) begin

rx_sync_reg_1 <= 2'd0;

end else begin

rx_sync_reg_1 <= rx_sync_reg_1 ^ {rx_error_bad_fcs_int, rx_error_bad_frame_int};

end

end

always @(posedge logic_clk or posedge logic_rst) begin

if (logic_rst) begin

rx_sync_reg_2 <= 2'd0;

rx_sync_reg_3 <= 2'd0;

rx_sync_reg_4 <= 2'd0;

end else begin

rx_sync_reg_2 <= rx_sync_reg_1;

rx_sync_reg_3 <= rx_sync_reg_2;

rx_sync_reg_4 <= rx_sync_reg_3;

end

end

// PTP timestamping

generate

if (PTP_TS_ENABLE) begin : tx_ptp

ptp_clock_cdc #(

.TS_WIDTH(PTP_TS_WIDTH),

.NS_WIDTH(6)

)

tx_ptp_cdc (

.input_clk(logic_clk),

.input_rst(logic_rst),

.output_clk(tx_clk),

.output_rst(tx_rst),

.sample_clk(ptp_sample_clk),

.input_ts(ptp_ts_96),

.input_ts_step(ptp_ts_step),

.output_ts(tx_ptp_ts_96),

.output_ts_step(),

.output_pps(),

.locked()

);

axis_async_fifo #(

.DEPTH(TX_PTP_TS_FIFO_DEPTH),

.DATA_WIDTH(PTP_TS_WIDTH),

.KEEP_ENABLE(0),

.LAST_ENABLE(0),

.ID_ENABLE(TX_PTP_TAG_ENABLE),

.ID_WIDTH(PTP_TAG_WIDTH),

.DEST_ENABLE(0),

.USER_ENABLE(0),

.FRAME_FIFO(0)

)

tx_ptp_ts_fifo (

// AXI input

.s_clk(tx_clk),

.s_rst(tx_rst),

.s_axis_tdata(tx_axis_ptp_ts_96),

.s_axis_tkeep(0),

.s_axis_tvalid(tx_axis_ptp_ts_valid),

.s_axis_tready(),

.s_axis_tlast(0),

.s_axis_tid(tx_axis_ptp_ts_tag),

.s_axis_tdest(0),

.s_axis_tuser(0),

// AXI output

.m_clk(logic_clk),

.m_rst(logic_rst),

.m_axis_tdata(m_axis_tx_ptp_ts_96),

.m_axis_tkeep(),

.m_axis_tvalid(m_axis_tx_ptp_ts_valid),

.m_axis_tready(m_axis_tx_ptp_ts_ready),

.m_axis_tlast(),

.m_axis_tid(m_axis_tx_ptp_ts_tag),

.m_axis_tdest(),

.m_axis_tuser(),

// Status

.s_status_overflow(),

.s_status_bad_frame(),

.s_status_good_frame(),

.m_status_overflow(),

.m_status_bad_frame(),

.m_status_good_frame()

);

end else begin

assign m_axis_tx_ptp_ts_96 = {PTP_TS_WIDTH{1'b0}};

assign m_axis_tx_ptp_ts_tag = {PTP_TAG_WIDTH{1'b0}};

assign m_axis_tx_ptp_ts_valid = 1'b0;

assign tx_ptp_ts_96 = {PTP_TS_WIDTH{1'b0}};

end

if (PTP_TS_ENABLE) begin : rx_ptp

ptp_clock_cdc #(

.TS_WIDTH(PTP_TS_WIDTH),

.NS_WIDTH(6)

)

rx_ptp_cdc (

.input_clk(logic_clk),

.input_rst(logic_rst),

.output_clk(rx_clk),

.output_rst(rx_rst),

.sample_clk(ptp_sample_clk),

.input_ts(ptp_ts_96),

.input_ts_step(ptp_ts_step),

.output_ts(rx_ptp_ts_96),

.output_ts_step(),

.output_pps(),

.locked()

);

end else begin

assign rx_ptp_ts_96 = {PTP_TS_WIDTH{1'b0}};

end

endgenerate

eth_mac_10g #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_WIDTH(KEEP_WIDTH),

.CTRL_WIDTH(CTRL_WIDTH),

.ENABLE_PADDING(ENABLE_PADDING),

.ENABLE_DIC(ENABLE_DIC),

.MIN_FRAME_LENGTH(MIN_FRAME_LENGTH),

.PTP_TS_ENABLE(PTP_TS_ENABLE),

.PTP_TS_FMT_TOD(PTP_TS_FMT_TOD),

.PTP_TS_WIDTH(PTP_TS_WIDTH),

.TX_PTP_TS_CTRL_IN_TUSER(TX_PTP_TS_CTRL_IN_TUSER),

.TX_PTP_TAG_ENABLE(TX_PTP_TAG_ENABLE),

.TX_PTP_TAG_WIDTH(PTP_TAG_WIDTH),

.TX_USER_WIDTH(TX_USER_WIDTH),

.RX_USER_WIDTH(RX_USER_WIDTH)

)

eth_mac_10g_inst (

.tx_clk(tx_clk),

.tx_rst(tx_rst),

.rx_clk(rx_clk),

.rx_rst(rx_rst),

.tx_axis_tdata(tx_fifo_axis_tdata),

.tx_axis_tkeep(tx_fifo_axis_tkeep),

.tx_axis_tvalid(tx_fifo_axis_tvalid),

.tx_axis_tready(tx_fifo_axis_tready),

.tx_axis_tlast(tx_fifo_axis_tlast),

.tx_axis_tuser(tx_fifo_axis_tuser),

.rx_axis_tdata(rx_fifo_axis_tdata),

.rx_axis_tkeep(rx_fifo_axis_tkeep),

.rx_axis_tvalid(rx_fifo_axis_tvalid),

.rx_axis_tlast(rx_fifo_axis_tlast),

.rx_axis_tuser(rx_fifo_axis_tuser),

.xgmii_rxd(xgmii_rxd),

.xgmii_rxc(xgmii_rxc),

.xgmii_txd(xgmii_txd),

.xgmii_txc(xgmii_txc),

.tx_ptp_ts(tx_ptp_ts_96),

.rx_ptp_ts(rx_ptp_ts_96),

.tx_axis_ptp_ts(tx_axis_ptp_ts_96),

.tx_axis_ptp_ts_tag(tx_axis_ptp_ts_tag),

.tx_axis_ptp_ts_valid(tx_axis_ptp_ts_valid),

.tx_error_underflow(tx_error_underflow_int),

.rx_error_bad_frame(rx_error_bad_frame_int),

.rx_error_bad_fcs(rx_error_bad_fcs_int),

.cfg_ifg(cfg_ifg),

.cfg_tx_enable(cfg_tx_enable),

.cfg_rx_enable(cfg_rx_enable)

);

axis_async_fifo_adapter #(

.DEPTH(TX_FIFO_DEPTH),

.S_DATA_WIDTH(AXIS_DATA_WIDTH),

.S_KEEP_ENABLE(AXIS_KEEP_ENABLE),

.S_KEEP_WIDTH(AXIS_KEEP_WIDTH),

.M_DATA_WIDTH(DATA_WIDTH),

.M_KEEP_ENABLE(1),

.M_KEEP_WIDTH(KEEP_WIDTH),

.ID_ENABLE(0),

.DEST_ENABLE(0),

.USER_ENABLE(1),

.USER_WIDTH(TX_USER_WIDTH),

.RAM_PIPELINE(TX_FIFO_RAM_PIPELINE),

.FRAME_FIFO(TX_FRAME_FIFO),

.USER_BAD_FRAME_VALUE(1'b1),

.USER_BAD_FRAME_MASK(1'b1),

.DROP_OVERSIZE_FRAME(TX_DROP_OVERSIZE_FRAME),

.DROP_BAD_FRAME(TX_DROP_BAD_FRAME),

.DROP_WHEN_FULL(TX_DROP_WHEN_FULL)

)

tx_fifo (

// AXI input

.s_clk(logic_clk),

.s_rst(logic_rst),

.s_axis_tdata(tx_axis_tdata),

.s_axis_tkeep(tx_axis_tkeep),

.s_axis_tvalid(tx_axis_tvalid),

.s_axis_tready(tx_axis_tready),

.s_axis_tlast(tx_axis_tlast),

.s_axis_tid(0),

.s_axis_tdest(0),

.s_axis_tuser(tx_axis_tuser),

// AXI output

.m_clk(tx_clk),

.m_rst(tx_rst),

.m_axis_tdata(tx_fifo_axis_tdata),

.m_axis_tkeep(tx_fifo_axis_tkeep),

.m_axis_tvalid(tx_fifo_axis_tvalid),

.m_axis_tready(tx_fifo_axis_tready),

.m_axis_tlast(tx_fifo_axis_tlast),

.m_axis_tid(),

.m_axis_tdest(),

.m_axis_tuser(tx_fifo_axis_tuser),

// Status

.s_status_overflow(tx_fifo_overflow),

.s_status_bad_frame(tx_fifo_bad_frame),

.s_status_good_frame(tx_fifo_good_frame),

.m_status_overflow(),

.m_status_bad_frame(),

.m_status_good_frame()

);

axis_async_fifo_adapter #(

.DEPTH(RX_FIFO_DEPTH),

.S_DATA_WIDTH(DATA_WIDTH),

.S_KEEP_ENABLE(1),

.S_KEEP_WIDTH(KEEP_WIDTH),

.M_DATA_WIDTH(AXIS_DATA_WIDTH),

.M_KEEP_ENABLE(AXIS_KEEP_ENABLE),

.M_KEEP_WIDTH(AXIS_KEEP_WIDTH),

.ID_ENABLE(0),

.DEST_ENABLE(0),

.USER_ENABLE(1),

.USER_WIDTH(RX_USER_WIDTH),

.RAM_PIPELINE(RX_FIFO_RAM_PIPELINE),

.FRAME_FIFO(RX_FRAME_FIFO),

.USER_BAD_FRAME_VALUE(1'b1),

.USER_BAD_FRAME_MASK(1'b1),

.DROP_OVERSIZE_FRAME(RX_DROP_OVERSIZE_FRAME),

.DROP_BAD_FRAME(RX_DROP_BAD_FRAME),

.DROP_WHEN_FULL(RX_DROP_WHEN_FULL)

)

rx_fifo (

// AXI input

.s_clk(rx_clk),

.s_rst(rx_rst),

.s_axis_tdata(rx_fifo_axis_tdata),

.s_axis_tkeep(rx_fifo_axis_tkeep),

.s_axis_tvalid(rx_fifo_axis_tvalid),

.s_axis_tready(),

.s_axis_tlast(rx_fifo_axis_tlast),

.s_axis_tid(0),

.s_axis_tdest(0),

.s_axis_tuser(rx_fifo_axis_tuser),

// AXI output

.m_clk(logic_clk),

.m_rst(logic_rst),

.m_axis_tdata(rx_axis_tdata),

.m_axis_tkeep(rx_axis_tkeep),

.m_axis_tvalid(rx_axis_tvalid),

.m_axis_tready(rx_axis_tready),

.m_axis_tlast(rx_axis_tlast),

.m_axis_tid(),

.m_axis_tdest(),

.m_axis_tuser(rx_axis_tuser),

// Status

.s_status_overflow(),

.s_status_bad_frame(),

.s_status_good_frame(),

.m_status_overflow(rx_fifo_overflow),

.m_status_bad_frame(rx_fifo_bad_frame),

.m_status_good_frame(rx_fifo_good_frame)

);

endmodule

`resetall

点击查看代码

/*

Copyright (c) 2015-2023 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* 10G Ethernet MAC

*/

module eth_mac_10g #

(

parameter DATA_WIDTH = 64,

parameter KEEP_WIDTH = (DATA_WIDTH/8),

parameter CTRL_WIDTH = (DATA_WIDTH/8),

parameter ENABLE_PADDING = 1,

parameter ENABLE_DIC = 1,

parameter MIN_FRAME_LENGTH = 64,

parameter PTP_TS_ENABLE = 0,

parameter PTP_TS_FMT_TOD = 1,

parameter PTP_TS_WIDTH = PTP_TS_FMT_TOD ? 96 : 64,

parameter TX_PTP_TS_CTRL_IN_TUSER = 0,

parameter TX_PTP_TAG_ENABLE = PTP_TS_ENABLE,

parameter TX_PTP_TAG_WIDTH = 16,

parameter TX_USER_WIDTH = (PTP_TS_ENABLE ? (TX_PTP_TAG_ENABLE ? TX_PTP_TAG_WIDTH : 0) + (TX_PTP_TS_CTRL_IN_TUSER ? 1 : 0) : 0) + 1,

parameter RX_USER_WIDTH = (PTP_TS_ENABLE ? PTP_TS_WIDTH : 0) + 1,

parameter PFC_ENABLE = 0,

parameter PAUSE_ENABLE = PFC_ENABLE

)

(

input wire rx_clk,

input wire rx_rst,

input wire tx_clk,

input wire tx_rst,

/*

* AXI input

*/

input wire [DATA_WIDTH-1:0] tx_axis_tdata,

input wire [KEEP_WIDTH-1:0] tx_axis_tkeep,

input wire tx_axis_tvalid,

output wire tx_axis_tready,

input wire tx_axis_tlast,

input wire [TX_USER_WIDTH-1:0] tx_axis_tuser,

/*

* AXI output

*/

output wire [DATA_WIDTH-1:0] rx_axis_tdata,

output wire [KEEP_WIDTH-1:0] rx_axis_tkeep,

output wire rx_axis_tvalid,

output wire rx_axis_tlast,

output wire [RX_USER_WIDTH-1:0] rx_axis_tuser,

/*

* XGMII interface

*/

input wire [DATA_WIDTH-1:0] xgmii_rxd,

input wire [CTRL_WIDTH-1:0] xgmii_rxc,

output wire [DATA_WIDTH-1:0] xgmii_txd,

output wire [CTRL_WIDTH-1:0] xgmii_txc,

/*

* PTP

*/

input wire [PTP_TS_WIDTH-1:0] tx_ptp_ts,

input wire [PTP_TS_WIDTH-1:0] rx_ptp_ts,

output wire [PTP_TS_WIDTH-1:0] tx_axis_ptp_ts,

output wire [TX_PTP_TAG_WIDTH-1:0] tx_axis_ptp_ts_tag,

output wire tx_axis_ptp_ts_valid,

/*

* Link-level Flow Control (LFC) (IEEE 802.3 annex 31B PAUSE)

*/

input wire tx_lfc_req,

input wire tx_lfc_resend,

input wire rx_lfc_en,

output wire rx_lfc_req,

input wire rx_lfc_ack,

/*

* Priority Flow Control (PFC) (IEEE 802.3 annex 31D PFC)

*/

input wire [7:0] tx_pfc_req,

input wire tx_pfc_resend,

input wire [7:0] rx_pfc_en,

output wire [7:0] rx_pfc_req,

input wire [7:0] rx_pfc_ack,

/*

* Pause interface

*/

input wire tx_lfc_pause_en,

input wire tx_pause_req,

output wire tx_pause_ack,

/*

* Status

*/

output wire [1:0] tx_start_packet,

output wire tx_error_underflow,

output wire [1:0] rx_start_packet,

output wire rx_error_bad_frame,

output wire rx_error_bad_fcs,

output wire stat_tx_mcf,

output wire stat_rx_mcf,

output wire stat_tx_lfc_pkt,

output wire stat_tx_lfc_xon,

output wire stat_tx_lfc_xoff,

output wire stat_tx_lfc_paused,

output wire stat_tx_pfc_pkt,

output wire [7:0] stat_tx_pfc_xon,

output wire [7:0] stat_tx_pfc_xoff,

output wire [7:0] stat_tx_pfc_paused,

output wire stat_rx_lfc_pkt,

output wire stat_rx_lfc_xon,

output wire stat_rx_lfc_xoff,

output wire stat_rx_lfc_paused,

output wire stat_rx_pfc_pkt,

output wire [7:0] stat_rx_pfc_xon,

output wire [7:0] stat_rx_pfc_xoff,

output wire [7:0] stat_rx_pfc_paused,

/*

* Configuration

*/

input wire [7:0] cfg_ifg,

input wire cfg_tx_enable,

input wire cfg_rx_enable,

input wire [47:0] cfg_mcf_rx_eth_dst_mcast,

input wire cfg_mcf_rx_check_eth_dst_mcast,

input wire [47:0] cfg_mcf_rx_eth_dst_ucast,

input wire cfg_mcf_rx_check_eth_dst_ucast,

input wire [47:0] cfg_mcf_rx_eth_src,

input wire cfg_mcf_rx_check_eth_src,

input wire [15:0] cfg_mcf_rx_eth_type,

input wire [15:0] cfg_mcf_rx_opcode_lfc,

input wire cfg_mcf_rx_check_opcode_lfc,

input wire [15:0] cfg_mcf_rx_opcode_pfc,

input wire cfg_mcf_rx_check_opcode_pfc,

input wire cfg_mcf_rx_forward,

input wire cfg_mcf_rx_enable,

input wire [47:0] cfg_tx_lfc_eth_dst,

input wire [47:0] cfg_tx_lfc_eth_src,

input wire [15:0] cfg_tx_lfc_eth_type,

input wire [15:0] cfg_tx_lfc_opcode,

input wire cfg_tx_lfc_en,

input wire [15:0] cfg_tx_lfc_quanta,

input wire [15:0] cfg_tx_lfc_refresh,

input wire [47:0] cfg_tx_pfc_eth_dst,

input wire [47:0] cfg_tx_pfc_eth_src,

input wire [15:0] cfg_tx_pfc_eth_type,

input wire [15:0] cfg_tx_pfc_opcode,

input wire cfg_tx_pfc_en,

input wire [8*16-1:0] cfg_tx_pfc_quanta,

input wire [8*16-1:0] cfg_tx_pfc_refresh,

input wire [15:0] cfg_rx_lfc_opcode,

input wire cfg_rx_lfc_en,

input wire [15:0] cfg_rx_pfc_opcode,

input wire cfg_rx_pfc_en

);

parameter MAC_CTRL_ENABLE = PAUSE_ENABLE || PFC_ENABLE;

parameter TX_USER_WIDTH_INT = MAC_CTRL_ENABLE ? (PTP_TS_ENABLE ? (TX_PTP_TAG_ENABLE ? TX_PTP_TAG_WIDTH : 0) + 1 : 0) + 1 : TX_USER_WIDTH;

// bus width assertions

initial begin

if (DATA_WIDTH != 32 && DATA_WIDTH != 64) begin

$error("Error: Interface width must be 32 or 64");

$finish;

end

if (KEEP_WIDTH * 8 != DATA_WIDTH || CTRL_WIDTH * 8 != DATA_WIDTH) begin

$error("Error: Interface requires byte (8-bit) granularity");

$finish;

end

end

wire [DATA_WIDTH-1:0] tx_axis_tdata_int;

wire [KEEP_WIDTH-1:0] tx_axis_tkeep_int;

wire tx_axis_tvalid_int;

wire tx_axis_tready_int;

wire tx_axis_tlast_int;

wire [TX_USER_WIDTH_INT-1:0] tx_axis_tuser_int;

wire [DATA_WIDTH-1:0] rx_axis_tdata_int;

wire [KEEP_WIDTH-1:0] rx_axis_tkeep_int;

wire rx_axis_tvalid_int;

wire rx_axis_tlast_int;

wire [RX_USER_WIDTH-1:0] rx_axis_tuser_int;

generate

if (DATA_WIDTH == 64) begin

axis_xgmii_rx_64 #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_WIDTH(KEEP_WIDTH),

.CTRL_WIDTH(CTRL_WIDTH),

.PTP_TS_ENABLE(PTP_TS_ENABLE),

.PTP_TS_FMT_TOD(PTP_TS_FMT_TOD),

.PTP_TS_WIDTH(PTP_TS_WIDTH),

.USER_WIDTH(RX_USER_WIDTH)

)

axis_xgmii_rx_inst (

.clk(rx_clk),

.rst(rx_rst),

.xgmii_rxd(xgmii_rxd),

.xgmii_rxc(xgmii_rxc),

.m_axis_tdata(rx_axis_tdata_int),

.m_axis_tkeep(rx_axis_tkeep_int),

.m_axis_tvalid(rx_axis_tvalid_int),

.m_axis_tlast(rx_axis_tlast_int),

.m_axis_tuser(rx_axis_tuser_int),

.ptp_ts(rx_ptp_ts),

.cfg_rx_enable(cfg_rx_enable),

.start_packet(rx_start_packet),

.error_bad_frame(rx_error_bad_frame),

.error_bad_fcs(rx_error_bad_fcs)

);

axis_xgmii_tx_64 #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_WIDTH(KEEP_WIDTH),

.CTRL_WIDTH(CTRL_WIDTH),

.ENABLE_PADDING(ENABLE_PADDING),

.ENABLE_DIC(ENABLE_DIC),

.MIN_FRAME_LENGTH(MIN_FRAME_LENGTH),

.PTP_TS_ENABLE(PTP_TS_ENABLE),

.PTP_TS_FMT_TOD(PTP_TS_FMT_TOD),

.PTP_TS_WIDTH(PTP_TS_WIDTH),

.PTP_TS_CTRL_IN_TUSER(MAC_CTRL_ENABLE ? PTP_TS_ENABLE : TX_PTP_TS_CTRL_IN_TUSER),

.PTP_TAG_ENABLE(TX_PTP_TAG_ENABLE),

.PTP_TAG_WIDTH(TX_PTP_TAG_WIDTH),

.USER_WIDTH(TX_USER_WIDTH_INT)

)

axis_xgmii_tx_inst (

.clk(tx_clk),

.rst(tx_rst),

.s_axis_tdata(tx_axis_tdata_int),

.s_axis_tkeep(tx_axis_tkeep_int),

.s_axis_tvalid(tx_axis_tvalid_int),

.s_axis_tready(tx_axis_tready_int),

.s_axis_tlast(tx_axis_tlast_int),

.s_axis_tuser(tx_axis_tuser_int),

.xgmii_txd(xgmii_txd),

.xgmii_txc(xgmii_txc),

.ptp_ts(tx_ptp_ts),

.m_axis_ptp_ts(tx_axis_ptp_ts),

.m_axis_ptp_ts_tag(tx_axis_ptp_ts_tag),

.m_axis_ptp_ts_valid(tx_axis_ptp_ts_valid),

.cfg_ifg(cfg_ifg),

.cfg_tx_enable(cfg_tx_enable),

.start_packet(tx_start_packet),

.error_underflow(tx_error_underflow)

);

end else begin

axis_xgmii_rx_32 #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_WIDTH(KEEP_WIDTH),

.CTRL_WIDTH(CTRL_WIDTH),

.PTP_TS_ENABLE(PTP_TS_ENABLE),

.PTP_TS_WIDTH(PTP_TS_WIDTH),

.USER_WIDTH(RX_USER_WIDTH)

)

axis_xgmii_rx_inst (

.clk(rx_clk),

.rst(rx_rst),

.xgmii_rxd(xgmii_rxd),

.xgmii_rxc(xgmii_rxc),

.m_axis_tdata(rx_axis_tdata_int),

.m_axis_tkeep(rx_axis_tkeep_int),

.m_axis_tvalid(rx_axis_tvalid_int),

.m_axis_tlast(rx_axis_tlast_int),

.m_axis_tuser(rx_axis_tuser_int),

.ptp_ts(rx_ptp_ts),

.cfg_rx_enable(cfg_rx_enable),

.start_packet(rx_start_packet[0]),

.error_bad_frame(rx_error_bad_frame),

.error_bad_fcs(rx_error_bad_fcs)

);

assign rx_start_packet[1] = 1'b0;

axis_xgmii_tx_32 #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_WIDTH(KEEP_WIDTH),

.CTRL_WIDTH(CTRL_WIDTH),

.ENABLE_PADDING(ENABLE_PADDING),

.ENABLE_DIC(ENABLE_DIC),

.MIN_FRAME_LENGTH(MIN_FRAME_LENGTH),

.PTP_TS_ENABLE(PTP_TS_ENABLE),

.PTP_TS_WIDTH(PTP_TS_WIDTH),

.PTP_TS_CTRL_IN_TUSER(MAC_CTRL_ENABLE ? PTP_TS_ENABLE : TX_PTP_TS_CTRL_IN_TUSER),

.PTP_TAG_ENABLE(TX_PTP_TAG_ENABLE),

.PTP_TAG_WIDTH(TX_PTP_TAG_WIDTH),

.USER_WIDTH(TX_USER_WIDTH_INT)

)

axis_xgmii_tx_inst (

.clk(tx_clk),

.rst(tx_rst),

.s_axis_tdata(tx_axis_tdata_int),

.s_axis_tkeep(tx_axis_tkeep_int),

.s_axis_tvalid(tx_axis_tvalid_int),

.s_axis_tready(tx_axis_tready_int),

.s_axis_tlast(tx_axis_tlast_int),

.s_axis_tuser(tx_axis_tuser_int),

.xgmii_txd(xgmii_txd),

.xgmii_txc(xgmii_txc),

.ptp_ts(tx_ptp_ts),

.m_axis_ptp_ts(tx_axis_ptp_ts),

.m_axis_ptp_ts_tag(tx_axis_ptp_ts_tag),

.m_axis_ptp_ts_valid(tx_axis_ptp_ts_valid),

.cfg_ifg(cfg_ifg),

.cfg_tx_enable(cfg_tx_enable),

.start_packet(tx_start_packet[0]),

.error_underflow(tx_error_underflow)

);

assign tx_start_packet[1] = 1'b0;

end

if (MAC_CTRL_ENABLE) begin : mac_ctrl

localparam MCF_PARAMS_SIZE = PFC_ENABLE ? 18 : 2;

wire tx_mcf_valid;

wire tx_mcf_ready;

wire [47:0] tx_mcf_eth_dst;

wire [47:0] tx_mcf_eth_src;

wire [15:0] tx_mcf_eth_type;

wire [15:0] tx_mcf_opcode;

wire [MCF_PARAMS_SIZE*8-1:0] tx_mcf_params;

wire rx_mcf_valid;

wire [47:0] rx_mcf_eth_dst;

wire [47:0] rx_mcf_eth_src;

wire [15:0] rx_mcf_eth_type;

wire [15:0] rx_mcf_opcode;

wire [MCF_PARAMS_SIZE*8-1:0] rx_mcf_params;

// terminate LFC pause requests from RX internally on TX side

wire tx_pause_req_int;

wire rx_lfc_ack_int;

reg tx_lfc_req_sync_reg_1 = 1'b0;

reg tx_lfc_req_sync_reg_2 = 1'b0;

reg tx_lfc_req_sync_reg_3 = 1'b0;

always @(posedge rx_clk or posedge rx_rst) begin

if (rx_rst) begin

tx_lfc_req_sync_reg_1 <= 1'b0;

end else begin

tx_lfc_req_sync_reg_1 <= rx_lfc_req;

end

end

always @(posedge tx_clk or posedge tx_rst) begin

if (tx_rst) begin

tx_lfc_req_sync_reg_2 <= 1'b0;

tx_lfc_req_sync_reg_3 <= 1'b0;

end else begin

tx_lfc_req_sync_reg_2 <= tx_lfc_req_sync_reg_1;

tx_lfc_req_sync_reg_3 <= tx_lfc_req_sync_reg_2;

end

end

reg rx_lfc_ack_sync_reg_1 = 1'b0;

reg rx_lfc_ack_sync_reg_2 = 1'b0;

reg rx_lfc_ack_sync_reg_3 = 1'b0;

always @(posedge tx_clk or posedge tx_rst) begin

if (tx_rst) begin

rx_lfc_ack_sync_reg_1 <= 1'b0;

end else begin

rx_lfc_ack_sync_reg_1 <= tx_lfc_pause_en ? tx_pause_ack : 0;

end

end

always @(posedge rx_clk or posedge rx_rst) begin

if (rx_rst) begin

rx_lfc_ack_sync_reg_2 <= 1'b0;

rx_lfc_ack_sync_reg_3 <= 1'b0;

end else begin

rx_lfc_ack_sync_reg_2 <= rx_lfc_ack_sync_reg_1;

rx_lfc_ack_sync_reg_3 <= rx_lfc_ack_sync_reg_2;

end

end

assign tx_pause_req_int = tx_pause_req || (tx_lfc_pause_en ? tx_lfc_req_sync_reg_3 : 0);

assign rx_lfc_ack_int = rx_lfc_ack || rx_lfc_ack_sync_reg_3;

// handle PTP TS enable bit in tuser

wire [TX_USER_WIDTH_INT-1:0] tx_axis_tuser_in;

if (PTP_TS_ENABLE && !TX_PTP_TS_CTRL_IN_TUSER) begin

assign tx_axis_tuser_in = {tx_axis_tuser[TX_USER_WIDTH-1:1], 1'b1, tx_axis_tuser[0]};

end else begin

assign tx_axis_tuser_in = tx_axis_tuser;

end

mac_ctrl_tx #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_ENABLE(1),

.KEEP_WIDTH(KEEP_WIDTH),

.ID_ENABLE(0),

.DEST_ENABLE(0),

.USER_ENABLE(1),

.USER_WIDTH(TX_USER_WIDTH_INT),

.MCF_PARAMS_SIZE(MCF_PARAMS_SIZE)

)

mac_ctrl_tx_inst (

.clk(tx_clk),

.rst(tx_rst),

/*

* AXI stream input

*/

.s_axis_tdata(tx_axis_tdata),

.s_axis_tkeep(tx_axis_tkeep),

.s_axis_tvalid(tx_axis_tvalid),

.s_axis_tready(tx_axis_tready),

.s_axis_tlast(tx_axis_tlast),

.s_axis_tid(0),

.s_axis_tdest(0),

.s_axis_tuser(tx_axis_tuser_in),

/*

* AXI stream output

*/

.m_axis_tdata(tx_axis_tdata_int),

.m_axis_tkeep(tx_axis_tkeep_int),

.m_axis_tvalid(tx_axis_tvalid_int),

.m_axis_tready(tx_axis_tready_int),

.m_axis_tlast(tx_axis_tlast_int),

.m_axis_tid(),

.m_axis_tdest(),

.m_axis_tuser(tx_axis_tuser_int),

/*

* MAC control frame interface

*/

.mcf_valid(tx_mcf_valid),

.mcf_ready(tx_mcf_ready),

.mcf_eth_dst(tx_mcf_eth_dst),

.mcf_eth_src(tx_mcf_eth_src),

.mcf_eth_type(tx_mcf_eth_type),

.mcf_opcode(tx_mcf_opcode),

.mcf_params(tx_mcf_params),

.mcf_id(0),

.mcf_dest(0),

.mcf_user(0),

/*

* Pause interface

*/

.tx_pause_req(tx_pause_req_int),

.tx_pause_ack(tx_pause_ack),

/*

* Status

*/

.stat_tx_mcf(stat_tx_mcf)

);

mac_ctrl_rx #(

.DATA_WIDTH(DATA_WIDTH),

.KEEP_ENABLE(1),

.KEEP_WIDTH(KEEP_WIDTH),

.ID_ENABLE(0),

.DEST_ENABLE(0),

.USER_ENABLE(1),

.USER_WIDTH(RX_USER_WIDTH),

.USE_READY(0),

.MCF_PARAMS_SIZE(MCF_PARAMS_SIZE)

)

mac_ctrl_rx_inst (

.clk(rx_clk),

.rst(rx_rst),

/*

* AXI stream input

*/

.s_axis_tdata(rx_axis_tdata_int),

.s_axis_tkeep(rx_axis_tkeep_int),

.s_axis_tvalid(rx_axis_tvalid_int),

.s_axis_tready(),

.s_axis_tlast(rx_axis_tlast_int),

.s_axis_tid(0),

.s_axis_tdest(0),

.s_axis_tuser(rx_axis_tuser_int),

/*

* AXI stream output

*/

.m_axis_tdata(rx_axis_tdata),

.m_axis_tkeep(rx_axis_tkeep),

.m_axis_tvalid(rx_axis_tvalid),

.m_axis_tready(1'b1),

.m_axis_tlast(rx_axis_tlast),

.m_axis_tid(),

.m_axis_tdest(),

.m_axis_tuser(rx_axis_tuser),

/*

* MAC control frame interface

*/

.mcf_valid(rx_mcf_valid),

.mcf_eth_dst(rx_mcf_eth_dst),

.mcf_eth_src(rx_mcf_eth_src),

.mcf_eth_type(rx_mcf_eth_type),

.mcf_opcode(rx_mcf_opcode),

.mcf_params(rx_mcf_params),

.mcf_id(),

.mcf_dest(),

.mcf_user(),

/*

* Configuration

*/

.cfg_mcf_rx_eth_dst_mcast(cfg_mcf_rx_eth_dst_mcast),

.cfg_mcf_rx_check_eth_dst_mcast(cfg_mcf_rx_check_eth_dst_mcast),

.cfg_mcf_rx_eth_dst_ucast(cfg_mcf_rx_eth_dst_ucast),

.cfg_mcf_rx_check_eth_dst_ucast(cfg_mcf_rx_check_eth_dst_ucast),

.cfg_mcf_rx_eth_src(cfg_mcf_rx_eth_src),

.cfg_mcf_rx_check_eth_src(cfg_mcf_rx_check_eth_src),

.cfg_mcf_rx_eth_type(cfg_mcf_rx_eth_type),

.cfg_mcf_rx_opcode_lfc(cfg_mcf_rx_opcode_lfc),

.cfg_mcf_rx_check_opcode_lfc(cfg_mcf_rx_check_opcode_lfc),

.cfg_mcf_rx_opcode_pfc(cfg_mcf_rx_opcode_pfc),

.cfg_mcf_rx_check_opcode_pfc(cfg_mcf_rx_check_opcode_pfc && PFC_ENABLE),

.cfg_mcf_rx_forward(cfg_mcf_rx_forward),

.cfg_mcf_rx_enable(cfg_mcf_rx_enable),

/*

* Status

*/

.stat_rx_mcf(stat_rx_mcf)

);

mac_pause_ctrl_tx #(

.MCF_PARAMS_SIZE(MCF_PARAMS_SIZE),

.PFC_ENABLE(PFC_ENABLE)

)

mac_pause_ctrl_tx_inst (

.clk(tx_clk),

.rst(tx_rst),

/*

* MAC control frame interface

*/

.mcf_valid(tx_mcf_valid),

.mcf_ready(tx_mcf_ready),

.mcf_eth_dst(tx_mcf_eth_dst),

.mcf_eth_src(tx_mcf_eth_src),

.mcf_eth_type(tx_mcf_eth_type),

.mcf_opcode(tx_mcf_opcode),

.mcf_params(tx_mcf_params),

/*

* Pause (IEEE 802.3 annex 31B)

*/

.tx_lfc_req(tx_lfc_req),

.tx_lfc_resend(tx_lfc_resend),

/*

* Priority Flow Control (PFC) (IEEE 802.3 annex 31D)

*/

.tx_pfc_req(tx_pfc_req),

.tx_pfc_resend(tx_pfc_resend),

/*

* Configuration

*/

.cfg_tx_lfc_eth_dst(cfg_tx_lfc_eth_dst),

.cfg_tx_lfc_eth_src(cfg_tx_lfc_eth_src),

.cfg_tx_lfc_eth_type(cfg_tx_lfc_eth_type),

.cfg_tx_lfc_opcode(cfg_tx_lfc_opcode),

.cfg_tx_lfc_en(cfg_tx_lfc_en),

.cfg_tx_lfc_quanta(cfg_tx_lfc_quanta),

.cfg_tx_lfc_refresh(cfg_tx_lfc_refresh),

.cfg_tx_pfc_eth_dst(cfg_tx_pfc_eth_dst),

.cfg_tx_pfc_eth_src(cfg_tx_pfc_eth_src),

.cfg_tx_pfc_eth_type(cfg_tx_pfc_eth_type),

.cfg_tx_pfc_opcode(cfg_tx_pfc_opcode),

.cfg_tx_pfc_en(cfg_tx_pfc_en),

.cfg_tx_pfc_quanta(cfg_tx_pfc_quanta),

.cfg_tx_pfc_refresh(cfg_tx_pfc_refresh),

.cfg_quanta_step((DATA_WIDTH*256)/512),

.cfg_quanta_clk_en(1'b1),

/*

* Status

*/

.stat_tx_lfc_pkt(stat_tx_lfc_pkt),

.stat_tx_lfc_xon(stat_tx_lfc_xon),

.stat_tx_lfc_xoff(stat_tx_lfc_xoff),

.stat_tx_lfc_paused(stat_tx_lfc_paused),

.stat_tx_pfc_pkt(stat_tx_pfc_pkt),

.stat_tx_pfc_xon(stat_tx_pfc_xon),

.stat_tx_pfc_xoff(stat_tx_pfc_xoff),

.stat_tx_pfc_paused(stat_tx_pfc_paused)

);

mac_pause_ctrl_rx #(

.MCF_PARAMS_SIZE(18),

.PFC_ENABLE(PFC_ENABLE)

)

mac_pause_ctrl_rx_inst (

.clk(rx_clk),

.rst(rx_rst),

/*

* MAC control frame interface

*/

.mcf_valid(rx_mcf_valid),

.mcf_eth_dst(rx_mcf_eth_dst),

.mcf_eth_src(rx_mcf_eth_src),

.mcf_eth_type(rx_mcf_eth_type),

.mcf_opcode(rx_mcf_opcode),

.mcf_params(rx_mcf_params),

/*

* Pause (IEEE 802.3 annex 31B)

*/

.rx_lfc_en(rx_lfc_en),

.rx_lfc_req(rx_lfc_req),

.rx_lfc_ack(rx_lfc_ack_int),

/*

* Priority Flow Control (PFC) (IEEE 802.3 annex 31D)

*/

.rx_pfc_en(rx_pfc_en),

.rx_pfc_req(rx_pfc_req),

.rx_pfc_ack(rx_pfc_ack),

/*

* Configuration

*/

.cfg_rx_lfc_opcode(cfg_rx_lfc_opcode),

.cfg_rx_lfc_en(cfg_rx_lfc_en),

.cfg_rx_pfc_opcode(cfg_rx_pfc_opcode),

.cfg_rx_pfc_en(cfg_rx_pfc_en),

.cfg_quanta_step((DATA_WIDTH*256)/512),

.cfg_quanta_clk_en(1'b1),

/*

* Status

*/

.stat_rx_lfc_pkt(stat_rx_lfc_pkt),

.stat_rx_lfc_xon(stat_rx_lfc_xon),

.stat_rx_lfc_xoff(stat_rx_lfc_xoff),

.stat_rx_lfc_paused(stat_rx_lfc_paused),

.stat_rx_pfc_pkt(stat_rx_pfc_pkt),

.stat_rx_pfc_xon(stat_rx_pfc_xon),

.stat_rx_pfc_xoff(stat_rx_pfc_xoff),

.stat_rx_pfc_paused(stat_rx_pfc_paused)

);

end else begin

assign tx_axis_tdata_int = tx_axis_tdata;

assign tx_axis_tkeep_int = tx_axis_tkeep;

assign tx_axis_tvalid_int = tx_axis_tvalid;

assign tx_axis_tready = tx_axis_tready_int;

assign tx_axis_tlast_int = tx_axis_tlast;

assign tx_axis_tuser_int = tx_axis_tuser;

assign rx_axis_tdata = rx_axis_tdata_int;

assign rx_axis_tkeep = rx_axis_tkeep_int;

assign rx_axis_tvalid = rx_axis_tvalid_int;

assign rx_axis_tlast = rx_axis_tlast_int;

assign rx_axis_tuser = rx_axis_tuser_int;

assign rx_lfc_req = 0;

assign rx_pfc_req = 0;

assign tx_pause_ack = 0;

assign stat_tx_mcf = 0;

assign stat_rx_mcf = 0;

assign stat_tx_lfc_pkt = 0;

assign stat_tx_lfc_xon = 0;

assign stat_tx_lfc_xoff = 0;

assign stat_tx_lfc_paused = 0;

assign stat_tx_pfc_pkt = 0;

assign stat_tx_pfc_xon = 0;

assign stat_tx_pfc_xoff = 0;

assign stat_tx_pfc_paused = 0;

assign stat_rx_lfc_pkt = 0;

assign stat_rx_lfc_xon = 0;

assign stat_rx_lfc_xoff = 0;

assign stat_rx_lfc_paused = 0;

assign stat_rx_pfc_pkt = 0;

assign stat_rx_pfc_xon = 0;

assign stat_rx_pfc_xoff = 0;

assign stat_rx_pfc_paused = 0;

end

endgenerate

endmodule

`resetall

浙公网安备 33010602011771号

浙公网安备 33010602011771号