万兆以太网udp学习(一)

链接在上面,这里我们学习ZCU106的例程

顶层,简单概括就是,逻辑时钟125MHz,逻辑复位,外部按键,输出指示灯,串口,高速收发器,高速收发器参考时钟,以及两个固定为1的disable,暂时不知道用途。

时钟方面不多做介绍,对于万兆来讲,时钟是156.25MHz,66/64b编码,所以物理层实际速率是10.3125G,下面是核心模块,所有输入接口都做过同步处理,要注意的是,里面其实只用到了一个10G接口,所以sfp1相关的后面移植的时候可以删掉。

进入fpga_core,里面实现了mac层、链路和传输层,以及应用层,mac层是通过mac_10g_fifo实现的,具体接口如下,采用AXI4 Stream接口交互,带有缓冲fifo,实现以太网协议帧的提取。

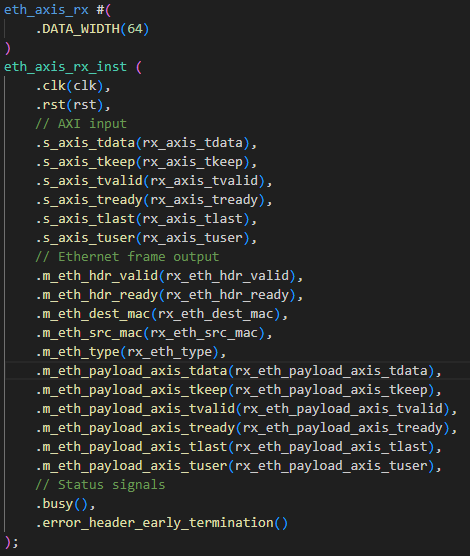

接收的AXI4 Stream数据流会给到eth_axis_rx模块,该模块实现了以太网协议分层输出以太网协议中的目的mac地址,源mac地址、以太网协议类别、以及后续相关数据。

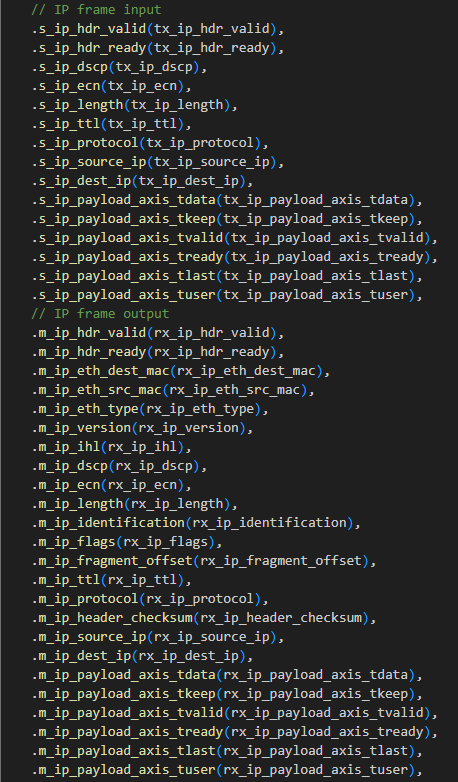

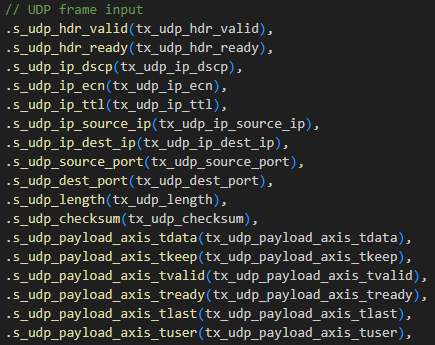

eth_axis_rx模块的输出会给到udp_complete_64模块,这个模块有点长,这里分作用区域显示,简单来讲实现了udp协议,里面进一步分开了IP部分和UDP数据部分,在发送部分也有本地mac地址接口和IP接口,这个一般是静态默认设置。

udp_complete_64模块解出来的最终数据会给到axis_fifo里。

axis_fifo的输出,又会给回udp_complete_64模块的UDP_frame_in接口,且地址端口啥的是保持接收原样的。

udp_complete_64模块的IP接口是不使用的,最终通过Ethernet frame output输出,进入eth_axis_tx模块。

eth_axis_tx模块的输出给到mac_10g_fifo,从而通过mii接口输出,形成回环,目前看来相比于千兆以太网来讲,只是在原协议层的基础上加了一层,这一层的解析在mac_10g_fifo里。

完整代码如下。

点击查看代码

/*

Copyright (c) 2020-2021 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* FPGA top-level module

*/

module fpga (

/*

* Clock: 125MHz LVDS

* Reset: Push button, active low

*/

input wire clk_125mhz_p,

input wire clk_125mhz_n,

input wire reset,

/*

* GPIO

*/

input wire btnu,

input wire btnl,

input wire btnd,

input wire btnr,

input wire btnc,

input wire [7:0] sw,

output wire [7:0] led,

/*

* UART: 115200 bps, 8N1

*/

input wire uart_rxd,

output wire uart_txd,

input wire uart_rts,

output wire uart_cts,

/*

* Ethernet: SFP+

*/

input wire sfp0_rx_p,

input wire sfp0_rx_n,

output wire sfp0_tx_p,

output wire sfp0_tx_n,

input wire sfp1_rx_p,

input wire sfp1_rx_n,

output wire sfp1_tx_p,

output wire sfp1_tx_n,

input wire sfp_mgt_refclk_0_p,

input wire sfp_mgt_refclk_0_n,

output wire sfp0_tx_disable_b,

output wire sfp1_tx_disable_b

);

// Clock and reset

wire clk_125mhz_ibufg;

// Internal 125 MHz clock

wire clk_125mhz_mmcm_out;

wire clk_125mhz_int;

wire rst_125mhz_int;

// Internal 156.25 MHz clock

wire clk_156mhz_int;

wire rst_156mhz_int;

wire mmcm_rst = reset;

wire mmcm_locked;

wire mmcm_clkfb;

IBUFGDS #(

.DIFF_TERM("FALSE"),

.IBUF_LOW_PWR("FALSE")

)

clk_125mhz_ibufg_inst (

.O (clk_125mhz_ibufg),

.I (clk_125mhz_p),

.IB (clk_125mhz_n)

);

// MMCM instance

// 125 MHz in, 125 MHz out

// PFD range: 10 MHz to 500 MHz

// VCO range: 800 MHz to 1600 MHz

// M = 8, D = 1 sets Fvco = 1000 MHz (in range)

// Divide by 8 to get output frequency of 125 MHz

MMCME4_BASE #(

.BANDWIDTH("OPTIMIZED"),

.CLKOUT0_DIVIDE_F(8),

.CLKOUT0_DUTY_CYCLE(0.5),

.CLKOUT0_PHASE(0),

.CLKOUT1_DIVIDE(1),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT1_PHASE(0),

.CLKOUT2_DIVIDE(1),

.CLKOUT2_DUTY_CYCLE(0.5),

.CLKOUT2_PHASE(0),

.CLKOUT3_DIVIDE(1),

.CLKOUT3_DUTY_CYCLE(0.5),

.CLKOUT3_PHASE(0),

.CLKOUT4_DIVIDE(1),

.CLKOUT4_DUTY_CYCLE(0.5),

.CLKOUT4_PHASE(0),

.CLKOUT5_DIVIDE(1),

.CLKOUT5_DUTY_CYCLE(0.5),

.CLKOUT5_PHASE(0),

.CLKOUT6_DIVIDE(1),

.CLKOUT6_DUTY_CYCLE(0.5),

.CLKOUT6_PHASE(0),

.CLKFBOUT_MULT_F(8),

.CLKFBOUT_PHASE(0),

.DIVCLK_DIVIDE(1),

.REF_JITTER1(0.010),

.CLKIN1_PERIOD(8.0),

.STARTUP_WAIT("FALSE"),

.CLKOUT4_CASCADE("FALSE")

)

clk_mmcm_inst (

.CLKIN1(clk_125mhz_ibufg),

.CLKFBIN(mmcm_clkfb),

.RST(mmcm_rst),

.PWRDWN(1'b0),

.CLKOUT0(clk_125mhz_mmcm_out),

.CLKOUT0B(),

.CLKOUT1(),

.CLKOUT1B(),

.CLKOUT2(),

.CLKOUT2B(),

.CLKOUT3(),

.CLKOUT3B(),

.CLKOUT4(),

.CLKOUT5(),

.CLKOUT6(),

.CLKFBOUT(mmcm_clkfb),

.CLKFBOUTB(),

.LOCKED(mmcm_locked)

);

BUFG

clk_125mhz_bufg_inst (

.I(clk_125mhz_mmcm_out),

.O(clk_125mhz_int)

);

sync_reset #(

.N(4)

)

sync_reset_125mhz_inst (

.clk(clk_125mhz_int),

.rst(~mmcm_locked),

.out(rst_125mhz_int)

);

// GPIO

wire btnu_int;

wire btnl_int;

wire btnd_int;

wire btnr_int;

wire btnc_int;

wire [7:0] sw_int;

debounce_switch #(

.WIDTH(9),

.N(8),

.RATE(156000)

)

debounce_switch_inst (

.clk(clk_156mhz_int),

.rst(rst_156mhz_int),

.in({btnu,

btnl,

btnd,

btnr,

btnc,

sw}),

.out({btnu_int,

btnl_int,

btnd_int,

btnr_int,

btnc_int,

sw_int})

);

wire uart_rxd_int;

wire uart_rts_int;

sync_signal #(

.WIDTH(2),

.N(2)

)

sync_signal_inst (

.clk(clk_156mhz_int),

.in({uart_rxd, uart_rts}),

.out({uart_rxd_int, uart_rts_int})

);

// XGMII 10G PHY

assign sfp0_tx_disable_b = 1'b1;

assign sfp1_tx_disable_b = 1'b1;

wire sfp0_tx_clk_int;

wire sfp0_tx_rst_int;

wire [63:0] sfp0_txd_int;

wire [7:0] sfp0_txc_int;

wire sfp0_rx_clk_int;

wire sfp0_rx_rst_int;

wire [63:0] sfp0_rxd_int;

wire [7:0] sfp0_rxc_int;

wire sfp1_tx_clk_int;

wire sfp1_tx_rst_int;

wire [63:0] sfp1_txd_int;

wire [7:0] sfp1_txc_int;

wire sfp1_rx_clk_int;

wire sfp1_rx_rst_int;

wire [63:0] sfp1_rxd_int;

wire [7:0] sfp1_rxc_int;

assign clk_156mhz_int = sfp0_tx_clk_int;

assign rst_156mhz_int = sfp0_tx_rst_int;

wire sfp0_rx_block_lock;

wire sfp1_rx_block_lock;

wire sfp_mgt_refclk_0;

IBUFDS_GTE4 ibufds_gte4_sfp_mgt_refclk_0_inst (

.I (sfp_mgt_refclk_0_p),

.IB (sfp_mgt_refclk_0_n),

.CEB (1'b0),

.O (sfp_mgt_refclk_0),

.ODIV2 ()

);

eth_xcvr_phy_quad_wrapper #(

.COUNT(2)

)

sfp_phy_inst (

.xcvr_ctrl_clk(clk_125mhz_int),

.xcvr_ctrl_rst(rst_125mhz_int),

/*

* Common

*/

.xcvr_gtpowergood_out(),

/*

* PLL

*/

.xcvr_gtrefclk00_in(sfp_mgt_refclk_0),

/*

* Serial data

*/

.xcvr_txp({sfp1_tx_p, sfp0_tx_p}),

.xcvr_txn({sfp1_tx_n, sfp0_tx_n}),

.xcvr_rxp({sfp1_rx_p, sfp0_rx_p}),

.xcvr_rxn({sfp1_rx_n, sfp0_rx_n}),

/*

* PHY connections

*/

.phy_1_tx_clk(sfp0_tx_clk_int),

.phy_1_tx_rst(sfp0_tx_rst_int),

.phy_1_xgmii_txd(sfp0_txd_int),

.phy_1_xgmii_txc(sfp0_txc_int),

.phy_1_rx_clk(sfp0_rx_clk_int),

.phy_1_rx_rst(sfp0_rx_rst_int),

.phy_1_xgmii_rxd(sfp0_rxd_int),

.phy_1_xgmii_rxc(sfp0_rxc_int),

.phy_1_tx_bad_block(),

.phy_1_rx_error_count(),

.phy_1_rx_bad_block(),

.phy_1_rx_sequence_error(),

.phy_1_rx_block_lock(sfp0_rx_block_lock),

.phy_1_rx_status(),

.phy_1_cfg_tx_prbs31_enable(1'b0),

.phy_1_cfg_rx_prbs31_enable(1'b0),

.phy_2_tx_clk(sfp1_tx_clk_int),

.phy_2_tx_rst(sfp1_tx_rst_int),

.phy_2_xgmii_txd(sfp1_txd_int),

.phy_2_xgmii_txc(sfp1_txc_int),

.phy_2_rx_clk(sfp1_rx_clk_int),

.phy_2_rx_rst(sfp1_rx_rst_int),

.phy_2_xgmii_rxd(sfp1_rxd_int),

.phy_2_xgmii_rxc(sfp1_rxc_int),

.phy_2_tx_bad_block(),

.phy_2_rx_error_count(),

.phy_2_rx_bad_block(),

.phy_2_rx_sequence_error(),

.phy_2_rx_block_lock(sfp1_rx_block_lock),

.phy_2_rx_status(),

.phy_2_cfg_tx_prbs31_enable(1'b0),

.phy_2_cfg_rx_prbs31_enable(1'b0)

);

fpga_core

core_inst (

/*

* Clock: 156.25 MHz

* Synchronous reset

*/

.clk(clk_156mhz_int),

.rst(rst_156mhz_int),

/*

* GPIO

*/

.btnu(btnu_int),

.btnl(btnl_int),

.btnd(btnd_int),

.btnr(btnr_int),

.btnc(btnc_int),

.sw(sw_int),

.led(led),

/*

* UART: 115200 bps, 8N1

*/

.uart_rxd(uart_rxd_int),

.uart_txd(uart_txd),

.uart_rts(uart_rts_int),

.uart_cts(uart_cts),

/*

* Ethernet: SFP+

*/

.sfp0_tx_clk(sfp0_tx_clk_int),

.sfp0_tx_rst(sfp0_tx_rst_int),

.sfp0_txd(sfp0_txd_int),

.sfp0_txc(sfp0_txc_int),

.sfp0_rx_clk(sfp0_rx_clk_int),

.sfp0_rx_rst(sfp0_rx_rst_int),

.sfp0_rxd(sfp0_rxd_int),

.sfp0_rxc(sfp0_rxc_int),

.sfp1_tx_clk(sfp1_tx_clk_int),

.sfp1_tx_rst(sfp1_tx_rst_int),

.sfp1_txd(sfp1_txd_int),

.sfp1_txc(sfp1_txc_int),

.sfp1_rx_clk(sfp1_rx_clk_int),

.sfp1_rx_rst(sfp1_rx_rst_int),

.sfp1_rxd(sfp1_rxd_int),

.sfp1_rxc(sfp1_rxc_int)

);

endmodule

`resetall

点击查看代码

/*

Copyright (c) 2020-2021 Alex Forencich

Permission is hereby granted, free of charge, to any person obtaining a copy

of this software and associated documentation files (the "Software"), to deal

in the Software without restriction, including without limitation the rights

to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

copies of the Software, and to permit persons to whom the Software is

furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in

all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY

FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

THE SOFTWARE.

*/

// Language: Verilog 2001

`resetall

`timescale 1ns / 1ps

`default_nettype none

/*

* FPGA core logic

*/

module fpga_core

(

/*

* Clock: 156.25MHz

* Synchronous reset

*/

input wire clk,

input wire rst,

/*

* GPIO

*/

input wire btnu,

input wire btnl,

input wire btnd,

input wire btnr,

input wire btnc,

input wire [7:0] sw,

output wire [7:0] led,

/*

* UART: 115200 bps, 8N1

*/

input wire uart_rxd,

output wire uart_txd,

input wire uart_rts,

output wire uart_cts,

/*

* Ethernet: SFP+

*/

input wire sfp0_tx_clk,

input wire sfp0_tx_rst,

output wire [63:0] sfp0_txd,

output wire [7:0] sfp0_txc,

input wire sfp0_rx_clk,

input wire sfp0_rx_rst,

input wire [63:0] sfp0_rxd,

input wire [7:0] sfp0_rxc,

input wire sfp1_tx_clk,

input wire sfp1_tx_rst,

output wire [63:0] sfp1_txd,

output wire [7:0] sfp1_txc,

input wire sfp1_rx_clk,

input wire sfp1_rx_rst,

input wire [63:0] sfp1_rxd,

input wire [7:0] sfp1_rxc

);

// AXI between MAC and Ethernet modules

wire [63:0] rx_axis_tdata;

wire [7:0] rx_axis_tkeep;

wire rx_axis_tvalid;

wire rx_axis_tready;

wire rx_axis_tlast;

wire rx_axis_tuser;

wire [63:0] tx_axis_tdata;

wire [7:0] tx_axis_tkeep;

wire tx_axis_tvalid;

wire tx_axis_tready;

wire tx_axis_tlast;

wire tx_axis_tuser;

// Ethernet frame between Ethernet modules and UDP stack

wire rx_eth_hdr_ready;

wire rx_eth_hdr_valid;

wire [47:0] rx_eth_dest_mac;

wire [47:0] rx_eth_src_mac;

wire [15:0] rx_eth_type;

wire [63:0] rx_eth_payload_axis_tdata;

wire [7:0] rx_eth_payload_axis_tkeep;

wire rx_eth_payload_axis_tvalid;

wire rx_eth_payload_axis_tready;

wire rx_eth_payload_axis_tlast;

wire rx_eth_payload_axis_tuser;

wire tx_eth_hdr_ready;

wire tx_eth_hdr_valid;

wire [47:0] tx_eth_dest_mac;

wire [47:0] tx_eth_src_mac;

wire [15:0] tx_eth_type;

wire [63:0] tx_eth_payload_axis_tdata;

wire [7:0] tx_eth_payload_axis_tkeep;

wire tx_eth_payload_axis_tvalid;

wire tx_eth_payload_axis_tready;

wire tx_eth_payload_axis_tlast;

wire tx_eth_payload_axis_tuser;

// IP frame connections

wire rx_ip_hdr_valid;

wire rx_ip_hdr_ready;

wire [47:0] rx_ip_eth_dest_mac;

wire [47:0] rx_ip_eth_src_mac;

wire [15:0] rx_ip_eth_type;

wire [3:0] rx_ip_version;

wire [3:0] rx_ip_ihl;

wire [5:0] rx_ip_dscp;

wire [1:0] rx_ip_ecn;

wire [15:0] rx_ip_length;

wire [15:0] rx_ip_identification;

wire [2:0] rx_ip_flags;

wire [12:0] rx_ip_fragment_offset;

wire [7:0] rx_ip_ttl;

wire [7:0] rx_ip_protocol;

wire [15:0] rx_ip_header_checksum;

wire [31:0] rx_ip_source_ip;

wire [31:0] rx_ip_dest_ip;

wire [63:0] rx_ip_payload_axis_tdata;

wire [7:0] rx_ip_payload_axis_tkeep;

wire rx_ip_payload_axis_tvalid;

wire rx_ip_payload_axis_tready;

wire rx_ip_payload_axis_tlast;

wire rx_ip_payload_axis_tuser;

wire tx_ip_hdr_valid;

wire tx_ip_hdr_ready;

wire [5:0] tx_ip_dscp;

wire [1:0] tx_ip_ecn;

wire [15:0] tx_ip_length;

wire [7:0] tx_ip_ttl;

wire [7:0] tx_ip_protocol;

wire [31:0] tx_ip_source_ip;

wire [31:0] tx_ip_dest_ip;

wire [63:0] tx_ip_payload_axis_tdata;

wire [7:0] tx_ip_payload_axis_tkeep;

wire tx_ip_payload_axis_tvalid;

wire tx_ip_payload_axis_tready;

wire tx_ip_payload_axis_tlast;

wire tx_ip_payload_axis_tuser;

// UDP frame connections

wire rx_udp_hdr_valid;

wire rx_udp_hdr_ready;

wire [47:0] rx_udp_eth_dest_mac;

wire [47:0] rx_udp_eth_src_mac;

wire [15:0] rx_udp_eth_type;

wire [3:0] rx_udp_ip_version;

wire [3:0] rx_udp_ip_ihl;

wire [5:0] rx_udp_ip_dscp;

wire [1:0] rx_udp_ip_ecn;

wire [15:0] rx_udp_ip_length;

wire [15:0] rx_udp_ip_identification;

wire [2:0] rx_udp_ip_flags;

wire [12:0] rx_udp_ip_fragment_offset;

wire [7:0] rx_udp_ip_ttl;

wire [7:0] rx_udp_ip_protocol;

wire [15:0] rx_udp_ip_header_checksum;

wire [31:0] rx_udp_ip_source_ip;

wire [31:0] rx_udp_ip_dest_ip;

wire [15:0] rx_udp_source_port;

wire [15:0] rx_udp_dest_port;

wire [15:0] rx_udp_length;

wire [15:0] rx_udp_checksum;

wire [63:0] rx_udp_payload_axis_tdata;

wire [7:0] rx_udp_payload_axis_tkeep;

wire rx_udp_payload_axis_tvalid;

wire rx_udp_payload_axis_tready;

wire rx_udp_payload_axis_tlast;

wire rx_udp_payload_axis_tuser;

wire tx_udp_hdr_valid;

wire tx_udp_hdr_ready;

wire [5:0] tx_udp_ip_dscp;

wire [1:0] tx_udp_ip_ecn;

wire [7:0] tx_udp_ip_ttl;

wire [31:0] tx_udp_ip_source_ip;

wire [31:0] tx_udp_ip_dest_ip;

wire [15:0] tx_udp_source_port;

wire [15:0] tx_udp_dest_port;

wire [15:0] tx_udp_length;

wire [15:0] tx_udp_checksum;

wire [63:0] tx_udp_payload_axis_tdata;

wire [7:0] tx_udp_payload_axis_tkeep;

wire tx_udp_payload_axis_tvalid;

wire tx_udp_payload_axis_tready;

wire tx_udp_payload_axis_tlast;

wire tx_udp_payload_axis_tuser;

wire [63:0] rx_fifo_udp_payload_axis_tdata;

wire [7:0] rx_fifo_udp_payload_axis_tkeep;

wire rx_fifo_udp_payload_axis_tvalid;

wire rx_fifo_udp_payload_axis_tready;

wire rx_fifo_udp_payload_axis_tlast;

wire rx_fifo_udp_payload_axis_tuser;

wire [63:0] tx_fifo_udp_payload_axis_tdata;

wire [7:0] tx_fifo_udp_payload_axis_tkeep;

wire tx_fifo_udp_payload_axis_tvalid;

wire tx_fifo_udp_payload_axis_tready;

wire tx_fifo_udp_payload_axis_tlast;

wire tx_fifo_udp_payload_axis_tuser;

// Configuration

wire [47:0] local_mac = 48'h02_00_00_00_00_00;

wire [31:0] local_ip = {8'd192, 8'd168, 8'd1, 8'd128};

wire [31:0] gateway_ip = {8'd192, 8'd168, 8'd1, 8'd1};

wire [31:0] subnet_mask = {8'd255, 8'd255, 8'd255, 8'd0};

// IP ports not used

assign rx_ip_hdr_ready = 1;

assign rx_ip_payload_axis_tready = 1;

assign tx_ip_hdr_valid = 0;

assign tx_ip_dscp = 0;

assign tx_ip_ecn = 0;

assign tx_ip_length = 0;

assign tx_ip_ttl = 0;

assign tx_ip_protocol = 0;

assign tx_ip_source_ip = 0;

assign tx_ip_dest_ip = 0;

assign tx_ip_payload_axis_tdata = 0;

assign tx_ip_payload_axis_tkeep = 0;

assign tx_ip_payload_axis_tvalid = 0;

assign tx_ip_payload_axis_tlast = 0;

assign tx_ip_payload_axis_tuser = 0;

// Loop back UDP

wire match_cond = rx_udp_dest_port == 1234;

wire no_match = ~match_cond;

reg match_cond_reg = 0;

reg no_match_reg = 0;

always @(posedge clk) begin

if (rst) begin

match_cond_reg <= 0;

no_match_reg <= 0;

end else begin

if (rx_udp_payload_axis_tvalid) begin

if ((~match_cond_reg & ~no_match_reg) |

(rx_udp_payload_axis_tvalid & rx_udp_payload_axis_tready & rx_udp_payload_axis_tlast)) begin

match_cond_reg <= match_cond;

no_match_reg <= no_match;

end

end else begin

match_cond_reg <= 0;

no_match_reg <= 0;

end

end

end

assign tx_udp_hdr_valid = rx_udp_hdr_valid & match_cond;

assign rx_udp_hdr_ready = (tx_eth_hdr_ready & match_cond) | no_match;

assign tx_udp_ip_dscp = 0;

assign tx_udp_ip_ecn = 0;

assign tx_udp_ip_ttl = 64;

assign tx_udp_ip_source_ip = local_ip;

assign tx_udp_ip_dest_ip = rx_udp_ip_source_ip;

assign tx_udp_source_port = rx_udp_dest_port;

assign tx_udp_dest_port = rx_udp_source_port;

assign tx_udp_length = rx_udp_length;

assign tx_udp_checksum = 0;

assign tx_udp_payload_axis_tdata = tx_fifo_udp_payload_axis_tdata;

assign tx_udp_payload_axis_tkeep = tx_fifo_udp_payload_axis_tkeep;

assign tx_udp_payload_axis_tvalid = tx_fifo_udp_payload_axis_tvalid;

assign tx_fifo_udp_payload_axis_tready = tx_udp_payload_axis_tready;

assign tx_udp_payload_axis_tlast = tx_fifo_udp_payload_axis_tlast;

assign tx_udp_payload_axis_tuser = tx_fifo_udp_payload_axis_tuser;

assign rx_fifo_udp_payload_axis_tdata = rx_udp_payload_axis_tdata;

assign rx_fifo_udp_payload_axis_tkeep = rx_udp_payload_axis_tkeep;

assign rx_fifo_udp_payload_axis_tvalid = rx_udp_payload_axis_tvalid & match_cond_reg;

assign rx_udp_payload_axis_tready = (rx_fifo_udp_payload_axis_tready & match_cond_reg) | no_match_reg;

assign rx_fifo_udp_payload_axis_tlast = rx_udp_payload_axis_tlast;

assign rx_fifo_udp_payload_axis_tuser = rx_udp_payload_axis_tuser;

// Place first payload byte onto LEDs

reg valid_last = 0;

reg [7:0] led_reg = 0;

always @(posedge clk) begin

if (rst) begin

led_reg <= 0;

end else begin

valid_last <= tx_udp_payload_axis_tvalid;

if (tx_udp_payload_axis_tvalid & ~valid_last) begin

led_reg <= tx_udp_payload_axis_tdata;

end

end

end

assign led = led_reg;

assign sfp1_txd = 64'h0707070707070707;

assign sfp1_txc = 8'hff;

eth_mac_10g_fifo #(

.ENABLE_PADDING(1),

.ENABLE_DIC(1),

.MIN_FRAME_LENGTH(64),

.TX_FIFO_DEPTH(4096),

.TX_FRAME_FIFO(1),

.RX_FIFO_DEPTH(4096),

.RX_FRAME_FIFO(1)

)

eth_mac_10g_fifo_inst (

.rx_clk(sfp0_rx_clk),

.rx_rst(sfp0_rx_rst),

.tx_clk(sfp0_tx_clk),

.tx_rst(sfp0_tx_rst),

.logic_clk(clk),

.logic_rst(rst),

.tx_axis_tdata(tx_axis_tdata),

.tx_axis_tkeep(tx_axis_tkeep),

.tx_axis_tvalid(tx_axis_tvalid),

.tx_axis_tready(tx_axis_tready),

.tx_axis_tlast(tx_axis_tlast),

.tx_axis_tuser(tx_axis_tuser),

.rx_axis_tdata(rx_axis_tdata),

.rx_axis_tkeep(rx_axis_tkeep),

.rx_axis_tvalid(rx_axis_tvalid),

.rx_axis_tready(rx_axis_tready),

.rx_axis_tlast(rx_axis_tlast),

.rx_axis_tuser(rx_axis_tuser),

.xgmii_rxd(sfp0_rxd),

.xgmii_rxc(sfp0_rxc),

.xgmii_txd(sfp0_txd),

.xgmii_txc(sfp0_txc),

.tx_fifo_overflow(),

.tx_fifo_bad_frame(),

.tx_fifo_good_frame(),

.rx_error_bad_frame(),

.rx_error_bad_fcs(),

.rx_fifo_overflow(),

.rx_fifo_bad_frame(),

.rx_fifo_good_frame(),

.cfg_ifg(8'd12),

.cfg_tx_enable(1'b1),

.cfg_rx_enable(1'b1)

);

eth_axis_rx #(

.DATA_WIDTH(64)

)

eth_axis_rx_inst (

.clk(clk),

.rst(rst),

// AXI input

.s_axis_tdata(rx_axis_tdata),

.s_axis_tkeep(rx_axis_tkeep),

.s_axis_tvalid(rx_axis_tvalid),

.s_axis_tready(rx_axis_tready),

.s_axis_tlast(rx_axis_tlast),

.s_axis_tuser(rx_axis_tuser),

// Ethernet frame output

.m_eth_hdr_valid(rx_eth_hdr_valid),

.m_eth_hdr_ready(rx_eth_hdr_ready),

.m_eth_dest_mac(rx_eth_dest_mac),

.m_eth_src_mac(rx_eth_src_mac),

.m_eth_type(rx_eth_type),

.m_eth_payload_axis_tdata(rx_eth_payload_axis_tdata),

.m_eth_payload_axis_tkeep(rx_eth_payload_axis_tkeep),

.m_eth_payload_axis_tvalid(rx_eth_payload_axis_tvalid),

.m_eth_payload_axis_tready(rx_eth_payload_axis_tready),

.m_eth_payload_axis_tlast(rx_eth_payload_axis_tlast),

.m_eth_payload_axis_tuser(rx_eth_payload_axis_tuser),

// Status signals

.busy(),

.error_header_early_termination()

);

eth_axis_tx #(

.DATA_WIDTH(64)

)

eth_axis_tx_inst (

.clk(clk),

.rst(rst),

// Ethernet frame input

.s_eth_hdr_valid(tx_eth_hdr_valid),

.s_eth_hdr_ready(tx_eth_hdr_ready),

.s_eth_dest_mac(tx_eth_dest_mac),

.s_eth_src_mac(tx_eth_src_mac),

.s_eth_type(tx_eth_type),

.s_eth_payload_axis_tdata(tx_eth_payload_axis_tdata),

.s_eth_payload_axis_tkeep(tx_eth_payload_axis_tkeep),

.s_eth_payload_axis_tvalid(tx_eth_payload_axis_tvalid),

.s_eth_payload_axis_tready(tx_eth_payload_axis_tready),

.s_eth_payload_axis_tlast(tx_eth_payload_axis_tlast),

.s_eth_payload_axis_tuser(tx_eth_payload_axis_tuser),

// AXI output

.m_axis_tdata(tx_axis_tdata),

.m_axis_tkeep(tx_axis_tkeep),

.m_axis_tvalid(tx_axis_tvalid),

.m_axis_tready(tx_axis_tready),

.m_axis_tlast(tx_axis_tlast),

.m_axis_tuser(tx_axis_tuser),

// Status signals

.busy()

);

udp_complete_64

udp_complete_inst (

.clk(clk),

.rst(rst),

// Ethernet frame input

.s_eth_hdr_valid(rx_eth_hdr_valid),

.s_eth_hdr_ready(rx_eth_hdr_ready),

.s_eth_dest_mac(rx_eth_dest_mac),

.s_eth_src_mac(rx_eth_src_mac),

.s_eth_type(rx_eth_type),

.s_eth_payload_axis_tdata(rx_eth_payload_axis_tdata),

.s_eth_payload_axis_tkeep(rx_eth_payload_axis_tkeep),

.s_eth_payload_axis_tvalid(rx_eth_payload_axis_tvalid),

.s_eth_payload_axis_tready(rx_eth_payload_axis_tready),

.s_eth_payload_axis_tlast(rx_eth_payload_axis_tlast),

.s_eth_payload_axis_tuser(rx_eth_payload_axis_tuser),

// Ethernet frame output

.m_eth_hdr_valid(tx_eth_hdr_valid),

.m_eth_hdr_ready(tx_eth_hdr_ready),

.m_eth_dest_mac(tx_eth_dest_mac),

.m_eth_src_mac(tx_eth_src_mac),

.m_eth_type(tx_eth_type),

.m_eth_payload_axis_tdata(tx_eth_payload_axis_tdata),

.m_eth_payload_axis_tkeep(tx_eth_payload_axis_tkeep),

.m_eth_payload_axis_tvalid(tx_eth_payload_axis_tvalid),

.m_eth_payload_axis_tready(tx_eth_payload_axis_tready),

.m_eth_payload_axis_tlast(tx_eth_payload_axis_tlast),

.m_eth_payload_axis_tuser(tx_eth_payload_axis_tuser),

// IP frame input

.s_ip_hdr_valid(tx_ip_hdr_valid),

.s_ip_hdr_ready(tx_ip_hdr_ready),

.s_ip_dscp(tx_ip_dscp),

.s_ip_ecn(tx_ip_ecn),

.s_ip_length(tx_ip_length),

.s_ip_ttl(tx_ip_ttl),

.s_ip_protocol(tx_ip_protocol),

.s_ip_source_ip(tx_ip_source_ip),

.s_ip_dest_ip(tx_ip_dest_ip),

.s_ip_payload_axis_tdata(tx_ip_payload_axis_tdata),

.s_ip_payload_axis_tkeep(tx_ip_payload_axis_tkeep),

.s_ip_payload_axis_tvalid(tx_ip_payload_axis_tvalid),

.s_ip_payload_axis_tready(tx_ip_payload_axis_tready),

.s_ip_payload_axis_tlast(tx_ip_payload_axis_tlast),

.s_ip_payload_axis_tuser(tx_ip_payload_axis_tuser),

// IP frame output

.m_ip_hdr_valid(rx_ip_hdr_valid),

.m_ip_hdr_ready(rx_ip_hdr_ready),

.m_ip_eth_dest_mac(rx_ip_eth_dest_mac),

.m_ip_eth_src_mac(rx_ip_eth_src_mac),

.m_ip_eth_type(rx_ip_eth_type),

.m_ip_version(rx_ip_version),

.m_ip_ihl(rx_ip_ihl),

.m_ip_dscp(rx_ip_dscp),

.m_ip_ecn(rx_ip_ecn),

.m_ip_length(rx_ip_length),

.m_ip_identification(rx_ip_identification),

.m_ip_flags(rx_ip_flags),

.m_ip_fragment_offset(rx_ip_fragment_offset),

.m_ip_ttl(rx_ip_ttl),

.m_ip_protocol(rx_ip_protocol),

.m_ip_header_checksum(rx_ip_header_checksum),

.m_ip_source_ip(rx_ip_source_ip),

.m_ip_dest_ip(rx_ip_dest_ip),

.m_ip_payload_axis_tdata(rx_ip_payload_axis_tdata),

.m_ip_payload_axis_tkeep(rx_ip_payload_axis_tkeep),

.m_ip_payload_axis_tvalid(rx_ip_payload_axis_tvalid),

.m_ip_payload_axis_tready(rx_ip_payload_axis_tready),

.m_ip_payload_axis_tlast(rx_ip_payload_axis_tlast),

.m_ip_payload_axis_tuser(rx_ip_payload_axis_tuser),

// UDP frame input

.s_udp_hdr_valid(tx_udp_hdr_valid),

.s_udp_hdr_ready(tx_udp_hdr_ready),

.s_udp_ip_dscp(tx_udp_ip_dscp),

.s_udp_ip_ecn(tx_udp_ip_ecn),

.s_udp_ip_ttl(tx_udp_ip_ttl),

.s_udp_ip_source_ip(tx_udp_ip_source_ip),

.s_udp_ip_dest_ip(tx_udp_ip_dest_ip),

.s_udp_source_port(tx_udp_source_port),

.s_udp_dest_port(tx_udp_dest_port),

.s_udp_length(tx_udp_length),

.s_udp_checksum(tx_udp_checksum),

.s_udp_payload_axis_tdata(tx_udp_payload_axis_tdata),

.s_udp_payload_axis_tkeep(tx_udp_payload_axis_tkeep),

.s_udp_payload_axis_tvalid(tx_udp_payload_axis_tvalid),

.s_udp_payload_axis_tready(tx_udp_payload_axis_tready),

.s_udp_payload_axis_tlast(tx_udp_payload_axis_tlast),

.s_udp_payload_axis_tuser(tx_udp_payload_axis_tuser),

// UDP frame output

.m_udp_hdr_valid(rx_udp_hdr_valid),

.m_udp_hdr_ready(rx_udp_hdr_ready),

.m_udp_eth_dest_mac(rx_udp_eth_dest_mac),

.m_udp_eth_src_mac(rx_udp_eth_src_mac),

.m_udp_eth_type(rx_udp_eth_type),

.m_udp_ip_version(rx_udp_ip_version),

.m_udp_ip_ihl(rx_udp_ip_ihl),

.m_udp_ip_dscp(rx_udp_ip_dscp),

.m_udp_ip_ecn(rx_udp_ip_ecn),

.m_udp_ip_length(rx_udp_ip_length),

.m_udp_ip_identification(rx_udp_ip_identification),

.m_udp_ip_flags(rx_udp_ip_flags),

.m_udp_ip_fragment_offset(rx_udp_ip_fragment_offset),

.m_udp_ip_ttl(rx_udp_ip_ttl),

.m_udp_ip_protocol(rx_udp_ip_protocol),

.m_udp_ip_header_checksum(rx_udp_ip_header_checksum),

.m_udp_ip_source_ip(rx_udp_ip_source_ip),

.m_udp_ip_dest_ip(rx_udp_ip_dest_ip),

.m_udp_source_port(rx_udp_source_port),

.m_udp_dest_port(rx_udp_dest_port),

.m_udp_length(rx_udp_length),

.m_udp_checksum(rx_udp_checksum),

.m_udp_payload_axis_tdata(rx_udp_payload_axis_tdata),

.m_udp_payload_axis_tkeep(rx_udp_payload_axis_tkeep),

.m_udp_payload_axis_tvalid(rx_udp_payload_axis_tvalid),

.m_udp_payload_axis_tready(rx_udp_payload_axis_tready),

.m_udp_payload_axis_tlast(rx_udp_payload_axis_tlast),

.m_udp_payload_axis_tuser(rx_udp_payload_axis_tuser),

// Status signals

.ip_rx_busy(),

.ip_tx_busy(),

.udp_rx_busy(),

.udp_tx_busy(),

.ip_rx_error_header_early_termination(),

.ip_rx_error_payload_early_termination(),

.ip_rx_error_invalid_header(),

.ip_rx_error_invalid_checksum(),

.ip_tx_error_payload_early_termination(),

.ip_tx_error_arp_failed(),

.udp_rx_error_header_early_termination(),

.udp_rx_error_payload_early_termination(),

.udp_tx_error_payload_early_termination(),

// Configuration

.local_mac(local_mac),

.local_ip(local_ip),

.gateway_ip(gateway_ip),

.subnet_mask(subnet_mask),

.clear_arp_cache(1'b0)

);

axis_fifo #(

.DEPTH(8192),

.DATA_WIDTH(64),

.KEEP_ENABLE(1),

.KEEP_WIDTH(8),

.ID_ENABLE(0),

.DEST_ENABLE(0),

.USER_ENABLE(1),

.USER_WIDTH(1),

.FRAME_FIFO(0)

)

udp_payload_fifo (

.clk(clk),

.rst(rst),

// AXI input

.s_axis_tdata(rx_fifo_udp_payload_axis_tdata),

.s_axis_tkeep(rx_fifo_udp_payload_axis_tkeep),

.s_axis_tvalid(rx_fifo_udp_payload_axis_tvalid),

.s_axis_tready(rx_fifo_udp_payload_axis_tready),

.s_axis_tlast(rx_fifo_udp_payload_axis_tlast),

.s_axis_tid(0),

.s_axis_tdest(0),

.s_axis_tuser(rx_fifo_udp_payload_axis_tuser),

// AXI output

.m_axis_tdata(tx_fifo_udp_payload_axis_tdata),

.m_axis_tkeep(tx_fifo_udp_payload_axis_tkeep),

.m_axis_tvalid(tx_fifo_udp_payload_axis_tvalid),

.m_axis_tready(tx_fifo_udp_payload_axis_tready),

.m_axis_tlast(tx_fifo_udp_payload_axis_tlast),

.m_axis_tid(),

.m_axis_tdest(),

.m_axis_tuser(tx_fifo_udp_payload_axis_tuser),

// Status

.status_overflow(),

.status_bad_frame(),

.status_good_frame()

);

endmodule

`resetall

浙公网安备 33010602011771号

浙公网安备 33010602011771号