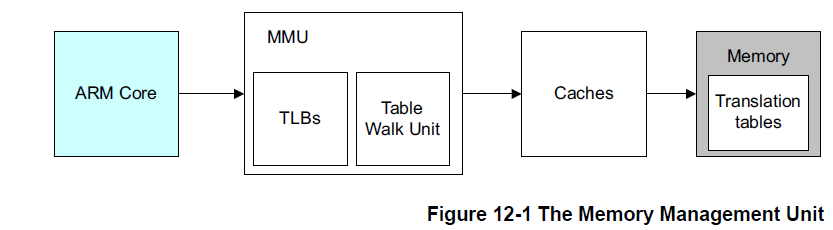

MMU 最重要的功能是系统可以同时运行多个task,因为独立运行在各自独立的virtual memory 空间。

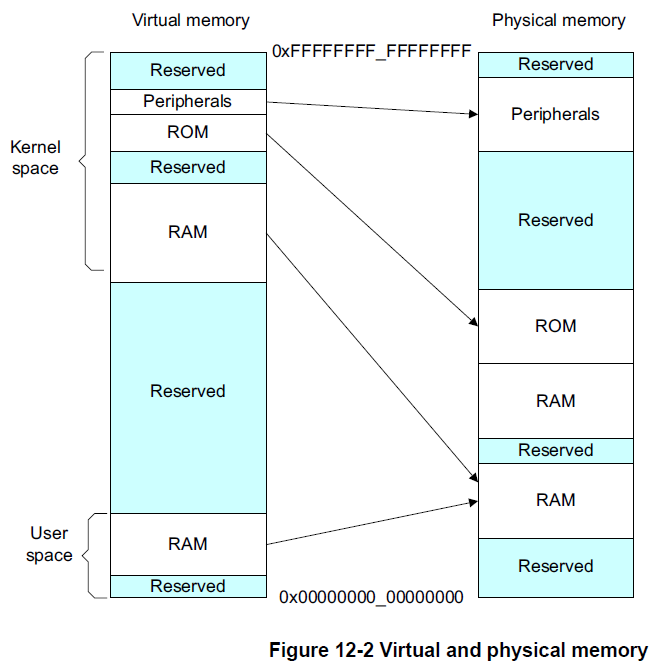

virtual 地址空间跟系统memory独立,且有对应的映射关系。

下图为不同的处理器和device 有不同的虚拟、物理地址映射:

MMU 使用virtual 地址指向translation table,管理哪些block可以访问。地址转换由硬件自动完成,MMU 同时管理memory 访问权限、memory 保序规则、每个memory region 的cache police。

TLB:

Transaction Lookaside Buffer是MMU转换地址的cache,每次访问,MMU 都会检查translation 是否命中TLB。每个TLB entry 不仅仅包含physical 地址和virtual 地址,还有attribute,比如memory type、cache police、access permission、address space ID(ASID)、virtual machine ID(VMID)。

TLB 可以hold 一个固定的entry 个数,提高命中率,在尽可能少的转换资源情况下达到最大性能。

TLB 还有一个configuous bit,set 后这个entry 可以用于多个block。此时需要对齐边界,VA[20:16]对应4KB边界,VA[28:21]对应64KB边界。支持的粒度有:16X4KB、32X32MB、32X64KB。

TLB 可以cache 一个entry 给固定的地址区间。

kernel 和application 的virtual 地址空间区分:

OS对每个application 划分了唯一的translation table。

Translation Table Base Register(TTBR0_EL1和TTBR1_EL1和)指定table base 地址,BBTR0/1由VA 高bit 决定。

Translation Control Register TCR_EL1定义了符号位数,包含T0SZ[5:0]和T1SZ[5:0]。

Intermediate Physical Size(IPS),控制输的地址的位宽,000:32bit,101:48bit。

two-bit Translation Granule(TG)TG0和TG1指定kernel、user 使用粒度大小,00:4KB;01:16KB;11:64KB;

整个转换过程需要3-4级表项查找,第一次查找需要TTBR0/1。

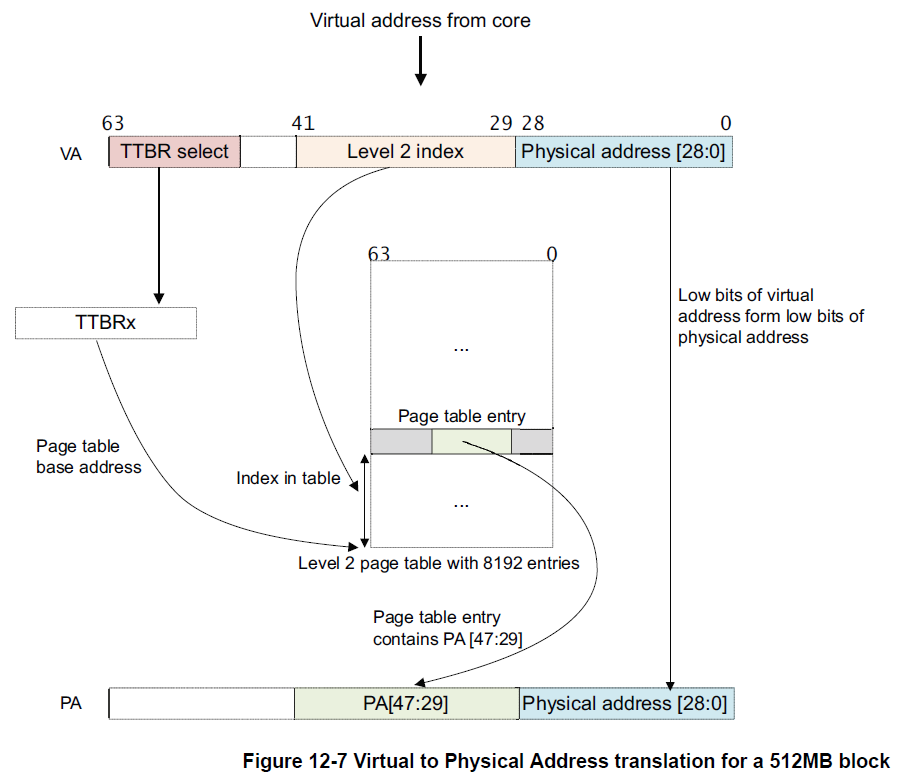

Virtual 地址到Physical 地址转换:

指令fetch的64bit VA,MMU转化为Physical 地址,高16bit [63:47]必须全部为0或者1.

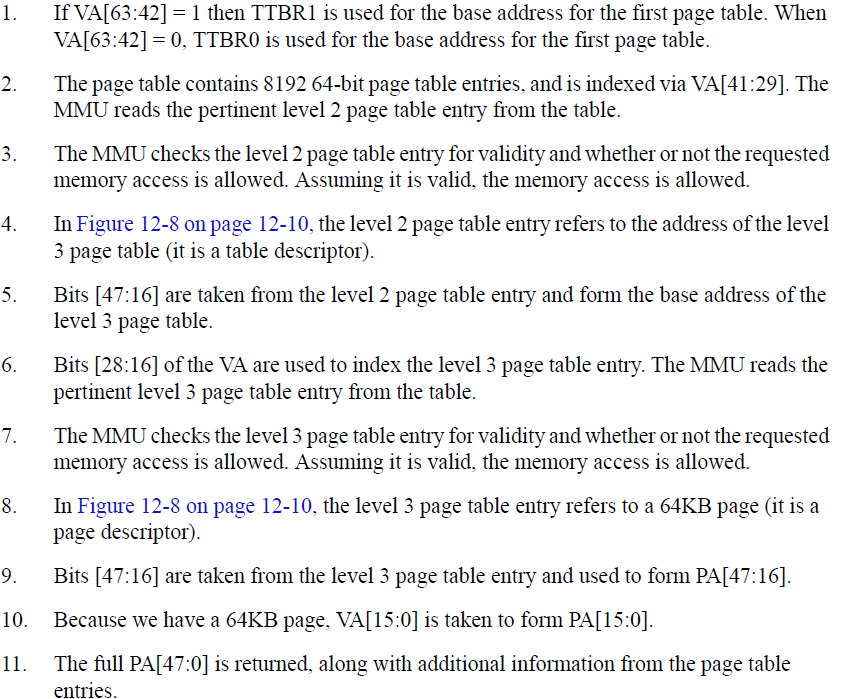

步骤如下:

1、VA[63:42]=1 则选择TTBR1,VA[63:42]=0则选择TTBR0.

2、page table 包含8192个64bit 的page table entry,index 为VA[41:29],MMU读取第二级table entry;

3、MMU检查page table entry 是否合理,检查memory权限是否允许,然后访问memory;

4、上图为512MBpage;

5、bit[47:29]也是physical 地址的[47:29]bit;

6、512MB 的page,VA[28:0]也为PA[28:0];

7、返回PA[47:0];

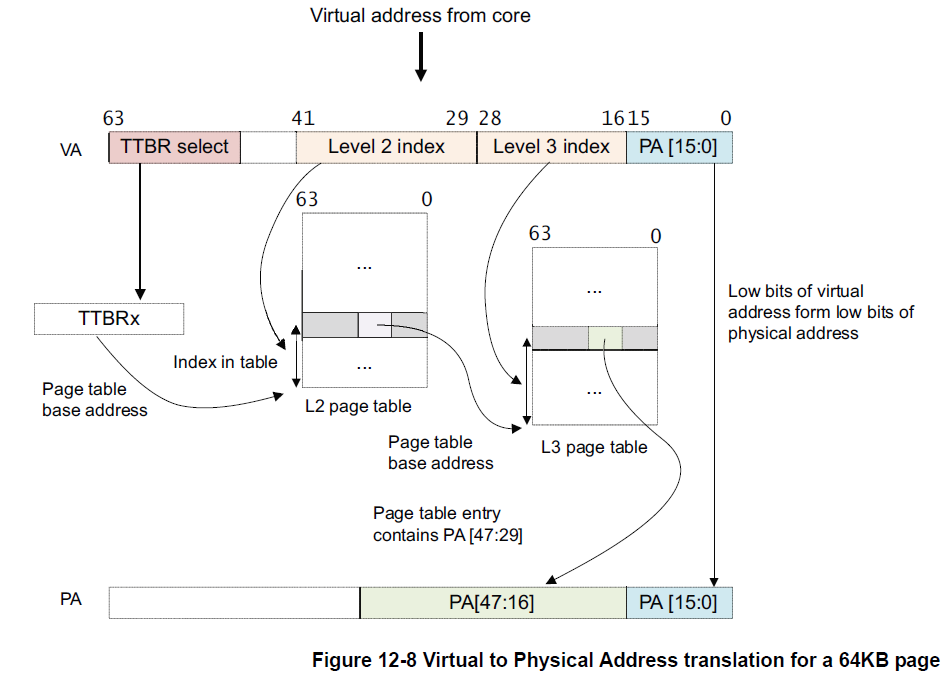

两级转换为:

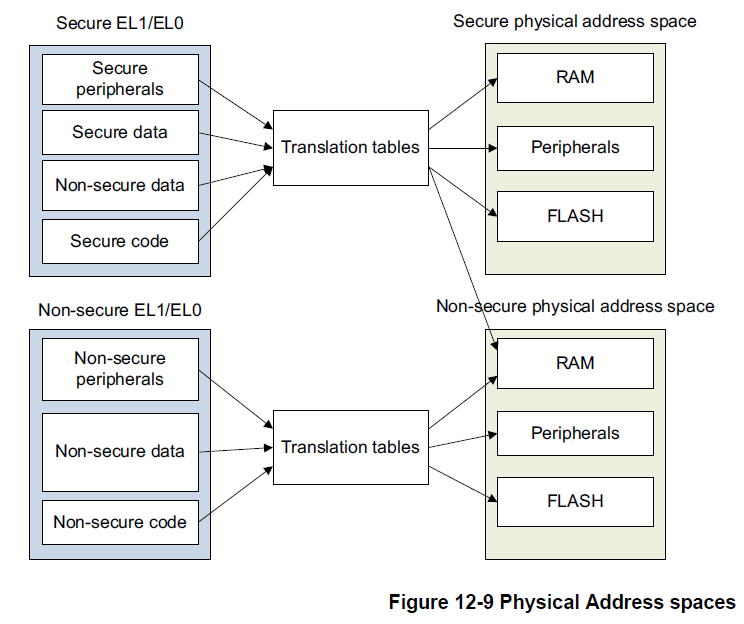

安全和非安全地址:

安全和非安全的PA空间是独立的,系统中设计Secure、Non-secure 通过控制访问实现,Normal 只能访问Non-secure PA空间,Secure 可以访问两者,这些都是通过translation table 实现。

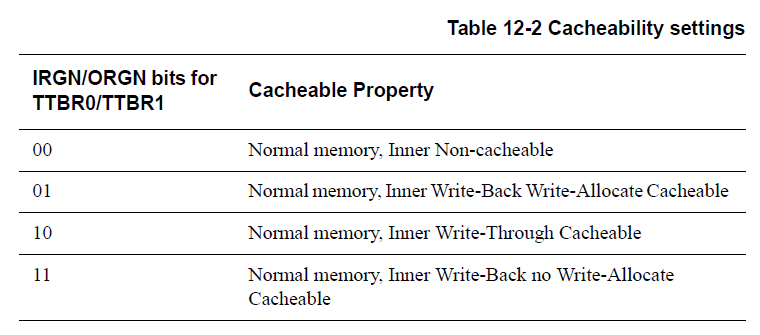

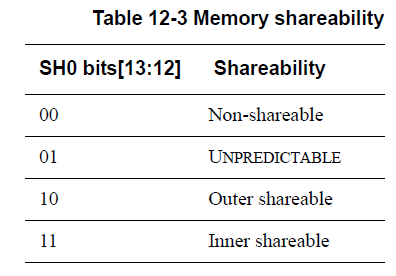

Translation Table 配置:

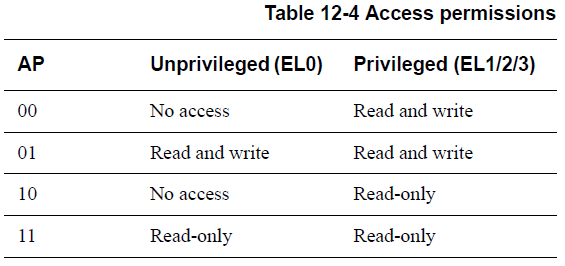

访问权限:

访问权限主要有读写,由EL0-3控制,如下所示:

第二种权限是executable,block 可以标executable或者non-executable(Execute Never (XN)),可以设置Unprivileged Execute Never(UXN)、Privileged Execute Never(PXN)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号