Synchronous Reset?Asynchronous Reset?

Abstract

复位是我们经常要使用到的,但是究竟是选择哪个好呢,两者之间有什么差别?这个以前都没怎么仔细看过,这两天看了一个大牛的论文,做个总结和分析。究竟两者间有什么区别。

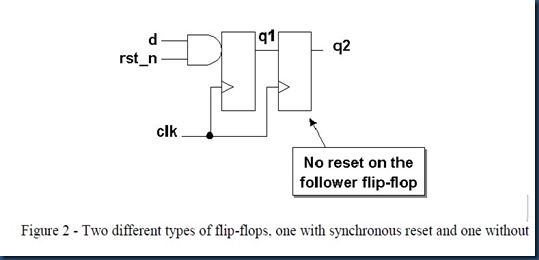

1、Synchronous reset flip-flops with non reset follower flip-flops

每一个verilog程序块或者VHDL process 应该只构建一种类型的flip-flop,就是一个designer不能将可复位FF与无复位FF混合使用。

module badFFstyle(q2,d,clk,rst_n);

output q2;

input d,clk,rst_n;

reg q2,q1;

always @(posedge clk)

if(!rst_n) q1<=1'b0;

else begin

q1<= d;

q2<= q1;

end

endmodule

在这个always block中q1后面跟着一个无reset的q2,复位信号rst_n变成q2的数据使能信号,产生额外的逻辑。

正确的方式构建follower flip-flop是用两个verilog程序块。

module goodFFstyle(q2,d,clk,rst_n);

output q2;

input d,clk,rst_n;

reg q2,q1;

always @(posedge clk)

if(!rst_n) q1<=1'b0;

else begin

q1<= d;

end

always @(posedge clk)

q2<= q1;

endmodule

EXAMPLE 2

必须注意的是上述的rst_n生成的外部逻辑只是在同步复位中生成,在异步复位中不会产生外部逻辑.

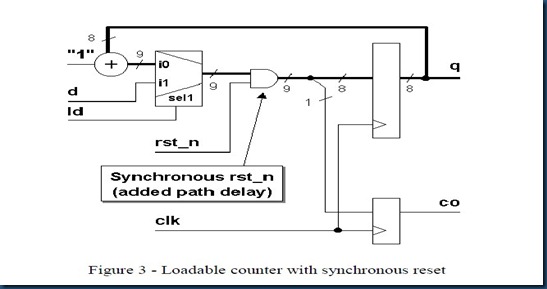

2、Synchronous Reset

Synchronous resets are based on the premise that the reset signal will only affect the state of the FF on the active edge of a clock.

复位信号应用在FF中组成一个组合逻辑作为FF的输入,这可以用IF-ELSE模块实现,如果这种模式没有严格遵守,会有两个问题:

1、一些仿真器中,基于逻辑等式,逻辑会将reset和FF分离成块。

2、复位信号可能会变成"late arriving signal”相对于时钟周期,由于reset tree的高fanout,即使有buffer tree,明智地减小它要穿过的logic的数量还是很重要的。

module ctr8sr(q,co,d,ld,rst_n,clk);

output [7:0]q;

output co;

input [7:0]d;

input ld,rst_n,clk;

reg [7:0]q;

reg co;

always @(posedge clk)

if (!rst_n) {co,q}<= 9'b0;

else if (ld) {co,q}<= d;

else {co,q}<= q+1'b1;

endmodule

EXAMPLE 3

2.1、Coding style and example circuit

例4显示了正确的方式去构建同步复位FF。

module sync_resetFFstyle(q,d,clk,rst_n);

output q;

input d,clk,rst_n;

reg q;

always @(posedge clk)

if (!rst_n) q<= 1'b0;

else q<=d;

endmodule

EXAMPLE 4

2.2、Advantage of synchronous resets

(1) 同步复位会综合成更小的FF,特别当reset生成逻辑电路作为FF的输入,这样组合逻辑电路的数量变多,所以总的门电路节省不是那么有意义。

(2) 同步复位更加容易工作当使用基于周期的仿真器。

(3) 同步复位确保电路100%是同步的。

(4) 同步复位确保复位只发生在时钟有效边沿,对小的复位毛刺来说,时钟就像滤波器。

(5) 在一些设计中,复位必须由内部条件产生,同步复位能滤除毛刺,所以被采用。

(6) 使用同步复位,FF能够在复位buffer tree中帮助buffer tree的时序保持在一个周期内。

2.3、Disadvantage of synchronous resets

(1) 同步复位需要一个脉冲延伸器保证复位脉冲足够宽能够被有效时钟沿采集到。

(2) 同步复位电路必须要有时钟。

3、Asynchronous resets

Synopsys要求假如敏感列表中的任何一个信号是边沿触发的,那么其余的信号也必须是边沿触发。Verilog仿真没有这种要求,但是如果敏感列表不仅仅对时钟边沿和复位边沿敏感,仿真模型将会不正确。并且只能有时钟和复位信号能够在敏感列表中。如果另外的信号在内,仿真模型对FF可能不正确,Synopsys将会报错。

module async_resetFFstyle(q,d,clk,rst_n); outoput q; inpout d,clk,rst_n; reg g; always @(posedge clk or negedge rst_n) if(!rst_n) q<=1'b0; else q<=d; endmodule

EXAMPLE 5

综合异步复位的方法因接近复位缓冲树的远近不同而不同,如果直接由外部引脚驱动,通常使用set_drive 0命令在复位的引脚,并且在复位网线中设置set_dont_touch_network将会保护网线不被综合器修改。有时需要set_resistance 0在复位网线上,或者创建一个线载模型在reset输入端口:set_wire_load pore_list reset.

随着Synopsys的升级,set_ideal_net命令能创建理想网线,没有时序升级,没有延迟优化,没有DRC混合。

3.1、Modeling verilog Flip-Flops with asynchronous reset and asynchronous set

假如FF的仿真模型中同时包括异步复位和异步set,可能仿真有错误除非designer有一些修改,Example 6能正确描述:

module dff3_aras(q,d,clk,rst_n,set_n);

output q;

input d,clk,rst_n,set_n;

reg q;

always @(posedge clk or negedge rst_n or negedge set_n)

if (!rst_n) q<= 1'b0;

else if (!set_n) q<=1'b1;

else q<= d;

//synopsys translate_off

always @(rst_n or set_n)

if (rst_n or !set_n) force q=1;

else release q;

//synopsys translate_on

endmodule

注意:这个问题只是一个仿真的问题而非综合问题,仿真的问题是由于always block都是边沿触发的,如果reset有效,接着set active,然后 reset inactive,FF应该先进入reset状态,然后进入set状态。因为都是异步的,所以set当reset is removed时本应该马上active。但是always block必须等到下一个clk时才能被驱动。

这样的问题可以用translate_off/translate_on命令来解决。

3.2、Advantage of asychronous resets

(1) 使用异步复位,reset不会被添加到data path中。没有额外的path delay。

(2) 能够被复位无论有没有clk present。

3.3、Disadvantage of asynchronous resets

(1) For DFT,如果异步复位不是直接由I/O引脚驱动,复位网线来自复位驱动器不能被DFT scanning and testing。

(2) STA变的困难,reset tree的同步复位和异步复位一定要约束确保reset的释放能在一个clk内发生。

(3) 最大的问题就是异步可能带来亚稳态。

(4) 可能有毛刺等,造成不稳定。

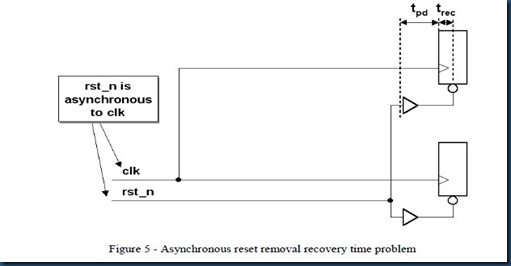

4、Asynchronous reset problem

我们必须考虑的是异步复位的亚稳态情况,就是释放reset时刚好碰上clk active,这样就会进入亚稳态。

Figure 5中所示,一个复位信号插入到时钟信号中,这种情形有两个潜在的问题:(1)违背复位恢复时间。 (2)复位移动发生在不同时钟周期在不同顺序元件中。

4.1、Reset recovery time

复位恢复时间指的是rst_n信号无效到clk上升沿之间的时间。有3个内建命令测试recovery time,removal time,$recovery,$removal和$recrem.

复位恢复时间指的是一个建立时间,“PRE或者CLR无效的建立时间”不满足恢复时间可能造成亚稳态。

4.2、Reset removal traversing different clock cycle

不同复位信号的延迟不同,registers or FF离开reset的状态不同。

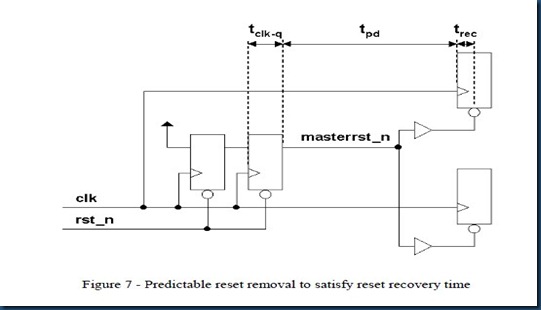

5、Reset synchronizer

Guideline:每一个ASIC使用一个异步复位必须包括一个复位同步的电路。

Figure 6利用了同步复位和异步复位各自的优点:

一个外部的reset信号将master FF异步复位,输出的masterrst_n再将剩下的FF异步复位,所以整个设计是异步复位。

reset removal在复位信号失效时完成,第一个FF的输入被一个clk锁存,总共经过两个clk,masterrst_n的值等于第一个FF输入的值。

两个FF用来同步复位信号和时钟脉冲,第二个FF被用来移除一些亚稳态(可能发生在复位信号异步移动和离clk边沿太近,就是第二个FF用来移除rst_n由0变为1时,由于不满足recovery time或者removal time所引发的亚稳态),同步FF一定要远离扫描链。

时序最后的检查显示复位时序分布是clk-q传输延迟的总和。Figure 7显示了总的延迟和满足recovery的时序。

module async_resetFFstyle2(rst_n,clk,asyncrst_n)

output rst_n;

input clk,asyncrst_n;

reg rst_n,rff1;

always @(posedge clk or negedge asyncrst_n)

if(!asyncrst_n) {rst_n,rff1}<= 2'b0;

else {rst_n,rff1}<={rff1,1'b1};

endmodule

EXAMPLE 7

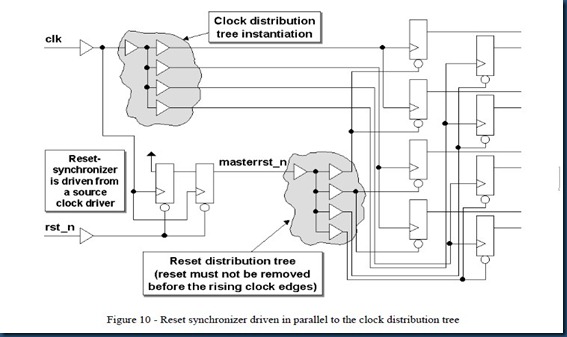

6、Reset distribution tree

复位分配树需要和时钟树一样的关注,复位树的时序要求对同步复位和异步复位是相同的。

时钟树和复位树的一个重要的区别是不同复位信号间的skew要平衡,skew不是非常严格,只要任何复位信号的延迟小于一个clk,并且能满足复位恢复时间。

为了加快reset信号到达系统的各个FF,复位驱动FF的时钟由提前的clk来驱动(Figure 10中所示),而非由时钟树的clk驱动。

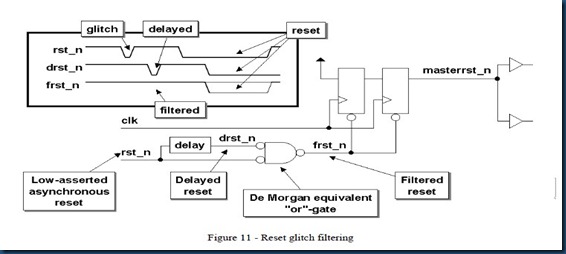

7、Reset-glitch filtering

当复位信号有毛刺时,我们可以通过delay滤除毛刺,这种方法要求有数字延迟

增加这个延迟有多种方法:(1)供销商提供的宏模块,能被手动设置。(2)可以自行设计一个module,但必须优化后才能实例化,并且设don’t touch.(3)通过增加buffer。

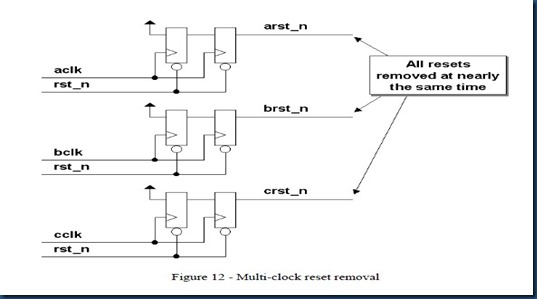

8、Multi_clock reset issues

对于多时钟,我们的异步复位,同步释放电路能够被每一个时钟域使用,并且确保了复位信号能够满足复位恢复时间.

所以说复位active没问题,问题在于复位释放时,由于频率不同,整个系统不同步.

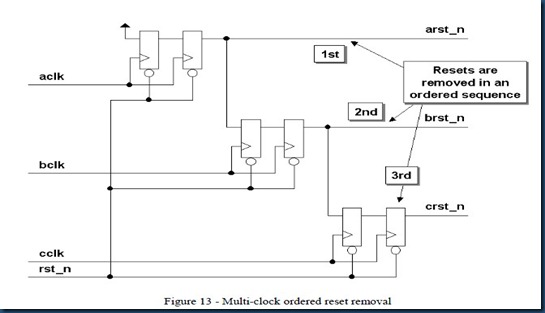

有两种技术可以应用:(1)不调整复位移动。 (2)顺序调整复位移动。

8.1、Non-coordinated reset removal

正如Figure 12,一般多用于具有握手信号的多时钟域中。

8.2、Coordinated reset removal

一般运用在有顺序要求的多时钟域中.

Reference:

Clifford E. Cummings,"Synchronous Resets, Asynchronous Resets,I am so confused,How will I ever know which to use”.

浙公网安备 33010602011771号

浙公网安备 33010602011771号