OV7725寄存器配置之PCLK、帧率

对OV7725中的帧率以及PCLK设置不解,故查看相关资料。找到了一些规律,不知是否准确,现总结如下:

在OV7725中有几个相关的比较重要的寄存器,0X0D、0X11、0X33.

0X0D主要是实现倍频的,通过高两位来控制四种倍频情况,00:不倍频,01:PLL 4*,

10:PLL 6*,11:PLL 8*。

0X11用来分频,Bit[5:0]:F(internal clock)=F(input clock)/(Bit[5:0]+1),

范围是0-31MHZ。

0X33这个地址中代表的内容是虚拟线低八位(Dummy line Low 8 Bits)。观察0X28,你会发现其中有这么一句话:Decrease frame rate by inserting dummy vertical sync equal to maximum exoposure lines.这就是说要减少帧率的话就得插入虚拟的垂直同步也就是增大lines。

下面从两段不同的代码中分析:

1、

30 fps, PCLK = 24Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x01);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x00);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

2、

25fps, PCLK = 24Mhz

SCCB_salve_Address = 0x42;

write_SCCB(0x11, 0x01);

write_SCCB(0x0d, 0x41);

write_SCCB(0x2a, 0x00);

write_SCCB(0x2b, 0x00);

write_SCCB(0x33, 0x66);

write_SCCB(0x34, 0x00);

write_SCCB(0x2d, 0x00);

write_SCCB(0x2e, 0x00);

write_SCCB(0x0e, 0x65);

这两端代码的输入clk都是24MHZ,输出PCLK相同都是24MHZ,但frame rate一个是30fps,一个为25fps,程序中只有0X33不同,如何通过将0X33设置为0X66,从而将30fps变为25fps。看下面的分析:

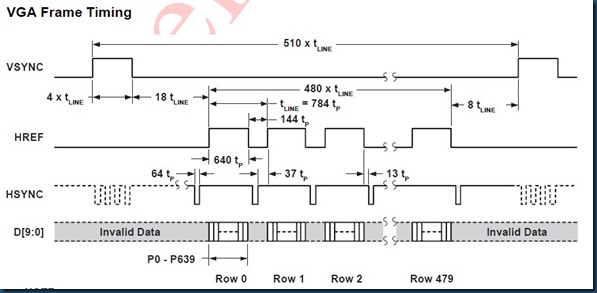

从图片中我们可以看到一个VSYNC有510个t(LINE),所以30fps表示有30*510*t(LINE),结合上面对于0X33的分析,因为都是24MHZ,所以30fps和25fps两个时间相同。故在这510个LINE中插入102个(0X66)LINE,总的时间才会相同。30*510*t(LINE)=25*(510+102)*t(LINE).

当然帧率会随着PCLK的变化而变化,当PCLK变为12MHZ时,帧率也就减为15fps了。

上面程序中对0X11设为0X01,根据这个公式F(internal clock)=F(input clock)/(Bit[5:0]+1),F(internal clock)=24/2=12MHZ,再将0X0D设为0X41,那应该是PLL 4*,这样

F(internal clock)=12*4=48MHZ了,而不是所谓的24MHZ啊?难道只是简单的成2倍的线性关系?暂且先这么理解。

求解释~~

浙公网安备 33010602011771号

浙公网安备 33010602011771号