Uart学习笔记

分享一个蛮好的链接:https://blog.csdn.net/wordwarwordwar/article/details/73662379

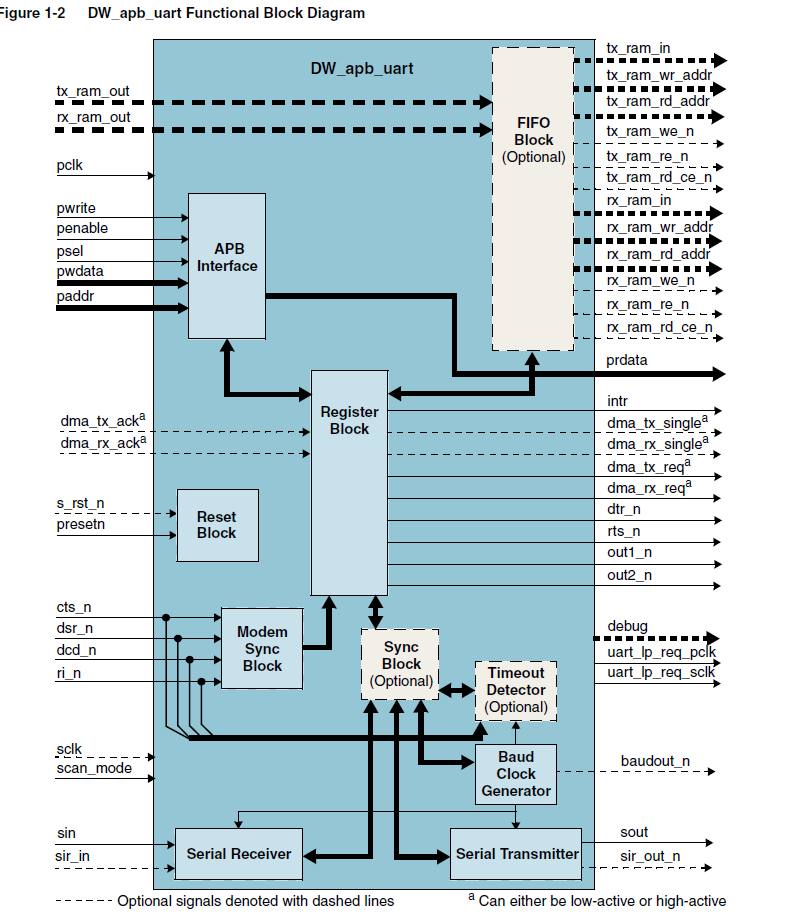

今天在看的资料是S家的DW_apb_uart的官方文档。该uart IP是挂在APB总线上面,CPU通过APB总线对uart进行访问和数据读写操作。

结构如下:

PS: sir_in/out是在SIR_MODE Enable时有效,用在irDA红外功能上。(红外功能将UART的NRZ串行比特率调制为脉冲形式)

主要流程是:

1.CPU通过APB总线config UART内部寄存器(register block),包括中断使能,charactor位宽,RX/TX FIFO 门限,同步时钟配置等等

2.数据读写操作(implement with FIFO)(CPU Master):

- 读:sin -> serial receiver -> sync -> FIFO -> register -> APB

- 写:APB -> register -> FIFO -> sync -> serial transmitter -> sout

其中FIFO作为buffer,FIFO余量要与APB一次burst WR/RD操作的大小相配合。

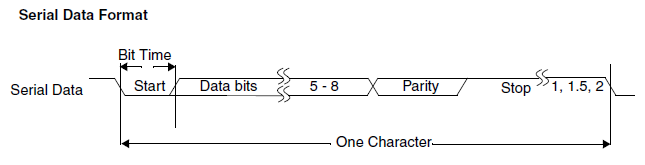

UART串行数据格式:

上图的sync时钟为baudclk,其中16 baudclk 对应 1bit data。

其中parity是奇偶校验位

波特率(baudout)由sclk和Divisor Latch Register决定。

UART可以有一个系统时钟(pclk)或者两个系统时钟(pclk,sclk)

时钟的计算方式看不懂= =略过

DMA:支撑两种DMA方式,通过dma_tx_req_n和dma_rx_req_n来做DMA读写请求

mode0:支撑单次DMA数据传输 mode1:支撑multi-DMA数据传输

cts_n和rts_n分别表示写ready和读ready。在auto-mode下由TX/RX fifo water level决定;在关闭audo-mode的时候由usr通过Cfg register的方式调节。(optional)

浙公网安备 33010602011771号

浙公网安备 33010602011771号