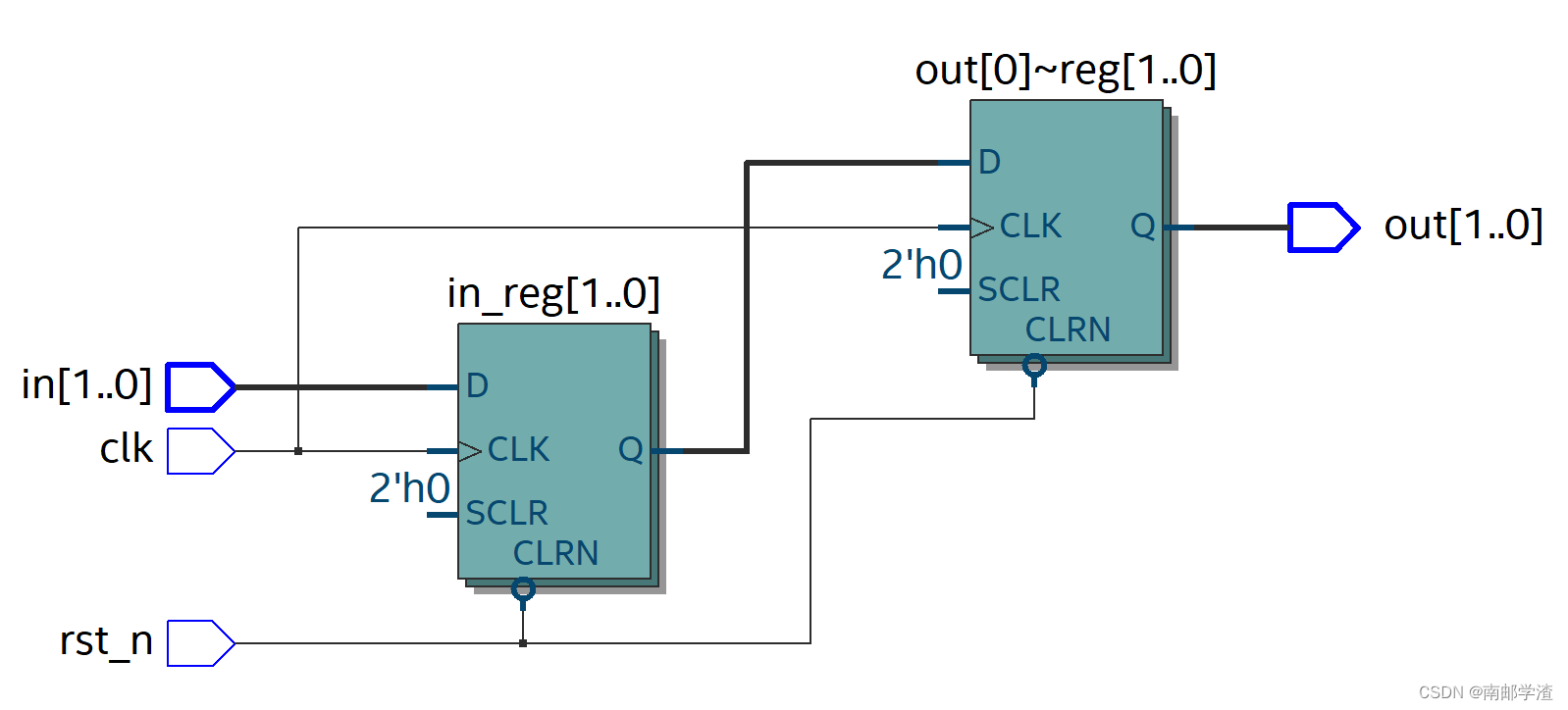

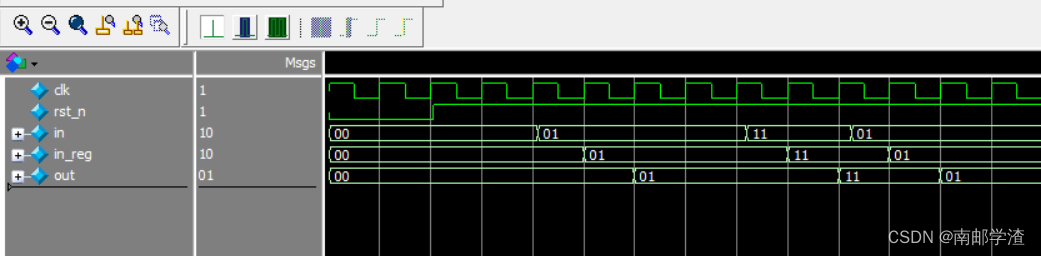

always非阻塞赋值延迟的周期数

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

in_reg=0; out=0;

end

else begin

in_reg<=in;

out<=in_reg;

end

分析:中间变量in_reg在in改变之后的下一个时钟上升沿才发生改变,因此in_reg与in之间会延迟一拍。对于out与in_reg之间,只要赋值号右边的表达式的值有变化,赋值号左边的表达式的值也不会立刻变化,需要等待下一次时钟沿到来时一起变化,所以我们最终看到的结果是输出信号 out 相对于输入信号是打了两拍的关系。

https://blog.csdn.net/qq_52450571/article/details/125553174?spm=1001.2101.3001.6650.1&utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7ERate-1-125553174-blog-106838806.pc_relevant_3mothn_strategy_recovery&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7ERate-1-125553174-blog-106838806.pc_relevant_3mothn_strategy_recovery&utm_relevant_index=2

浙公网安备 33010602011771号

浙公网安备 33010602011771号