Quartus18.0静态时序分析步骤

前言:静态时序分析和时序约束一般是同步并行的关系,故本文基于前文的时序约束仿真文件及网表的生成步骤,对一些缺漏点进行补充说明。

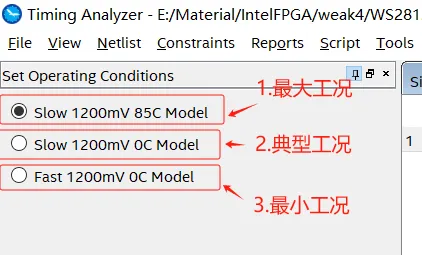

一、工况的选择和设置

进入Timing Analyzer工具后,可在左上角选择设置三种不同的工况,具体如下:

1.最大工况:Slow 1200mV 85C Model:芯片内核供电电压1200mV,工作温度85度情况下的慢速传输模型。

2.典型工况:Slow 1200mV 0C Model:芯片内核供电电压1200mV,工作0度情况下的慢速传输模型。

3.最小工况:Fast 1200mV 0C Modell:芯片内核供电电压1200mV,工作温度0度下快速传输模型。

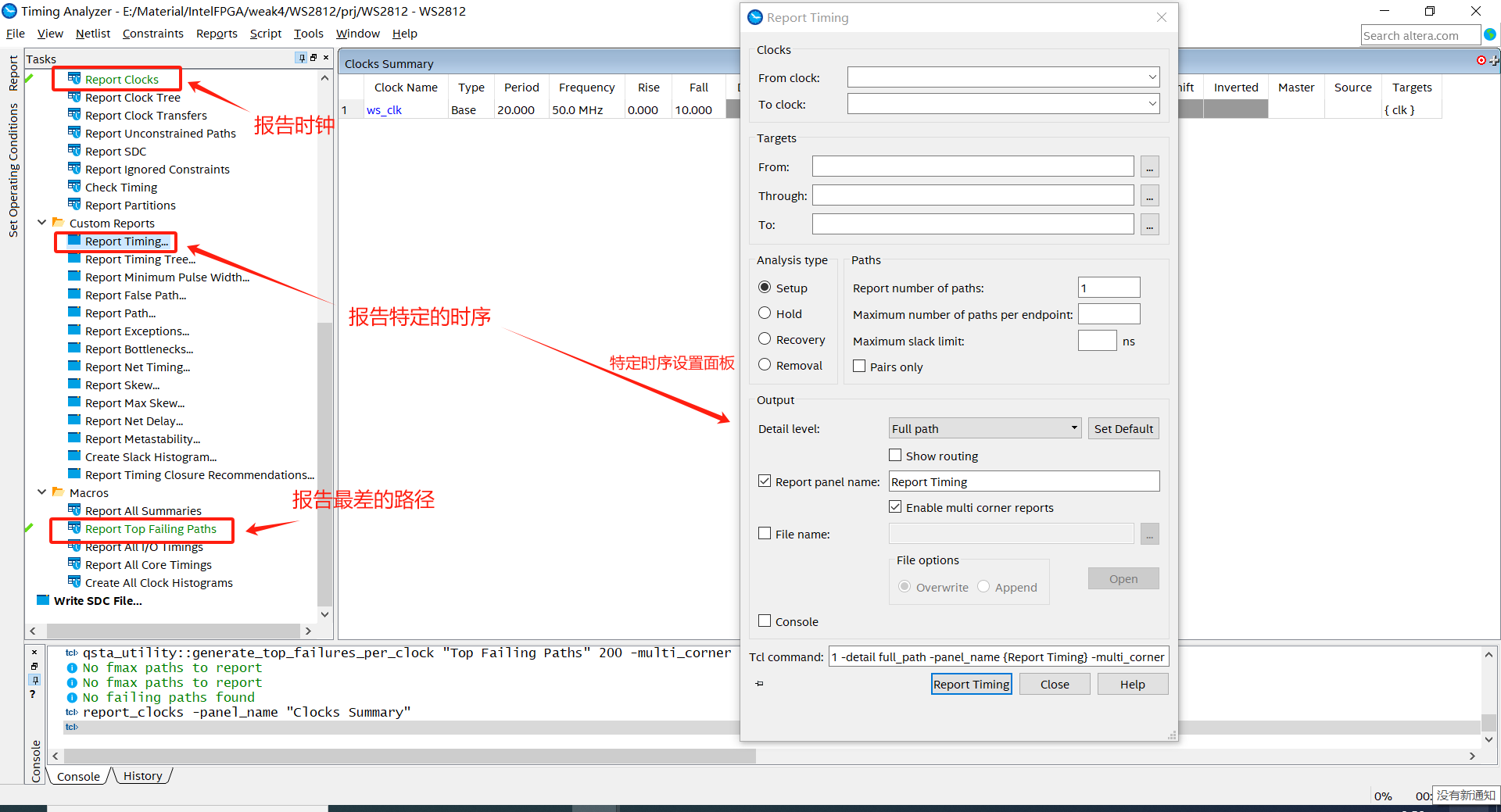

二、时序报告的查看

所以该项目中产生的时序报告都可以从“Tasks -> Reports”中查看,下面列举几个需要经常查看的时序报告:

这是几个常见的时序报告的操作步骤,至于其他的可以尝试自己点击进行测试。

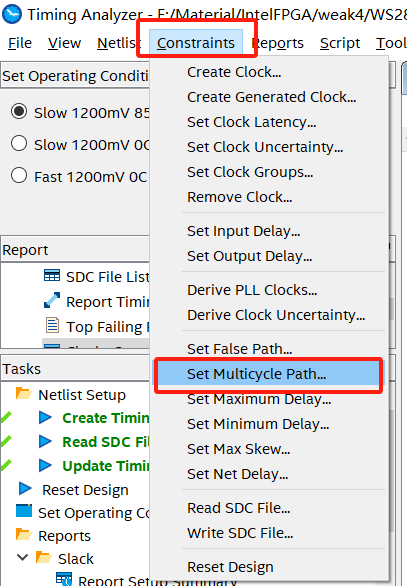

之后,就是按照昨天时序约束的步骤创建sdc约束文件,对时序分析过程中不满足的点通过“Constraints”进行相应的约束,其中各个不同约束的含义,在昨天的报告中均有提及。

三、sdc文件时序约束补充——时序例外的设置

设置时序例外主要有两种操作,一个是多周期路径,另一个是false路径。这两个其实在EDA工具进行布局布线得时候没什么作用,前者是让数据发射沿与数据接收沿之间的时间增大给建立时间带来好处,后者是告诉EDA工具不分析这一块。但是时序例外之前,一定要进行相应的处理,多周期路径的设置一定要是真的多周期路径,false掉的路径一定要对齐做跨时钟域处理、或者像是复位信号这种频率特别低的信号。3.1 设置多周期路径

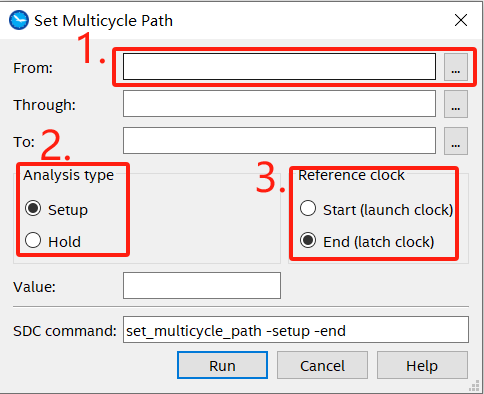

点击Set Multicycle Path弹出下面窗口:

1、选择需要设置多周期的路径

2、设置需要进行多周期的是建立时间还是保持时间

3、多周期路径到底是针对发射沿还是采样沿来说的,一般是采样沿

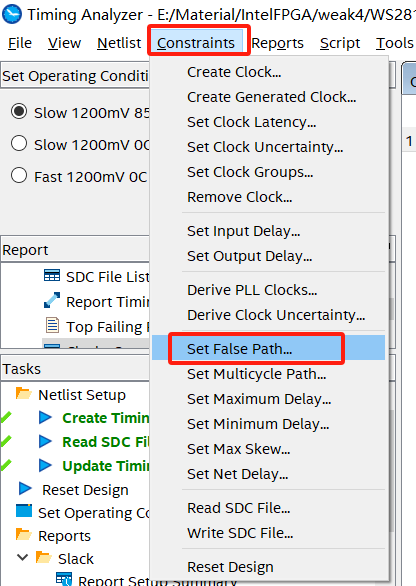

3.2 设置false路径

false路径在约束菜单栏中的如下位置:

点击Set False Path如下:

选择需要设置false的路径即可。

3.3 操作小结

所有的时序约束都可以跟着Report Timing来走,尤其是时序例外操作,在时序不满足要求的地方进行右击设置相应的多周期与false路径,这样就避免了自己寻找相应的节点,减少了自己的工作量。解决时序违例另一种常见的方法就是插入寄存器,改成流水线操作,但是插寄存器的时候不能随便乱插,见组合逻辑就插寄存器。我们要根据Report Timing来插寄存器。

3.4 时序约束注意点

1、如果用户没有对时钟信号加约束,软件就会自动对分析出的时钟加入约束,之后时钟会按照最大的来约束,也就是设置时钟频率为1GHz。按照最坏的情况来进行约束。2、有时候在时序分析的过程中会发现Tsu为负值的情况,这是正常的,因为Tsu是内部一系列时序的叠加,是有出现负值的可能性

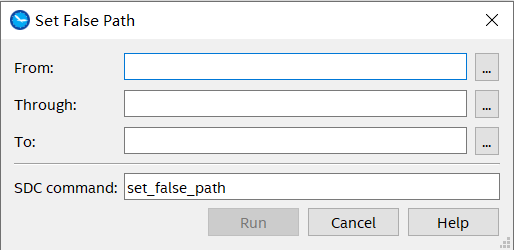

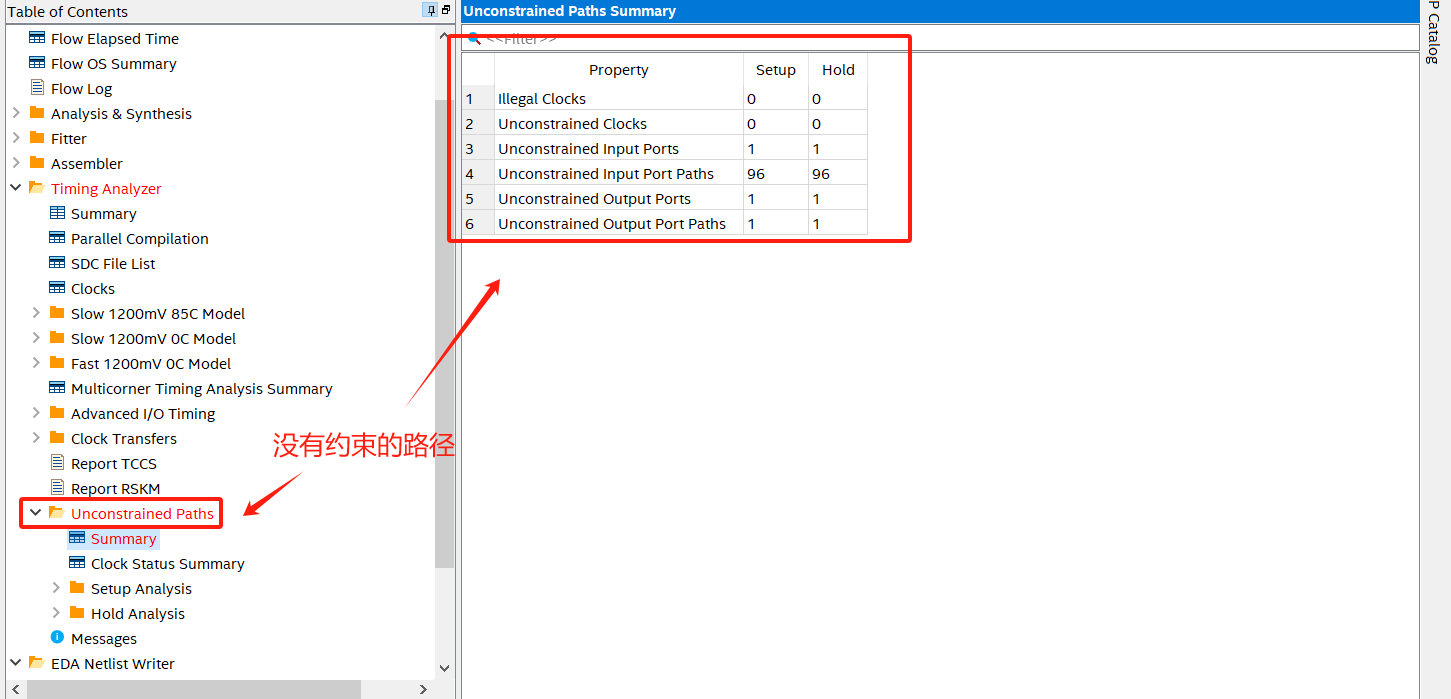

四、sdc文件时序约束补充——未约束路径的设置

1)在进行初步sdc时钟约束后,可能还会出现一些路径未约束的情况

2)此处会指明未约束路径报错的具体原因,可以根据该原因在进行进一步时序约束,进行排错。

浙公网安备 33010602011771号

浙公网安备 33010602011771号