always

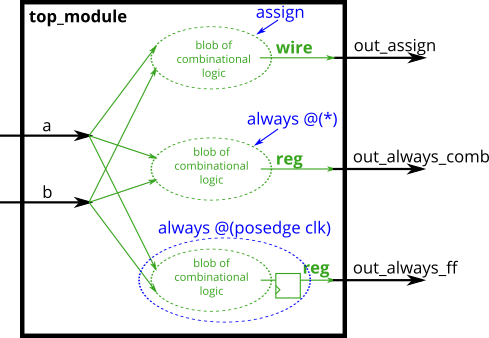

There are three types of assignments in Verilog:

- Continuous assignments (assign x = y;). Can only be used when not inside a procedure ("always block").

- Procedural blocking assignment: (x = y;). Can only be used inside a procedure.

- Procedural non-blocking assignment: (x <= y;). Can only be used inside a procedure.

![]()

// synthesis verilog_input_version verilog_2001 module top_module( input clk, input a, input b, output wire out_assign, output reg out_always_comb, output reg out_always_ff ); assign out_assign=a^b; always @(*)out_always_comb=a^b; always @(posedge clk)out_always_ff=a^b; endmodule

always if

always @(*) begin

if (condition) begin

……

This is equivalent to using a continuous assignment with a conditional operator:

assign out = (condition) ? x : y;

// synthesis verilog_input_version verilog_2001 module top_module( input a, input b, input sel_b1, input sel_b2, output wire out_assign, output reg out_always ); assign out_assign= (sel_b1&sel_b2)?b:a; always @(*)begin if(sel_b1&sel_b2)begin out_always=b; end else begin out_always=a; end end endmodule

always case

always casez

// synthesis verilog_input_version verilog_2001 module top_module ( input [7:0] in, output reg [2:0] pos ); always @(*)begin casez(in) 8'bzzzzzzz1:pos=0; 8'bzzzzzz1z:pos=1; 8'bzzzzz1zz:pos=2; 8'bzzzz1zzz:pos=3; 8'bzzz1zzzz:pos=4; 8'bzz1zzzzz:pos=5; 8'bz1zzzzzz:pos=6; 8'b1zzzzzzz:pos=7; default:pos = 0; endcase end endmodule

Always nolatches

// synthesis verilog_input_version verilog_2001 module top_module ( input [15:0] scancode, output reg left, output reg down, output reg right, output reg up ); always @(*)begin up = 1'b0; down = 1'b0; left = 1'b0; right = 1'b0; case(scancode) 16'he06b:begin up = 1'b0; down = 1'b0; left = 1'b1; right = 1'b0; end 16'he072:begin up = 1'b0; down = 1'b1; left = 1'b0; right = 1'b0; end 16'he074:begin up = 1'b0; down = 1'b0; left = 1'b0; right = 1'b1; end 16'he075:begin up = 1'b1; down = 1'b0; left = 1'b0; right = 1'b0; end default:begin up = 1'b0; down = 1'b0; left = 1'b0; right = 1'b0; end endcase end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号