STM32F1系列 GPIO详解

# STM32F1系列 GPIO详解

1.概述

GPIO是通用输入输出端口(General-purpose input/output)的英文简写,是所有的微控制器必不可少的外设之一,可以由STM32直接驱动从而实现与外部设备通信、控制以及采集和捕获的功能。

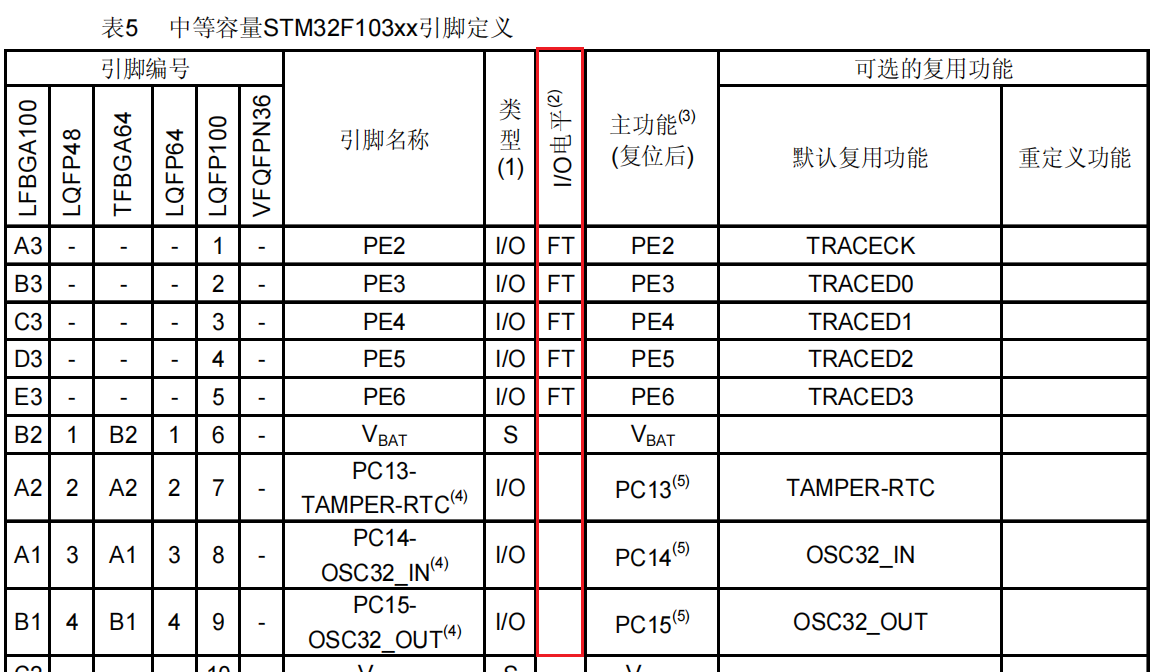

所有的GPIO都有基本的输入输出功能,不可能都只实现基础输入输出,使用片内UART、I2C等模块通信时,需要配置复用功能,称为端口复用,具体复用情况需要查找数据手册。

主要体现在提高硬件设计灵活性、优化引脚资源利用、方便电路升级与维护等方面,STM32配有端口重映射功能,在复杂的应用中,可能会出现多个外设需要使用相同引脚的情况,导致引脚冲突。端口重映射功能可以将冲突的外设引脚重新分配到其他可用的引脚上,从而避免引脚冲突,确保各个外设能够正常工作。

2.GPIO的工作原理

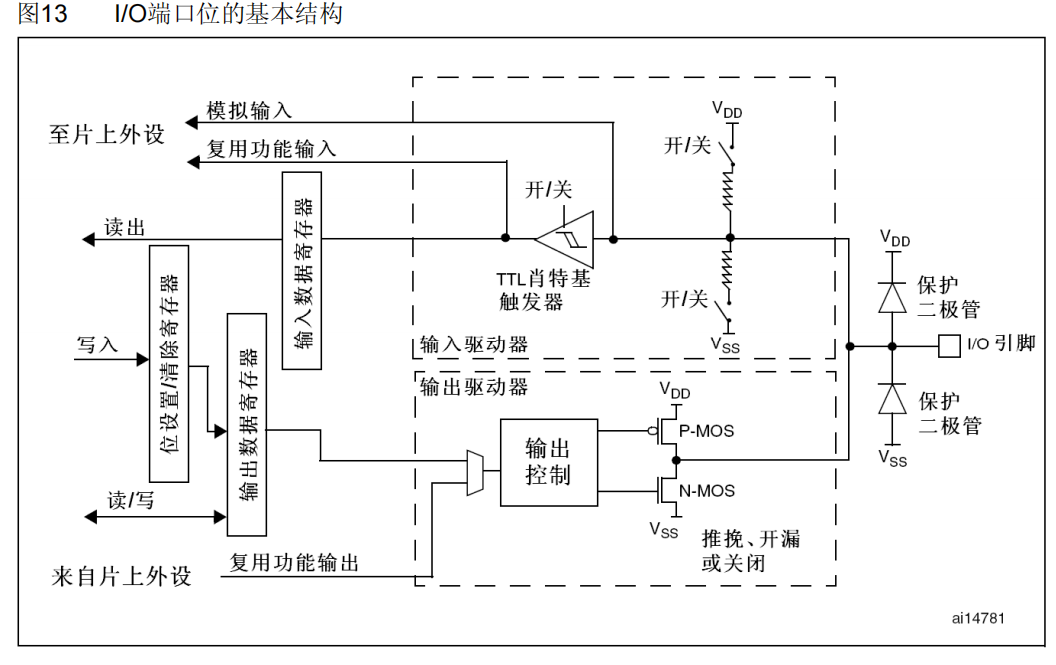

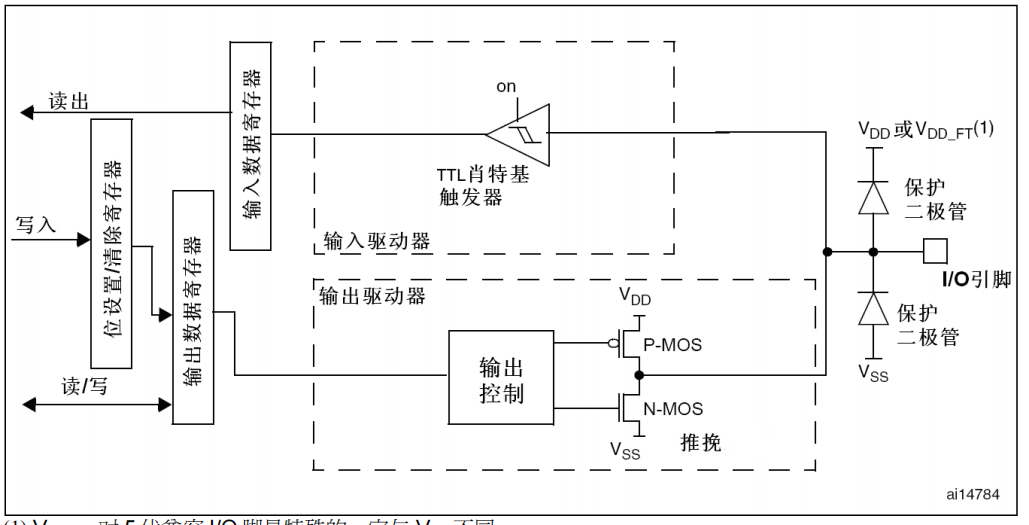

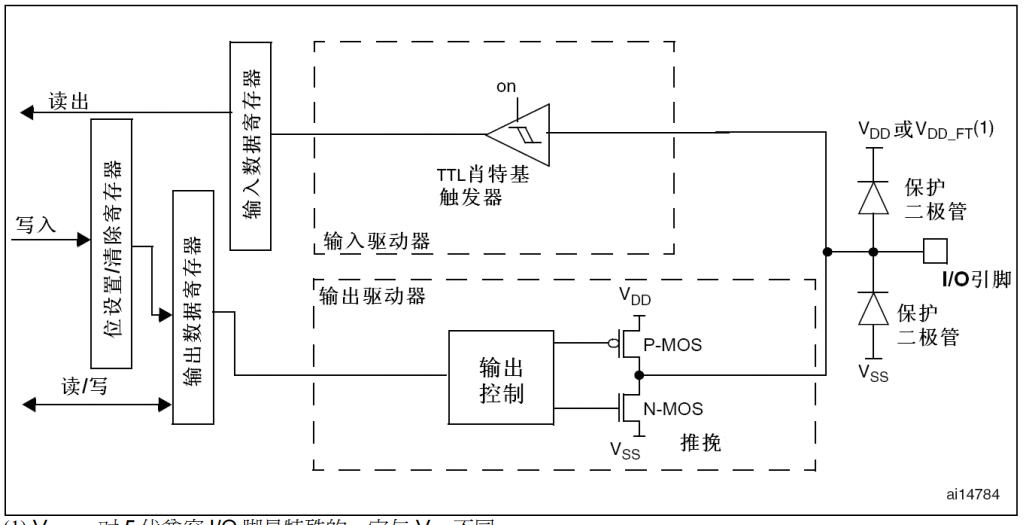

下图给出了一个I/O端口位的基本结构。

根据数据手册中列出的每个I/O端口的特定硬件特征, GPIO端口的每个位可以由软件分别配置成多种模式。

2.1保护二极管

保护二极管顾名思义对芯片起到保护作用,当I/O口输入电压大于VDD时将电压钳位在VDD,低于VSS时钳位在VSS。

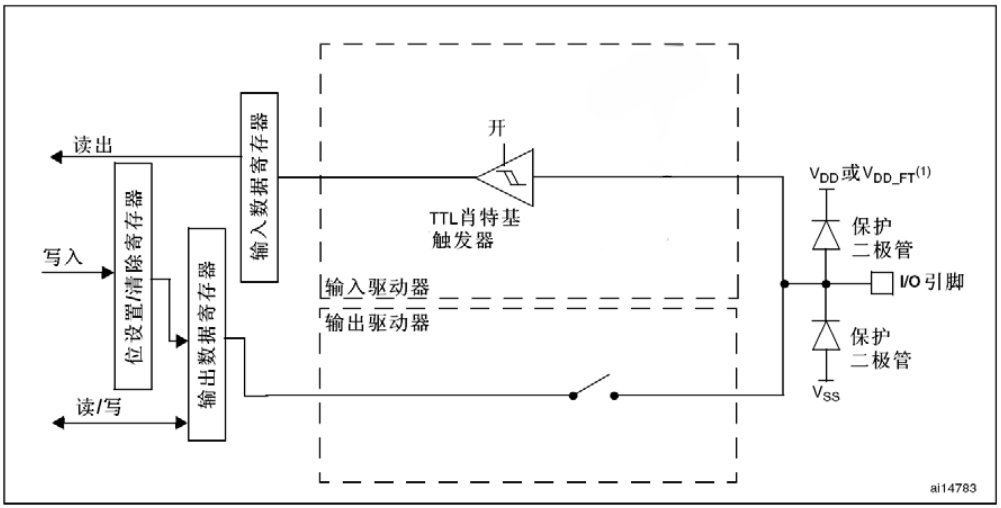

- VDD:通常电压范围在 1.8V 至 3.6V,具体取决于芯片的型号和应用需求,常见值为 3.3V。

- VDD_FT:一般来说,VDD_FT 在数值上可能与 VDD 的常见值有所不同,典型情况是 VDD_FT 可能会被设计为能够支持 5V 的输入输出电平,但实际工作电压可能根据电路设计和应用场景在一定范围内波动,具体要参考相应的数据手册。

![输入图片说明]()

2.3 TTL肖特基触发器

TTL 肖特基触发器是一种基于晶体管 - 晶体管逻辑(TTL)技术,并结合肖特基二极管改进的数字电路元件

- TTL(晶体管 - 晶体管逻辑):是一种广泛应用的数字集成电路技术,通过晶体管的导通和截止来实现逻辑功能,具有速度较快、抗干扰能力较强等特点。

- 肖特基二极管:一种具有快速开关特性的二极管,其正向导通压降较低,开关速度比普通二极管快。TTL 肖特基触发器将肖特基二极管集成到 TTL 电路中,以提高电路的性能。

-

- 基本触发器原理:触发器是一种具有记忆功能的双稳态电路,它有两个稳定状态(0 和 1),可以在外界信号的触发下从一个稳定状态转换到另一个稳定状态。常见的触发器有 RS 触发器、JK 触发器、D 触发器等。

- 肖特基二极管的作用:在 TTL 电路中,晶体管在饱和导通时会存储一定的电荷,这些电荷的存储和释放会影响电路的开关速度。肖特基二极管与晶体管的基极 - 集电极之间并联,当晶体管趋于饱和时,肖特基二极管会提前导通,将多余的电荷分流,从而减少晶体管的饱和深度,加快晶体管的开关速度。

在 STM32 芯片内部,每个 GPIO 引脚都连接有一个肖特基触发器。当外部信号输入到 GPIO 引脚时,首先会经过这个肖特基触发器进行处理(除了模拟输入),然后再将处理后的信号传输到芯片内部的其他模块(如寄存器等)进行进一步处理。

2.4 推挽输出硬件原理

在推挽输出电路中,PMOS 管的源极连接到电源正极 ,NMOS 管的源极连接到地 ,二者的漏极连接在一起作为输出端 ,栅极连接相同的输入信号 。

2.4.1 输出高电平

- 输入信号条件:当输入信号为低电平时。

- MOS 管状态:

- PMOS 管:对于PMOS管,其栅源电压小于其开启电压 (通常为负值,例如-1.5V),为-3.3V左右,处于导通状态,从而让源极和漏极之间能够导通电流。

- NMOS 管:对于NMOS管,其栅源电压小于其开启电压 (通常为正值,例如+1.5V),为0V左右,处于截止状态。NMOS管不导通。

- 电流路径与输出结果:电源的电流通过导通的 PMOS 管流向输出端 ,由于PMOS管导通电阻较小,输出端的电压接近电源电压 ,即输出高电平。

2.4.2 输出低电平

- 输入信号条件:当输入信号 为高电平时。

- MOS 管状态:

- PMOS 管:对于PMOS管,其栅源电压大于其开启电压 (通常为负值,例如-1.5V),为0V左右,处于截止状态。PMOS管不导通。

- NMOS 管:对于NMOS管,其栅源电压大于其开启电压 (通常为正值,例如+1.5V),为3V左右,处于导通状态,从而让源极和漏极之间能够导通电流。

- 电流路径与输出结果:输出端 的电流通过导通的 NMOS 管流向地 ,由于 NMOS 管导通电阻较小,输出端的电压接近地电压 ,即输出低电平。

2.4.3 状态转换

- 从高电平到低电平转换:当输入信号从低电平变为高电平时,PMOS管开始逐渐截止,NMOS管开始逐渐导通。在转换瞬间,由于MOS管的寄生电容等因素,可能会出现短暂的交越电流,即同时有电流从电源通过 PMOS管和从输出端通过NMOS管流向地。随着时间推移,PMOS管完全截止,NMOS管完全导通,输出端电压逐渐下降到低电平。

- 从低电平到高电平转换:当输入信号从高电平变为低电平时,NMOS 管开始逐渐截止,PMOS管开始逐渐导通。同样在转换瞬间可能会出现交越电流,之后NMOS管完全截止,PMOS管完全导通,输出端电压逐渐上升到高电平。

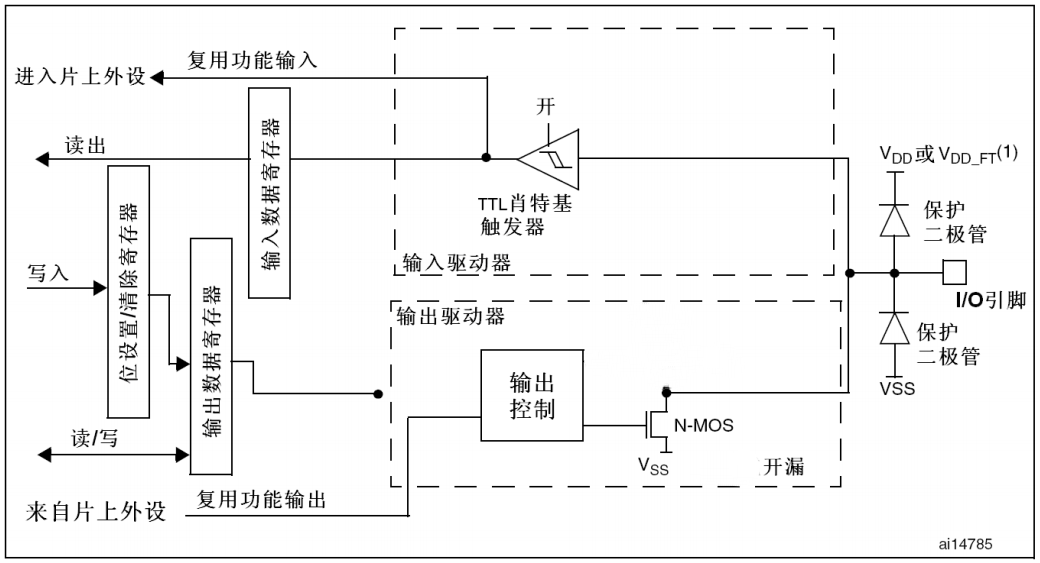

2.5 开漏输出硬件原理

- NMOS 管的源极(Source)连接到地(GND)。

- 漏极(Drain)作为输出端,该端不直接连接电源,处于开路状态。

- 需要在漏极和电源 之间外接一个上拉电阻 。

- 栅极(Gate)接收输入信号,用于控制 MOS 管的导通和截止。

- 输出低电平:当向控制该 GPIO 引脚的寄存器写入低电平控制信号时,NMOS 管的栅极获得相应信号,使NMOS管导通。此时,输出端通过导通的NMOS管连接到地,引脚输出低电平(接近 0V)。

- 输出高阻态:当向控制寄存器写入高电平控制信号时,NMOS管截止,相当于一个无穷大的电阻(高阻态)。由于外接了上拉电阻到电源,输出端的电平被上拉电阻拉高到电源电压,引脚输出高电平(接近 VDD),图例加了一个发光二极管,所以有0.7V的压降。

2.6工作模式

- 浮空输入(Floating Input)

- 上拉输入(Pull-up Input)

- 下拉输入(Pull-down Input)

- 模拟输入(Analog Input)

- 开漏输出(Open-Drain Output)

- 推挽输出(Push-Pull Output)

- 开漏复用输出(AF Open-Drain Output)

- 推挽复用输出(AF Push-Pull Output)

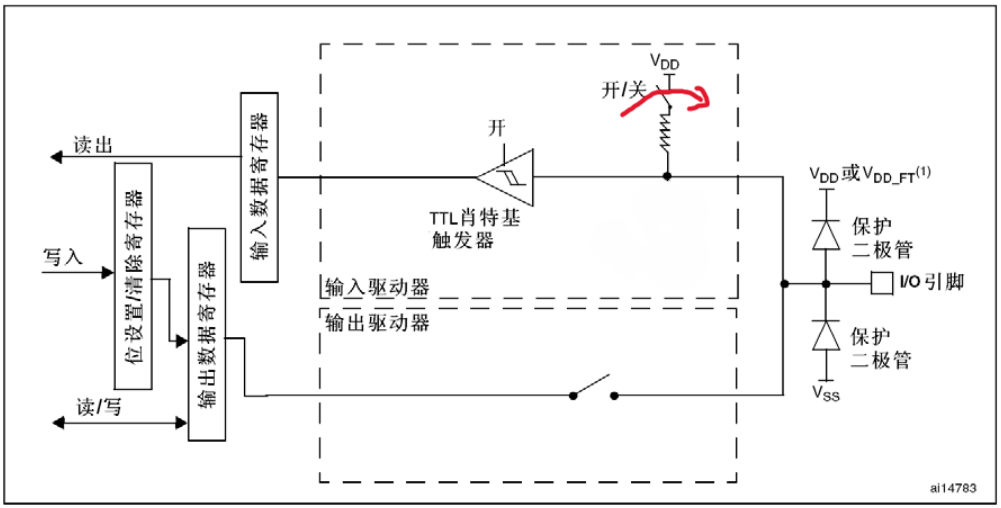

2.6.1 浮空输入

在浮空输入模式中,GPIO 引脚内部的上拉和下拉电阻开关均处于断开状态,使得引脚不与电源(上拉)或地(下拉)相连。外部信号可以直接作用在引脚上,引脚会读取外部信号的电平状态,并将其传输到内部的输入数据寄存器,微控制器通过读取该寄存器的值来获取引脚的电平。

应用场景:PWM,高低电平检测,数字信号。

- 优点

- 可以真实反映外部信号电平,对外部信号干扰较小,适用于信号源本身驱动能力较强且信号明确的情况。

- 硬件设计简单,无需额外的上拉或下拉电阻,降低成本和电路板空间占用。

- 缺点

- 引脚电平易受外界干扰,在没有外部信号输入时,引脚电平不稳定,可能会出现抖动现象,导致误判。

- 不适合用于信号源驱动能力弱或信号易受干扰的场景。

2.6.2 上拉输入

在 上拉输入模式下,引脚内部连接了一个上拉电阻到电源(VDD)。当外部电路没有连接或者输入为高阻态时,引脚会通过上拉电阻被拉高到高电平;当外部电路将引脚拉低时,引脚电平变为低电平。这样可以确保在没有外部信号输入时,引脚有一个确定的高电平状态,避免引脚电平的不确定性。

应用场景:检测低电平,PNP信号,开关量。

- 优点

- 确保在无外部信号输入时,引脚处于稳定的高电平状态,提高了系统的抗干扰能力。

- 适用于按键检测等场景,能有效避免按键抖动引起的误触发。

- 缺点

- 增加了内部上拉电阻的功耗,虽然功耗通常较小,但在对功耗要求极高的系统中可能会有影响。

- 如果外部信号需要将引脚拉低,上拉电阻会对信号产生一定的负载效应。

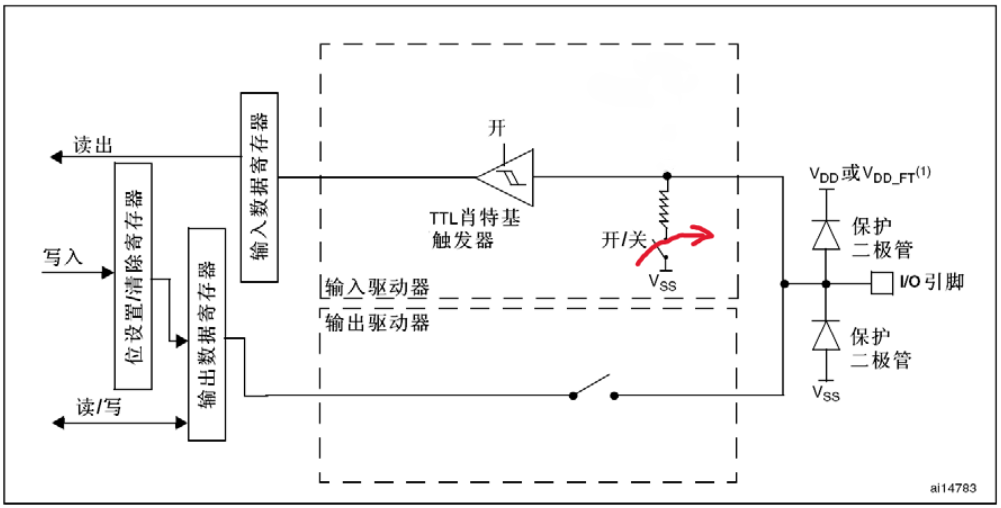

2.6.3 下拉输入

下拉输入模式下,引脚内部连接了一个下拉电阻到地(GND)。当外部电路没有连接或者输入为高阻态时,引脚会通过下拉电阻被拉低到低电平;当外部电路将引脚拉高时,引脚电平变为高电平。这样能确保在没有外部信号输入时,引脚有一个确定的低电平状态,避免引脚电平出现不确定情况。

应用场景:检测高电平,NPN信号,开关量。

- 优点

- 保证在无外部信号输入时,引脚处于稳定的低电平状态,增强系统稳定性,避免引脚电平不确定。

- 同样适用于一些特定的按键检测或传感器信号检测场景,能减少干扰。

- 缺点

- 存在内部下拉电阻的功耗问题,尽管功耗一般不大。

- 外部信号拉高引脚时,下拉电阻会产生负载影响。

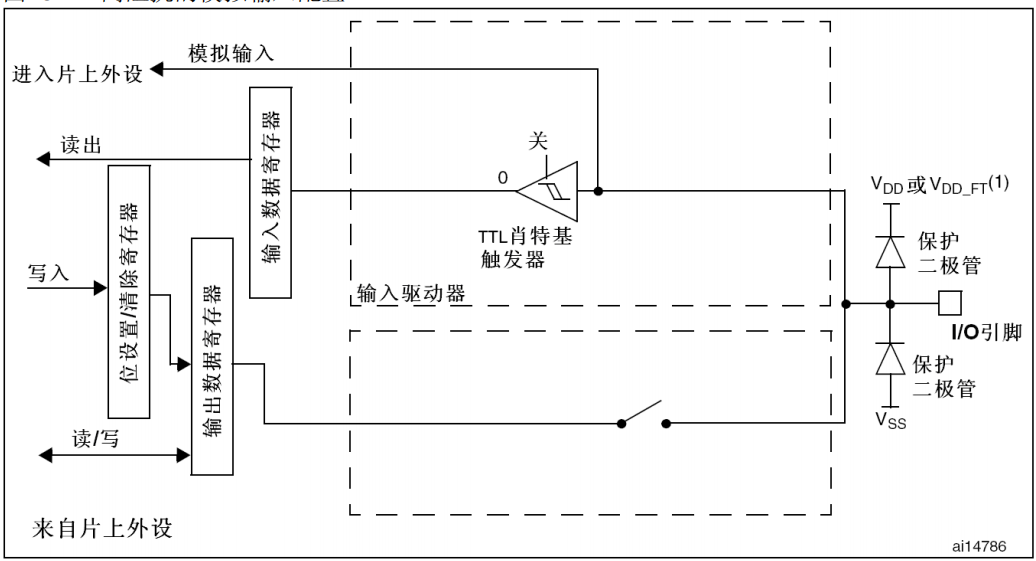

2.6.4 模拟输入

模拟输入模式主要用于将 GPIO 引脚连接到片上的模拟外设,如模数转换器(ADC)。在这种模式下,GPIO 引脚不再用于数字信号的输入或输出,而是专门用于采集模拟信号。上拉和下拉电阻也被禁止。这是为了避免对模拟信号产生干扰,让引脚能够直接连接到模拟电路,保证模拟信号的准确性和稳定性。

应用场景:ADC模拟输入、低功耗模式。

- 优点

- 能直接采集模拟信号,避免数字电路对模拟信号的干扰,保证了模拟信号的准确性和完整性。

- 为连接各种模拟传感器提供了方便,可实现对物理量的精确测量。

- 缺点

- 只能用于模拟信号采集,不能处理数字信号,功能相对单一。

- 对外部模拟信号的质量要求较高,容易受到噪声和干扰的影响。

2.6.5开漏输出

在开漏输出模式下,GPIO 引脚内部的输出级电路只有 N 沟道 MOS 管,其漏极(Drain)作为输出端直接连接到外部电路,而没有上拉电阻连接到电源。当输出控制信号为低电平时,MOS 管导通,引脚输出低电平;当输出控制信号为高电平时,MOS 管截止,此时引脚处于高阻态(浮空状态),引脚电平由外部上拉电阻决定。

应用场景:如模拟I2C总线,用于与其他设备进行通信。

- 优点

- 具有良好的电平兼容性,可通过外接不同电压的上拉电阻与不同电平标准的设备通信。

- 支持线与功能,多个开漏输出引脚连接可实现逻辑与操作,适用于总线通信等场景。

- 缺点

- 高电平驱动能力依赖外部上拉电阻,上拉电阻阻值选择不当会影响信号的上升时间和驱动能力。

- 需要外接上拉电阻,增加了硬件成本和电路板复杂度。

2.6.6 推挽输出

推挽输出电路由一个 P 沟道 MOS 管和一个 N 沟道 MOS 管组成互补结构。当输出高电平时,P 沟道 MOS 管导通,N 沟道 MOS 管截止,此时引脚通过导通的 P 沟道 MOS 管连接到电源,输出高电平;当输出低电平时,N 沟道 MOS 管导通,P 沟道 MOS 管截止,引脚通过导通的 N 沟道 MOS 管连接到地,输出低电平。

应用场景:用于驱动外部电路,如控制LED灯、驱动其他逻辑电路等。

- 优点

- 驱动能力强,无论是输出高电平还是低电平,都能为外部负载提供较大的电流,可直接驱动小功率负载。

- 电平转换速度快,能够快速切换高低电平,适用于对信号切换速度要求较高的场景。

- 缺点

- 不具备线与功能,多个推挽输出引脚不能直接连接在一起,否则可能会导致短路损坏器件。

- 电平兼容性较差,输出电平固定,难以直接与不同电平标准的设备连接。

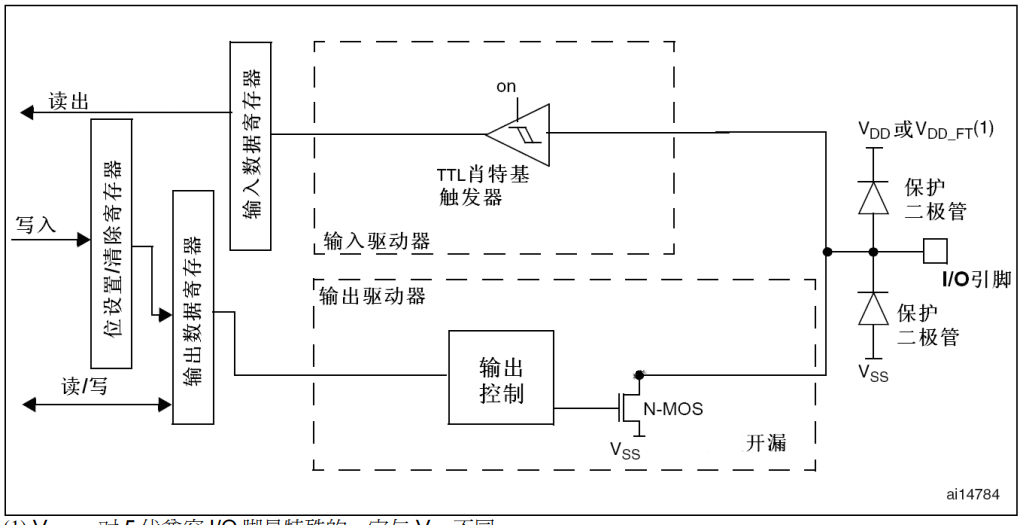

2.6.7开漏复用输出

在这种模式下,GPIO 引脚被复用为片上外设的特定功能,同时采用开漏输出的方式进行信号输出。也就是说,引脚的输出控制由对应的片上外设负责,而输出电路结构为开漏形式。

应用场景:连接到外设的特殊功能引脚,如片内I2C总线通信引脚、故障信号输出等。

- 优点

- 兼具复用功能和开漏输出的优势,可将 GPIO 引脚复用为特定外设功能,同时具有良好的电平兼容性和线与功能,适用于总线通信协议。

- 在多设备共享总线的系统中,能有效避免信号冲突,实现可靠通信。

- 缺点

- 高电平驱动能力依赖外部上拉电阻,上拉电阻的选择会影响信号质量和系统性能。

- 需要外接上拉电阻,增加了硬件成本和设计复杂度。

2.6.8 推挽复用输出

复用推挽输出的内部电路结构与普通推挽输出类似,由一个 P 沟道 MOS 管和一个 N 沟道 MOS 管组成互补结构。不同之处在于,其输出控制信号不再由用户直接通过 GPIO 寄存器控制,而是由对应的片上外设来控制。

应用场景:连接到外设的特殊功能引脚,如片内UART串口通信引脚、PWM输出等。

- 优点

- 结合了复用功能和推挽输出的优点,既可以将 GPIO 引脚复用为片上外设的功能,又能提供较强的驱动能力和快速的电平转换。

- 适用于需要高速、大电流驱动的外设,如定时器 PWM 输出、串口通信的 TX 引脚等。

- 缺点

- 与推挽输出类似,不具备线与功能,多个复用推挽输出引脚不能直接连接。

- 电平兼容性相对较差,可能需要额外的电平转换电路来与不同电平标准的设备连接。

2.7 输入配置

当I/O端口配置为输入时:

- 输出缓冲器被禁止

- 施密特触发输入被激活

- 根据输入配置(上拉,下拉或浮动)的不同,弱上拉和下拉电阻被连接

- 出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器

- 对输入数据寄存器的读访问可得到I/O状态

2.8 输出配置

当I/O端口配置为输出时:

- 输出缓冲器被激活

- 开漏模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将端口置于高阻状态(PMOS从不被激活)。

- 推挽模式:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将激活P-MOS。

- 施密特触发输入被激活

- 弱上拉和下拉电阻被禁止

- 出现在I/O脚上的数据在每个APB2时钟被采样到输入数据寄存器

- 访问I/0状态

- 在开漏模式时,对输入数据寄存器的读访问可得到I/O状态

- 在推挽式模式时,对输出数据寄存器的读访问得到最后一次写的值。

2.9 复用功能配置

当I/O端口配置为复用时:

- 在开漏或推挽式配置中,输出缓冲器被打开

- 内置外设的信号驱动输出缓冲器(复用功能输出)

- 施密特触发输入被激活

- 弱上拉和下拉电阻被禁止

- 在每个APB2时钟周期,出现在I/O脚上的数据被采样到输入数据寄存器

- 开漏模式时,读输入数据寄存器时可得到I/O口状态

- 在推挽模式时,读输出数据寄存器时可得到最后一次写的值

2.10 模拟输入配置

当I/O端口被配置为模拟输入配置时:

- 输出缓冲器被禁止;

- 禁止施密特触发输入,实现了每个模拟I/O引脚上的零消耗。施密特触发输出值被强置为’0’;

- 弱上拉和下拉电阻被禁止;

- 读取输入数据寄存器时数值为’0’。

2.11 注意事项

- 复位期间和刚复位后,复用功能未开启,I/O端口被配置成浮空输入模式。 复位后,JTAG引脚被置于输入上拉或下拉模式,具体是哪种模式需要看数据手册。

- 使用默认复用功能前必须对端口位配置寄存器编程。 对于复用的输入功能,端口必须配置成输入模式(浮空、上拉或下拉)且输入引脚必须由外部驱动。

- 对于复用输出功能,端口必须配置成复用功能输出模式(推挽或开漏)。

- 对于双向复用功能,端口位必须配置复用功能输出模式(推挽或开漏)。这时,输入驱动器被配置成浮空输入模式。

- 如果把端口配置成复用输出功能,则引脚和输出寄存器断开,并和片上外设的输出信号连接。如果软件把一个GPIO脚配置成复用输出功能,但是外设没有被激活,它的输出将不确定。

- 锁定机制允许冻结IO配置。当在一个端口位上执行了锁定(LOCK)程序,在下一次复位之前,将不能再更改端口位的配置。

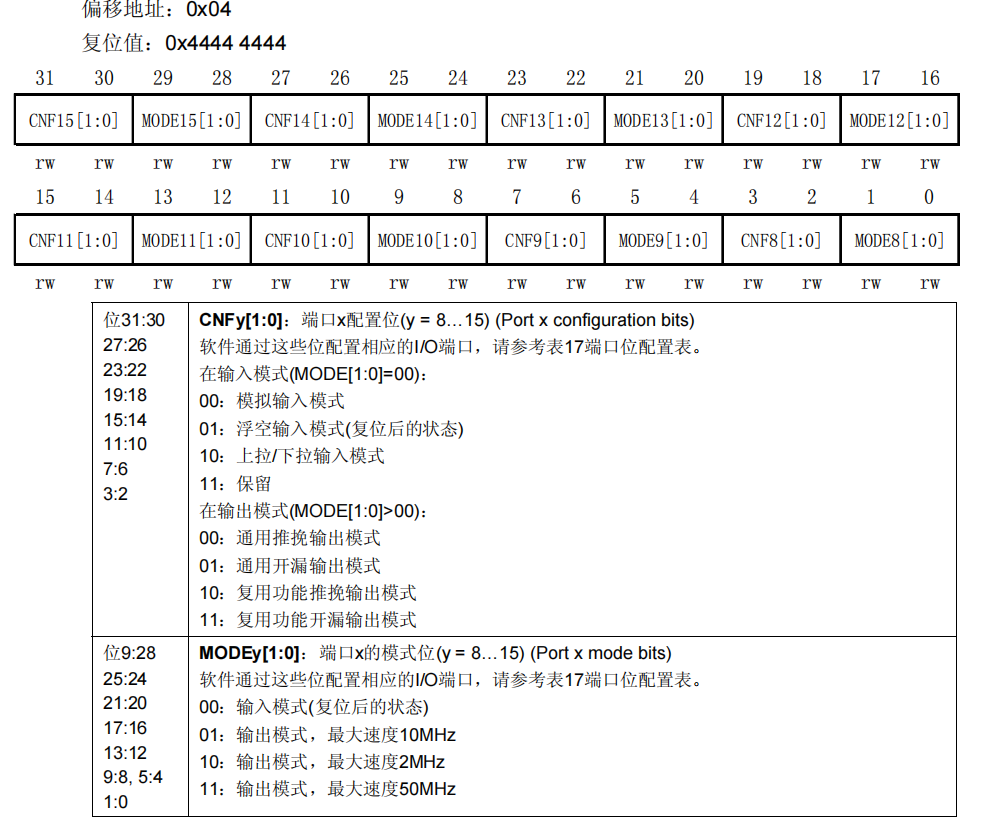

3.GPIO的相关寄存器

3.1 端口配置寄存器

端口配置寄存器包含GPIOx_CRH和GPIOx_CRL。复位后01000100010001000100010001000100,表示全部全部引脚为浮空输入模式。

GPIOx_CRL配置引脚0-7,GPIOx_CRH配置引脚8-15。

例如配置配置引脚PA1时,需要配置GPIOA_CRL。

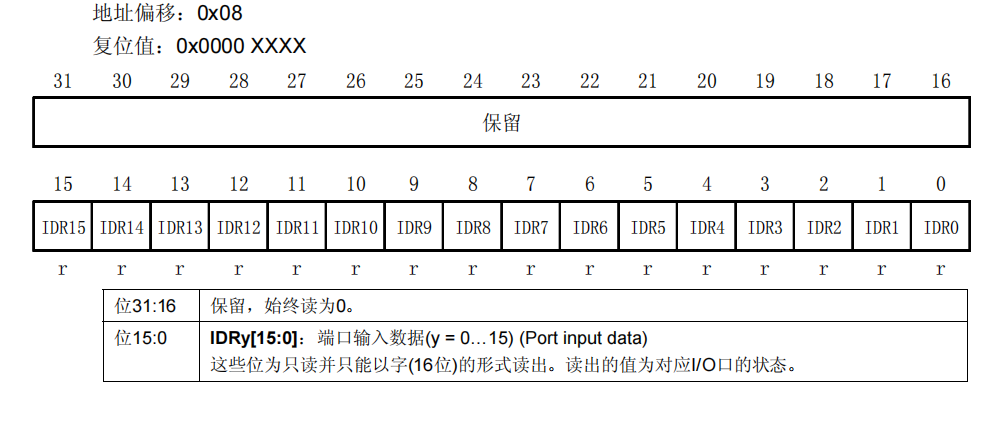

3.2端口输入数据寄存器

端口输入数据寄存器名为GPIOx_IDR。复位后全部为0。

例如要读取PA5引脚输入的电平,直接使用GPIOA_IDR&(1<<5)即可。

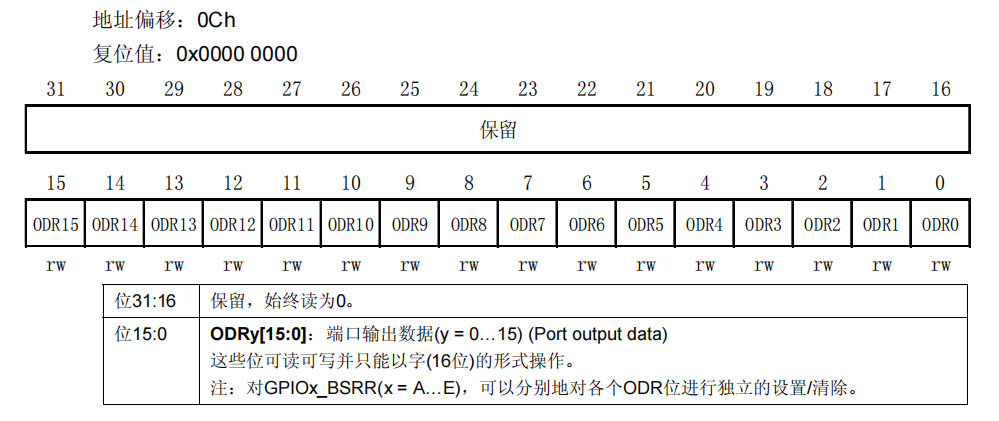

3.3端口输出数据寄存器

端口输出数据寄存器名为GPIOx_ODR。复位后全部为0。

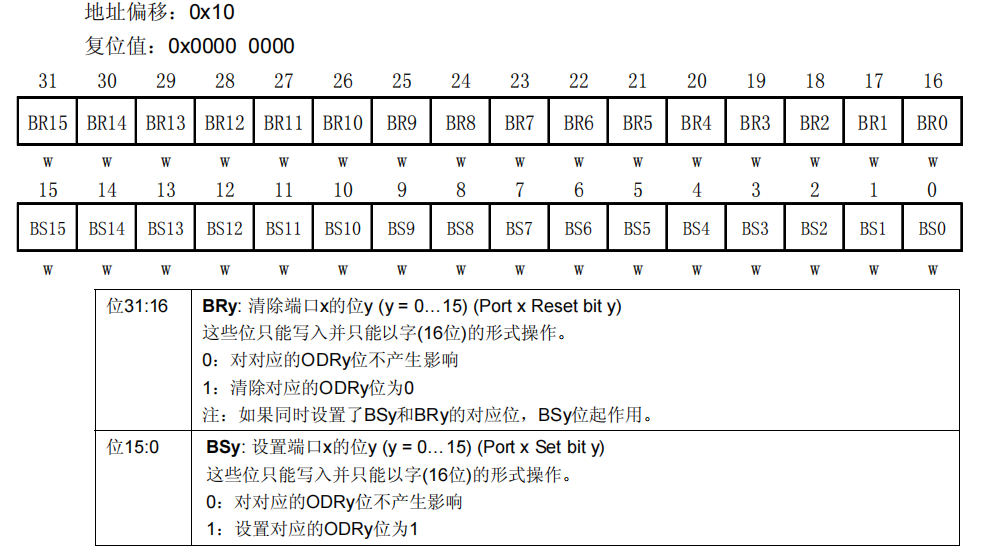

3.4端口位设置/清除寄存器

端口位设置/清除寄存器名为GPIOx_BSRR。复位后全部为0。

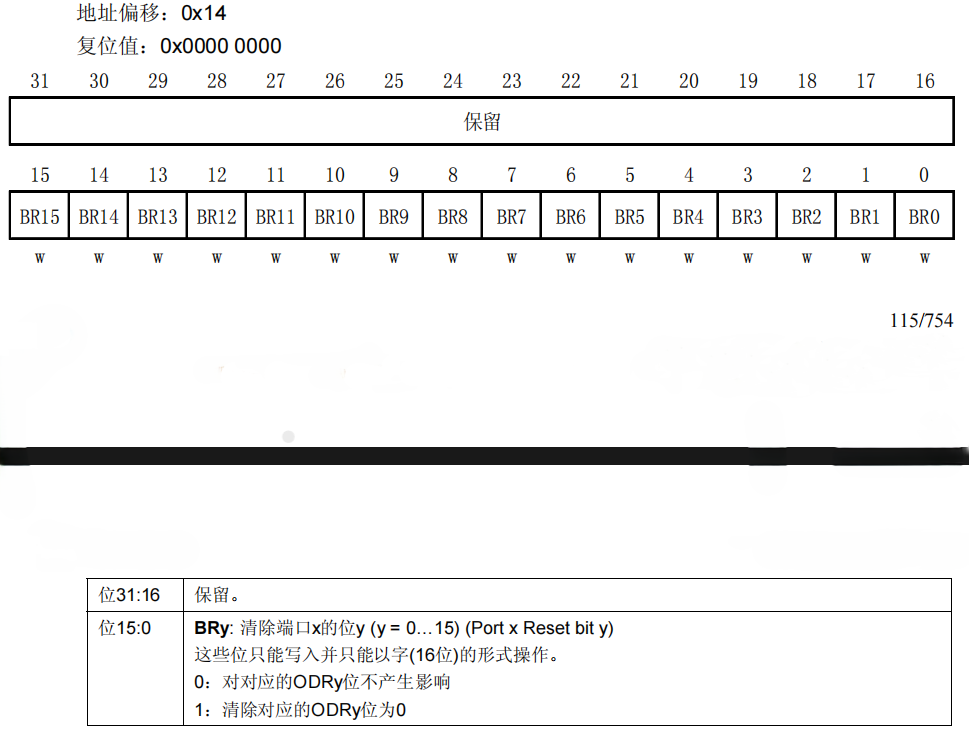

3.4端口位清除寄存器

端口位清除寄存器名为GPIOx_BRR。复位后全部为0。

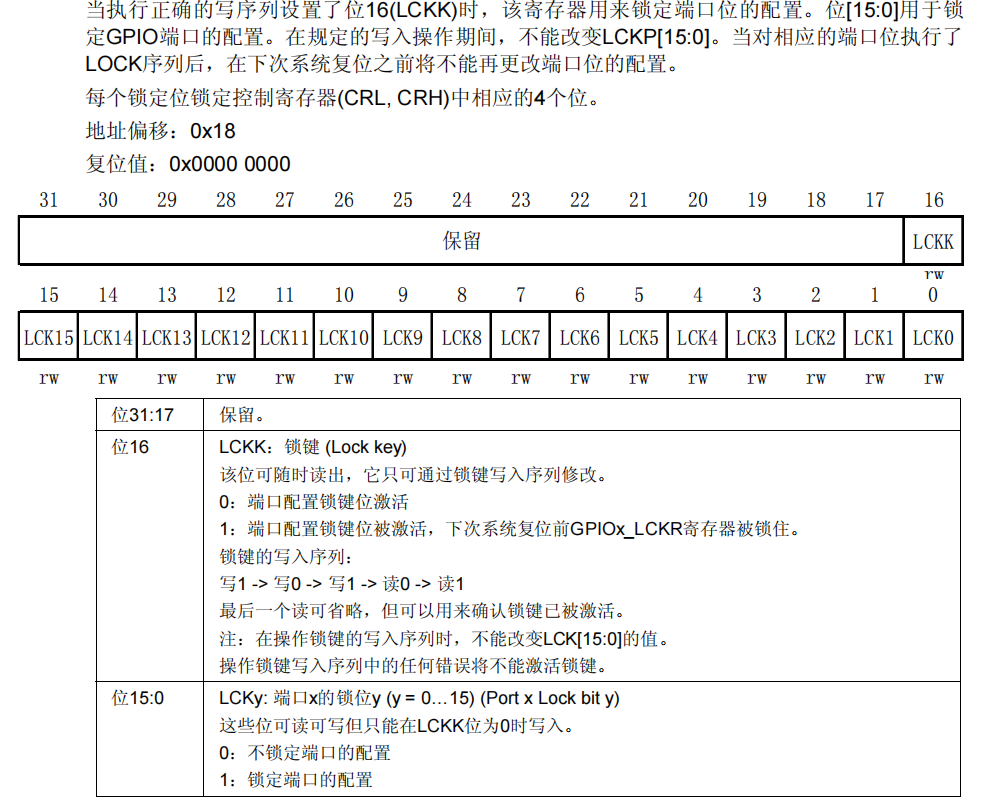

3.5 端口配置锁定寄存器

端口配置锁定寄存器名为GPIOx_LCKR。复位后全部为0。

4. 配置基础GPIO

- 步骤 1:使能 GPIO 时钟

在使用任何 GPIO 之前,需要先使能相应 GPIO 端口的时钟。时钟控制寄存器位于 RCC(Reset and Clock Control)外设中。例如,如果要使用 GPIOA 端口,需要使能 GPIOA 的时钟。 - 步骤 2:配置 GPIO 模式

GPIO 的模式由 GPIO 端口的配置寄存器(GPIOx_CRL 和 GPIOx_CRH)来控制,其中x代表端口号(A、B、C 等)。CRL用于配置引脚 0 - 7,CRH用于配置引脚 8 - 15。 - 步骤 3:设置 GPIO 输出类型和速度(仅适用于输出模式)

在输出模式下,还可以设置 GPIO 的输出类型(推挽输出、开漏输出等)和输出速度。这些设置同样在GPIOx_CRL和GPIOx_CRH寄存器中完成。 - 步骤 4:读取或写入 GPIO 数据

如果是输入模式,可以通过读取GPIOx_IDR(输入数据寄存器)来获取引脚的电平状态;如果是输出模式,可以通过写入GPIOx_ODR(输出数据寄存器)或GPIOx_BSRR(位设置 / 复位寄存器)来控制引脚的电平。

4.1 直接通过寄存器配置

例如使用寄存器配置 GPIOA 的引脚 0 为推挽输出模式。

// 步骤1:使能GPIOA时钟

RCC->APB2ENR |= RCC_APB2ENR_IOPAEN;

// 步骤2和3:配置GPIOA的引脚0为推挽输出模式,最大速度为50MHz

// 先清除GPIOA_CRL寄存器中对应引脚0的4位(MODE0[1:0]和CNF0[1:0])

GPIOA->CRL &= ~(0x0F << 0);

// 设置MODE0[1:0]为0x03,表示输出模式,最大速度50MHz

GPIOA->CRL |= (0x03 << 0);

while (1) {

// 步骤4:设置GPIOA的引脚0为高电平

GPIOA->BSRR = (1 << 0);

delay_ms(500);

// 步骤4:设置GPIOA的引脚0为低电平

GPIOA->BSRR = (1 << 16);

delay_ms(500);

}

可见使用寄存器直接配置仅仅只需两条代码,代码效率非常高,但是可读性很差,不明所以。

4.2 通过标准库配置

// 步骤1:使能GPIOA时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);

// 步骤2:定义并初始化GPIO初始化结构体

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; // 选择引脚0

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP; // 推挽输出模式

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; // 输出速度为50MHz

// 步骤3:初始化GPIOA的引脚0

GPIO_Init(GPIOA, &GPIO_InitStructure);

while (1) {

// 设置GPIOA的引脚0为高电平

GPIO_SetBits(GPIOA, GPIO_Pin_0);

delay_ms(500);

// 设置GPIOA的引脚0为低电平

GPIO_ResetBits(GPIOA, GPIO_Pin_0);

delay_ms(500);

}

可见第二步与第三步的工作都通过GPIO_Init(GPIO_TypeDef* GPIOx, GPIO_InitTypeDef* GPIO_InitStruct);这个函数来实现,相比于寄存器操作,牺牲了一部分资源,获取更好的可移植性和可读性。

4.3 通过hal库配置

int main(void)

{

// 初始化HAL库

HAL_Init();

// 配置系统时钟

SystemClock_Config();

// 初始化GPIO为输入模式

GPIO_Input_Init();

GPIO_PinState pinState;

while (1)

{

// 设置GPIO引脚为高电平

HAL_GPIO_WritePin(GPIOA, GPIO_PIN_5, GPIO_PIN_SET);

HAL_Delay(500);

// 设置GPIO引脚为低电平

HAL_GPIO_WritePin(GPIOA, GPIO_PIN_5, GPIO_PIN_RESET);

HAL_Delay(500);

}

}

void GPIO_Input_Init(void)

{

GPIO_InitTypeDef GPIO_InitStruct = {0};

// 使能GPIOA的时钟

__HAL_RCC_GPIOA_CLK_ENABLE();

// 配置GPIO引脚

GPIO_InitStruct.Pin = GPIO_PIN_0;

GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP; // 推挽输出模式

GPIO_InitStruct.Pull = GPIO_NOPULL; // 无上下拉

GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW; // 低速

// 初始化GPIO

HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

}

HAL 库遵循硬件抽象的设计原则,将底层硬件的操作细节封装起来,为开发者提供统一的、简洁的 API 接口。开发者无需深入了解具体硬件寄存器的操作,只需调用相应的函数即可完成各种硬件功能的配置和控制,降低了开发难度和门槛。

4.4 通过CUBEMX配置

- Output level:GPIO 引脚作为输出模式时的初始电平状态,也就是在完成 GPIO 初始化后引脚呈现的高低电平情况。

- Mode:对于输出模式可选择推挽输出(Output Push Pull)或开漏输出(Output Open Drain);输入模式可选择浮空输入(Input Floating)、上拉输入(Input Pull-up)或下拉输入(Input Pull-down)等。

- Pull-up/Pull-down:设置是否使用上拉或下拉电阻。

- Speed:设置 GPIO 的输出速度,有低速、中速、高速等选项。

4.5 各种开发方式对比

| 对比维度 | 寄存器开发 | 标准库开发 | HAL开发 | CubeMX开发 |

|---|---|---|---|---|

| 开发难度 | 高。需要深入了解芯片的硬件架构和寄存器功能,开发者要手动操作每个寄存器的位,对硬件知识要求极高。 | 中。虽然标准库对寄存器操作进行了一定封装,但仍需对硬件有较好的理解,掌握外设的基本原理。 | 低。HAL库对硬件进行了高度抽象,提供统一、简洁的API接口,降低了开发门槛,适合初学者。 | 最低。CubeMX以图形化界面配置项目,自动生成初始化代码,开发者无需手动编写大量初始化代码,操作简单直观。 |

| 代码可移植性 | 低。不同型号的STM32芯片寄存器地址和功能可能不同,代码移植时需要进行大量修改。 | 中。标准库在同一系列芯片中有一定可移植性,但不同系列之间仍需调整部分代码。 | 高。HAL库为不同系列的STM32芯片提供统一API,代码可在不同芯片间方便移植,只需少量修改。 | 高。CubeMX可针对不同芯片进行配置并生成代码,生成的代码结构一致,便于移植。 |

| 开发效率 | 低。手动编写寄存器操作代码工作量大,调试时间长,开发周期长。 | 中。标准库提供函数封装,减少了寄存器操作代码量,提高了一定开发效率。 | 高。使用HAL库的高级API可快速完成硬件初始化和功能实现,开发速度快。 | 最高。通过图形化界面快速配置项目,自动生成代码,大幅缩短开发时间。 |

| 性能表现 | 高。直接操作寄存器,无额外封装开销,代码执行效率高,响应速度快。 | 较高。标准库接近寄存器操作,性能损失较小,但仍有一定封装开销。 | 中。HAL库为追求通用性和易用性,存在一定性能损失,不过大多数场景可接受。 | 中。CubeMX生成的代码基于HAL库或LL库,性能与所选库相关。 |

| 代码可读性 | 低。大量寄存器操作代码,逻辑复杂,代码可读性差,维护困难。 | 中。标准库函数有一定命名规范,代码可读性有所提高,但仍需了解硬件原理。 | 高。HAL库函数命名清晰,参数设置直观,代码可读性好,易于维护。 | 高。CubeMX生成的代码结构清晰,注释详细,可读性好。 |

| 灵活性 | 高。可精确控制每个寄存器的位,能实现复杂的硬件操作和优化。 | 中。标准库提供一定灵活性,但受限于库函数的封装,部分特殊需求实现较困难。 | 低。HAL库为保证通用性,部分功能封装较固定,定制化难度较大。 | 低。主要通过图形化界面配置,定制化能力依赖于工具提供的选项,复杂需求实现受限。 |

| 学习成本 | 高。需要掌握芯片硬件架构、寄存器功能和位操作知识,学习周期长。 | 中。需学习标准库函数的使用和外设基本原理,有一定学习成本。 | 低。掌握HAL库API接口和基本开发流程即可进行开发,学习成本低。 | 最低。熟悉图形化界面操作和基本配置选项就能快速上手。 |

| 适用场景 | 对性能要求极高、资源受限的场景,如嵌入式实时系统、对功耗和响应时间敏感的应用。 | 对性能有一定要求,同时希望减少寄存器操作复杂度的项目,适合有一定硬件基础的开发者。 | 快速开发、对性能要求不是特别苛刻的项目,以及初学者入门学习。 | 项目初期快速搭建框架、初始化配置,尤其适合多外设配置的复杂项目。 |

文章中有错误之处 敬请谅解。

浙公网安备 33010602011771号

浙公网安备 33010602011771号