双ADC配置

1. 记录双ADC交替采样的学习过程

1.1 目的

ADC的转换有两个过程:采样、量化。采样和量化均需要一定时间,但同一时间只有一个ADC可以对同一个通道进行采样,但量化是独立进行的。

所以我们可以先让一个ADC进行采样,在其量化过程中,使用另一个ADC通道对该模拟量进行采样,以提高采样率。理论上采样率能翻倍。

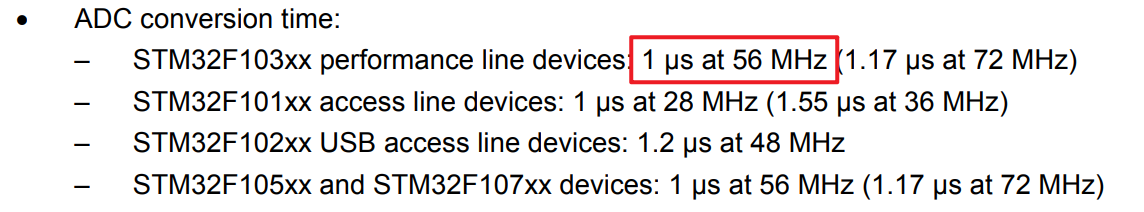

单个ADC的最大采样速度为1Mhz,我们的目的就是利用双ADC交替采样来提高采样率。

1.2 ADC时钟配置

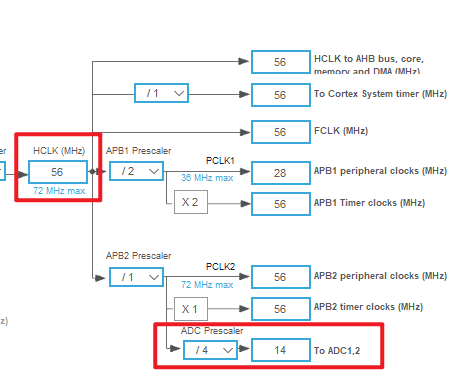

在stm32f103中,ADC1,2的时钟来源于APB2总线,经过一个分频器得到ADC时钟。ADC时钟最大频率不能超过14Mhz。

但由于时钟树的约束关系,当ADC时钟配置为14Mhz时,系统时钟只能被限制到56Mhz。

我这里由于特殊需求,需要提高ADC采样率,将ADC时钟配置为最大14Mhz,总线时钟因此被限制在56Mhz。

1.3 双ADC模式

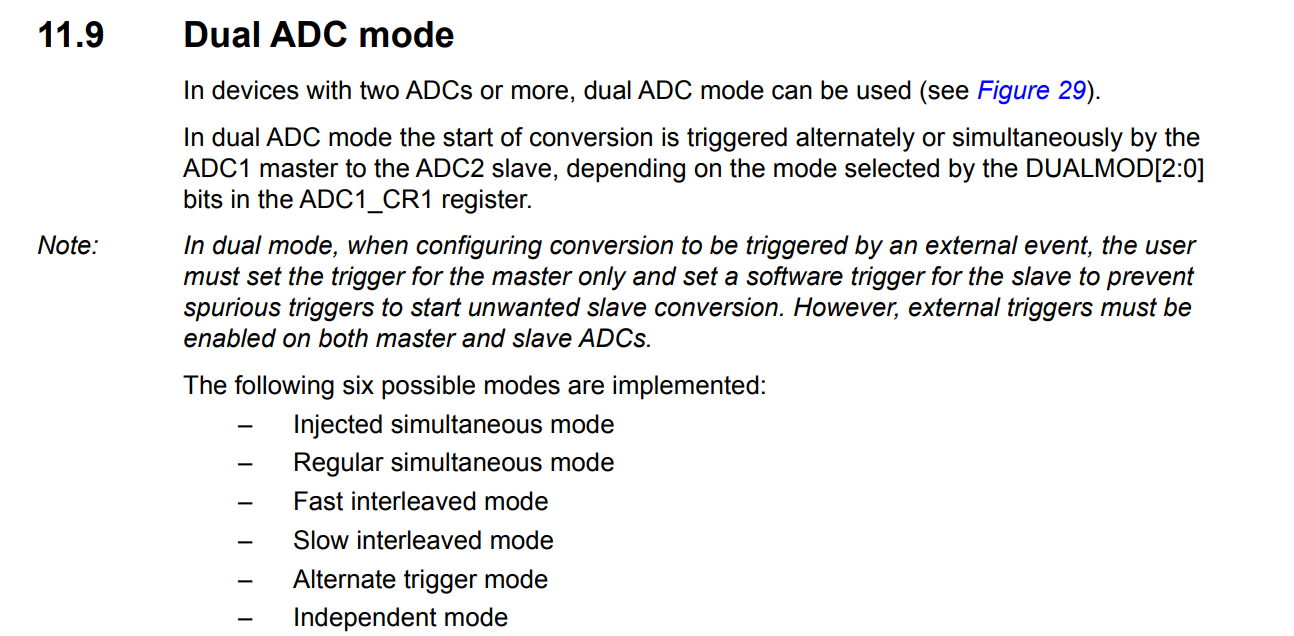

在拥有多个ADC的设备上才可以使用双ADC模式。

双ADC模式转换的开始是由主ADC1交替或同步触发从ADC2,取决于寄存器的配置。

在双ADC模式中,当配置外部事件触发转换时,用户只能设置主ADC(ADC1)的触发模式,同时给从ADC(ADC2)设置一个软件触发来防止从ADC进行一些意料之外的转换。但是,主从ADC都需要配置外部触发使能。

以下是6中可配置的模式:

-

注入组同步模式

-

规则组同步模式

-

快速交替模式

-

慢速交替模式

-

交替触发模式

-

独立模式

也可以使用这些中的组合

![]()

我这里由于需要周期性地采样,不存在注入组的情况,所以配置模式为规则组同步模式(Regular simultaneous mode)

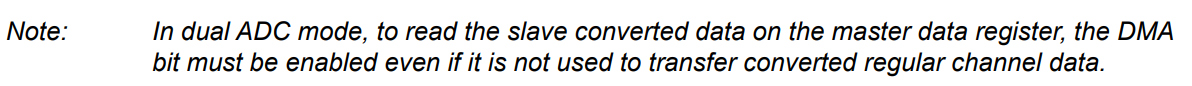

在双ADC模式下,为了在主ADC的数据寄存器中读取到从ADC的数据,DMA传输位必须使能,即使它并不传输转换后的规则组通道数据。

1.4 快速交替采样模式

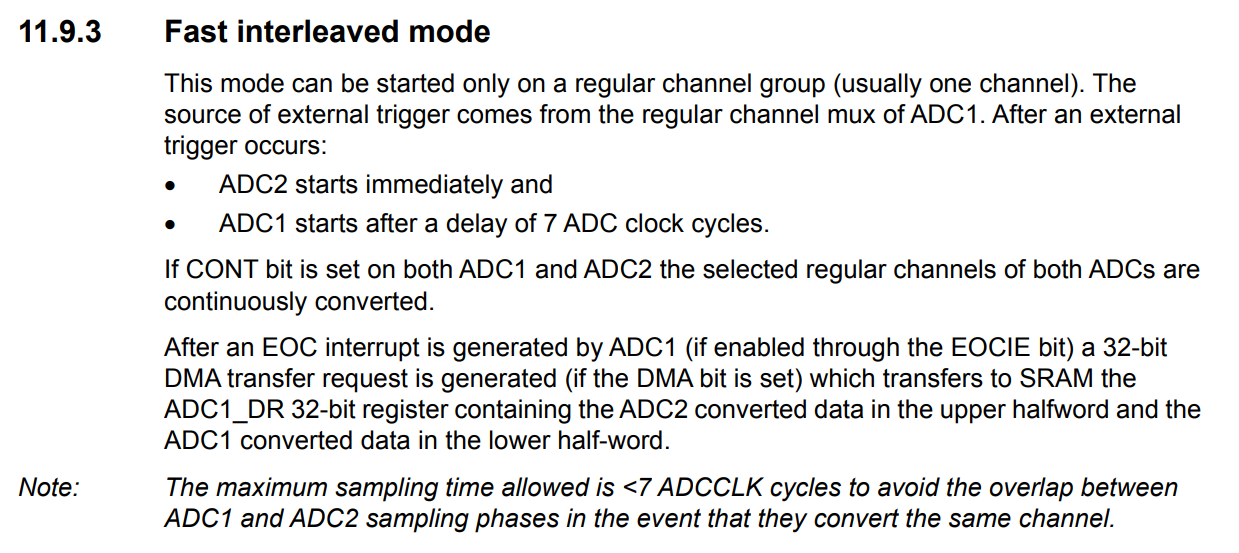

这个模式只能在一个规则通道组开启(通常只用于一个通道)。外部中断源来自于ADC1规则通道组(下图regular group)的复用。

我们在这里配置为TIM3_TRGO

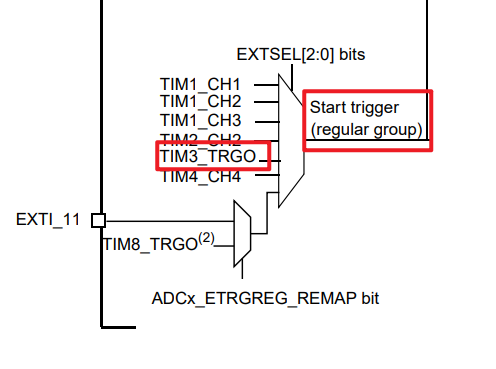

当外部中断源触发时:

- ADC2立即开始转换

- ADC1在7个ADC时钟周期后进行转换

ADC1,ADC2的CONT位需要被置位,这样所有ADC才能开启连续转换

当ADC1也采集完后,如果EOCIE被使能,那么会产生一个EOC(End of Conversion)中断,与此同时,如果DMA传输被打开,那么会产生一个32bit的DMA传输请求,它将ADC1_DR数据寄存器中32bit的数据传输到SRAM中,其中:

- 高16bit放置ADC2转换结果

- 低16bit放置ADC1转换结果

注:最大的采样时间不允许超过7个ADC时钟周期,用于避免ADC1,ADC2在对同一个通道的采样阶段出现数据重叠,为了理解这一概念,请看下面:

双ADC交错连续采样示意图如下:灰色块为采样阶段,白色块为量化阶段。

当一个ADC的采样阶段(灰色块)时间过长时,另一个ADC的采样已经到来,这时2者对同一个通道同时采样,造成了数据的混叠,看似提高了采样周期,但实际并未真正有效地提高采样率,并且由于两个ADC的充电电容产生竞争而降低精度。

浙公网安备 33010602011771号

浙公网安备 33010602011771号