Quartus & Modelsim初始化问题

Quartus & Modelsim初始化问题

问题也不是我一个人遇到:http://bbs.ednchina.com/BLOG_ARTICLE_271118.HTM

印象中verilog编程,不给初,就是默认为零哦!

但是Modelsim不赋初值,他就不是零;之后如果在复位中也没写道,到必然出错。

所以严谨的代码风格,完整的时序模型,于己于人都是一种完美!

调试一个fifo2sram2fifo的工程,用uart来显示,总是规律性的出现问题。睡觉自己当年设计的时候全凭YY。

在Quartus II自然没问题,他默认为0 的;

但是好歹不好意思杂用Quartus II自带的Simulation了,无奈,用Modelsim看看波形;问题也从此开始:

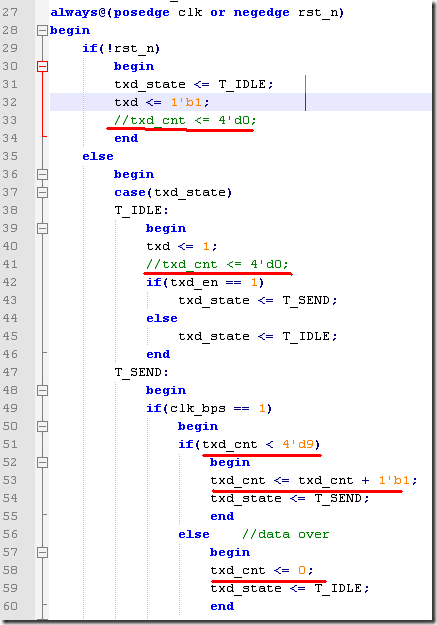

如下图所示,注释部分的txd_cnt本身没多大意义,只在T_SEND的时候才具有意义,因此当年因为偷懒,以及嫩,没写上去。

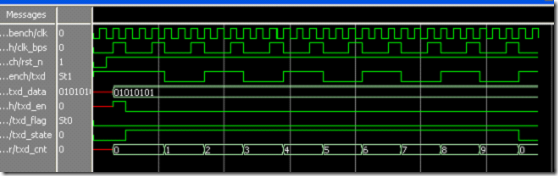

但是仿真波形如下,你可以看得到txd_cnt,txd,state的异常

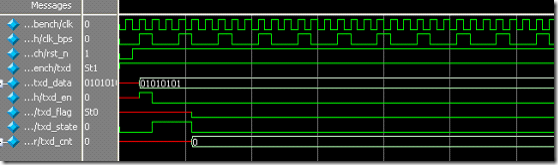

但是把上述注释部分加上,即完整时序,写入各种状态的初始化后:

哎,严谨的代码,完整的风格,于己于人,总会事半功倍的!

posted on 2012-03-13 09:03 CrazyBingo 阅读(2794) 评论(1) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号