qii, sopc, nios ii 10.1 IP核设计,LED验证死活不行,感觉很神奇

学sopc也有个很长一段时间,最近第一次自己设计IP核。

参照了艾米的自定义IP核:SRAM,12864的例子,以及黑金的PWM的例子,同时看了两本书,以及《Avalon-MM Interface Specialtion》,最后按部就班设计,为了验证,先从简单的开始,可是sram好像可以,lcd1602和led 都不行,在此处我先讲解我设计led的流程:

(1)当然是led ip verilog的代码

/********************************************************************

* Module Name : Crazy_LED

* Author : Crazy Bingo

* Device : EP2C8Q208C8

* Version : Quartus II 10.1

* Date : 2011-2-24

* Description :

*********************************************************************/

module Crazy_LED

(

//Avalon Clock

input csi_clk,

input csi_rst_n,

//Avalon-MM

input [1:0] avs_address, //multiple of 4

input avs_chipselect,

// input [1:0] avs_byteenable_n, //1,2,4,8,16,54,128

input avs_write,

input [31:0] avs_writedata, //32bit cpu

// input avs_read,

// output [31:0] avs_readdata, //32bit cpu

//Avalon Conduit

output [1:0] coe_data

);

reg [1:0] coe_data_r;

always @(posedge csi_clk or negedge csi_rst_n)

begin

if (!csi_rst_n)

coe_data_r <= 0;

else if (avs_chipselect && avs_write && (avs_address == 0))

coe_data_r <= avs_writedata[1:0];

end

assign coe_data = coe_data_r;

endmodule

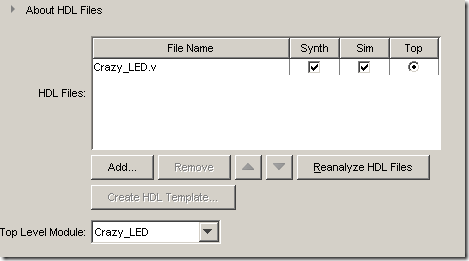

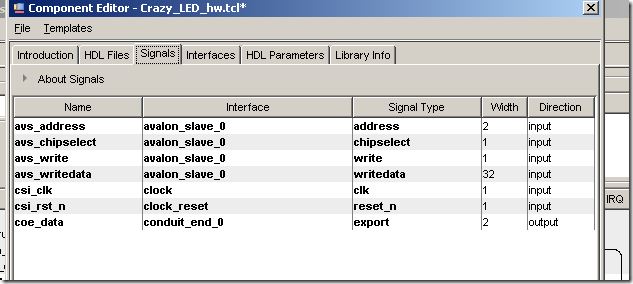

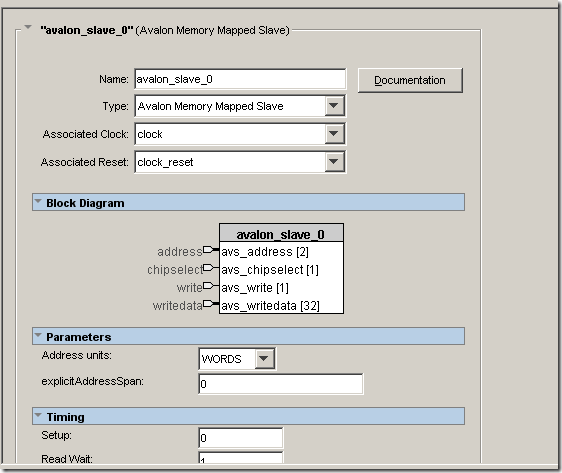

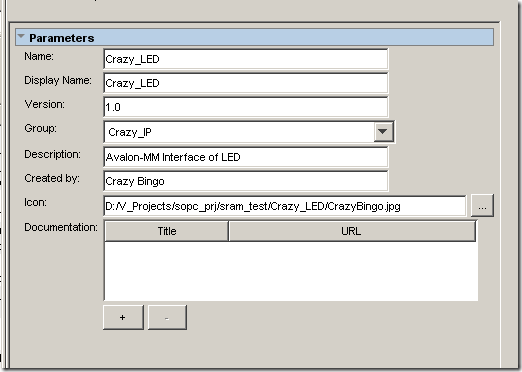

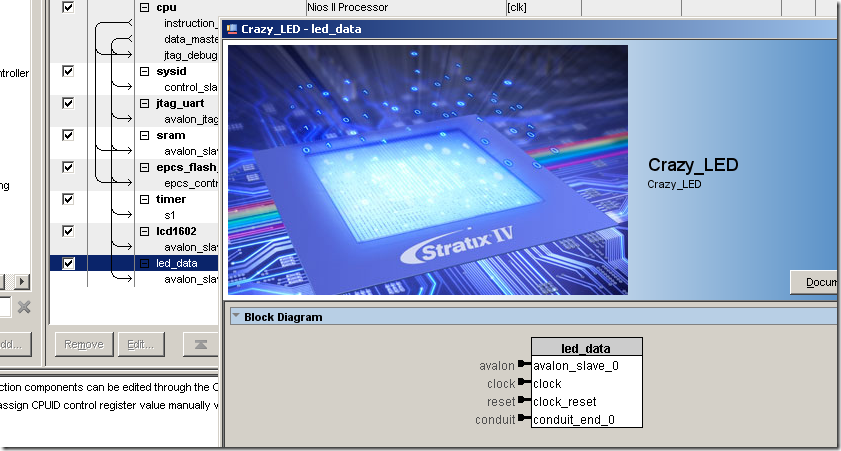

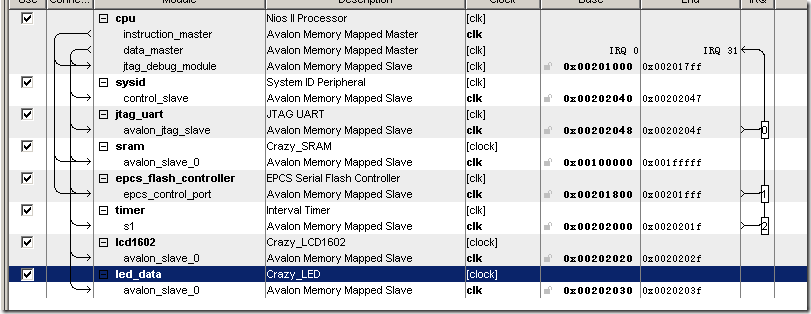

(2)在sopc中加入component

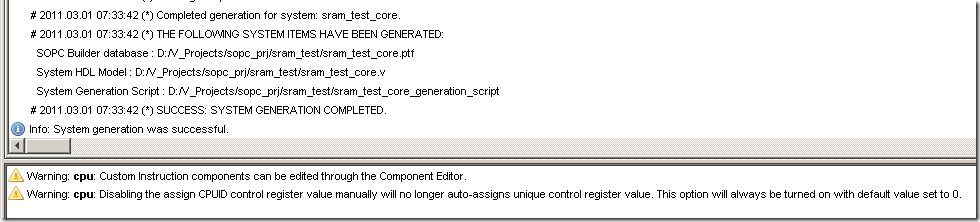

(2)加入led ip,generate

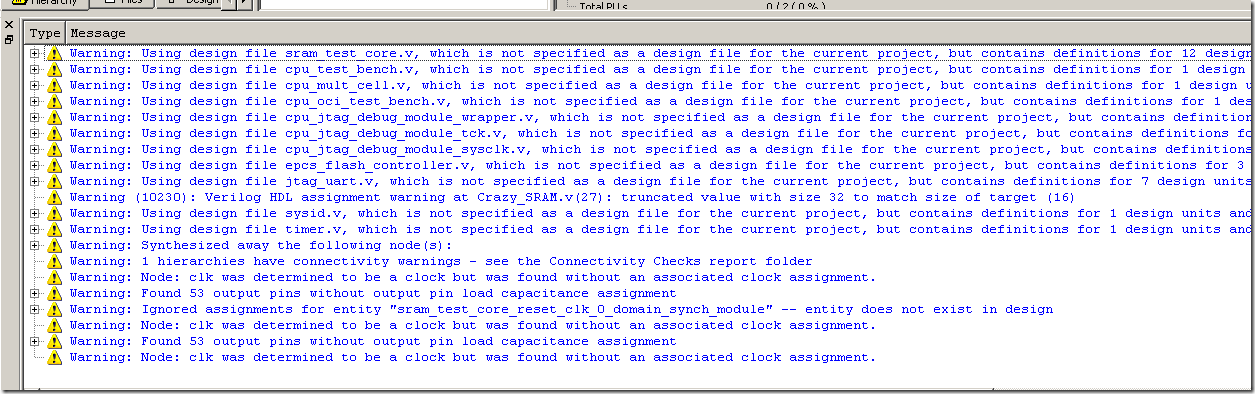

(顺便提下,10.1有这两个警告,有些人也碰到了,但是好像不用管,我试过pio-led没问难题的)

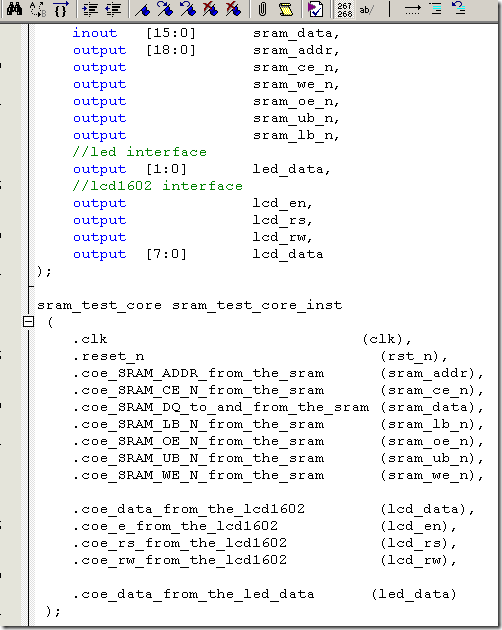

(3)qii top module,分配引脚,编译,ok(警告应该没事,不用理会)

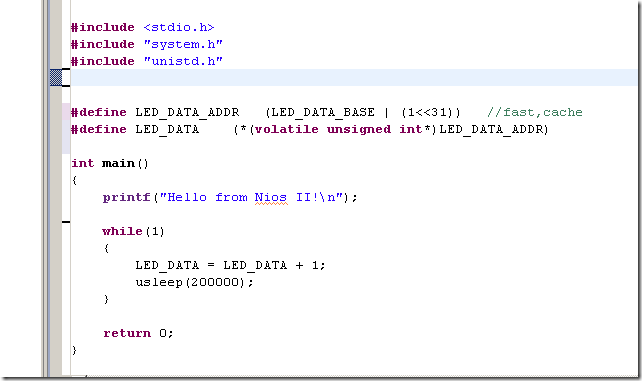

(4)新建nios2工程,涉及代码

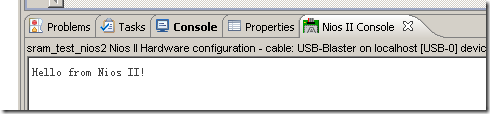

(5)下载pof后,run hardware,

printf运行了,但是led (2位)始终没反应,也没闪烁之类的,死了

各位前辈:

(1)address 信号可不可以直接不要

(2)是不是我在nios2 的管脚映射错了?

(3)这到底是为什么?????????????????

当然我确定硬件是木有问题的

我实在不知道哪里不行了,郁闷了n久n久,吃不好睡不香,早上6:30 就起了,这个世界让我好崩溃,有谁知道,给点指点,谢谢了

posted on 2011-03-01 08:04 CrazyBingo 阅读(1698) 评论(2) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号