ARMv7-A协处理器CP15寄存器

ARMv7-A架构保护系统控制协处理器CP15,主要用于处理存储系统相关的功能。CP15只能在特权模式下访问。CP15提供了16个32位主寄存器,命名为c0-c15。c0-c15寄存器可能对应多个不同的物理寄存器

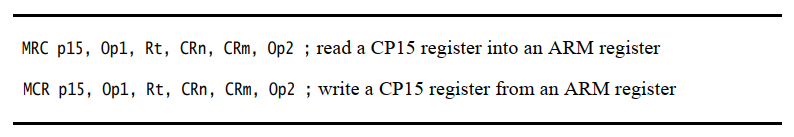

协处理器CP15寄存器访问包括读和写操作。

读操作即将CP15内的寄存器CRn的值读到通用寄存器Rt中,使用指令语法MRC, Op1, Rt, CRn, CRm, Op2;

写操作即将通用寄存器Rt的值写入CP15内的寄存器CRn中,使用指令语法MCR, Op1, Rt, CRn, CRm, Op2;

MRC:将CP15寄存器值读到ARM通用寄存器;

MCR:将ARM通用寄存器值写到CP15寄存器;

Op1 :协处理行为操作码;

Rt :ARM通用寄存器,不能是R15(PC);

CRn:协处理器CP15寄存器c0-c15;

CRm:附加目标寄存器,不需要附加信息,则设置为c0;

Op2 :区分同一编号不同的物理寄存器,例如分别访问c0中的MIDR和MPIDR,Op2值分别为0和1。默认情况下设置为0

示例:

将CP15寄存器c0的MIDR寄存器读到R1中。

MRC p15, 0, R1, c0, c0, 0

浙公网安备 33010602011771号

浙公网安备 33010602011771号