MOSFET/gate介绍

基本结构与引脚

-

源极 (Source - S): 电子流入沟道的位置。通常与衬底(B)短接并连接到电路的最低电位(如地GND)(这是理解体效应的关键)。

-

漏极 (Drain - D): 电子流出沟道的位置,连接到需要负载的较高电位点。

-

栅极 (Gate - G): 金属或多晶硅电极,与半导体沟道之间隔着一层非常薄的二氧化硅(SiO₂)绝缘层(Gate Oxide)。通过施加电压

V_GS来产生电场。输入控制端,阻抗极高(兆欧级GΩ)。 -

衬底/体区 (Body/Bulk - B): 器件的基础半导体区域,通常是P型硅 (P-Substrate),用于形成沟道。

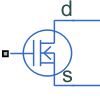

符号:

- 箭头方向: 始终指向芯片内部/N沟道形成处。

- 三个引出线:源极(S),栅极(G),漏极(D)。

- 箭头在源极S处: 指向内部表示电子源(N沟道器件),所以是NMOS。

- 衬底连接: 通常省略,隐含源极S和衬底B短接。有时会画出衬底引脚B用虚线连接。

- 衬底箭头方向: NPN结二极管的正向导通方向(从P到N)。

对于N沟道增强型MOSFET来说,要使其从截止状态进入导通状态,需要满足以下基本条件:

-

栅源电压条件:

V_GS > V_THV_GS: 是栅极(G)相对于源极(S)的电压。它必须是正电压(G比S电位高)。V_TH: 阈值电压(Threshold Voltage)。这是一个器件固有的重要参数,通常为(0.7V - 5V),由制造工艺决定(材料、掺杂浓度、氧化层厚度等)。这是形成导电沟道所需的最小栅源电压。- 意义: 只有当施加的

V_GS足够大(大于V_TH)时,才能建立起足够强的电场,将衬底表面反型成N型导电沟道。这是导通的先决条件。

-

漏源电压条件:

V_DS > 0VV_DS: 是漏极(D)相对于源极(S)的电压。在导通状态下,它必须大于0V(D比S电位高)。- 意义: 这是为电子流动提供驱动力。只有存在电位差(

V_DS> 0),电子才能在形成的N型沟道中从源极(电势较低,电子浓度高)向漏极(电势较高,正在吸收电子)定向移动,形成漏极电流I_D。当V_DS非常小(接近0V)但大于0V时,器件也能在V_GS > V_TH的条件下导通一个小电流。

关键总结: 对于N沟道增强型MOSFET来说,同时满足 V_GS > V_TH 和 V_DS > 0V 这两个条件,器件才会导通,形成漏极电流 I_D。

本文来自博客园,作者:cynety,转载请注明原文链接:https://www.cnblogs.com/connection0x00/p/18934729

浙公网安备 33010602011771号

浙公网安备 33010602011771号