面试必问并发编程内存模型JMM与内存屏障剖析 学习

总课程:

1、JMM。

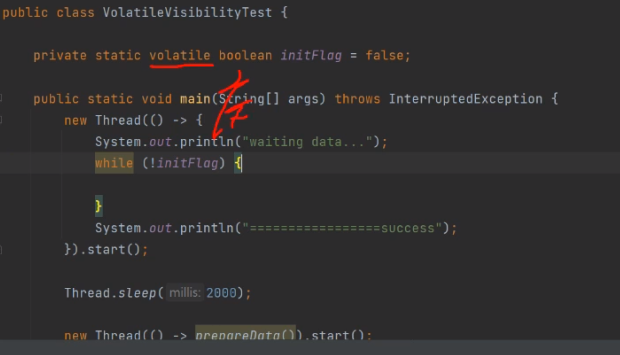

每个线程会产生一个变量副本。如下图所示,第二个变量修改了变量initFlag,但线程1并不会退出,是因为每个线程产生了副本。----解决方法:volatile

CPU缓存一致性协议:MESI机制,以及内存模型底层八大原子操作。

Volatile缓存可见性实现原理:底层实现主要通过汇编lock前缀指令,它会锁定这块内存区域的缓存(缓存行锁定),并回写到主内存:

lock指令的解释:

1、会将当前处理器缓存行的数据立即写回到系统主内存。

2、通过MESI协议,这个写回内存的操作会引起在其他CPU里缓存了该内存地址的数据无效。

3、提供内存屏障功能,使lock前后指令不能重排序。

指令重排序和内存屏障。

并发编程三大特性:可见性、有序性、原子性。

volatile保证可见性与有序性,但是不保证原子性,synchronized可以保证原子性。

指令重排序:在不影响单线程程序执行结果的前提下,计算机为了最大限度的发挥机器性能, 会对机器指令重排序优化。

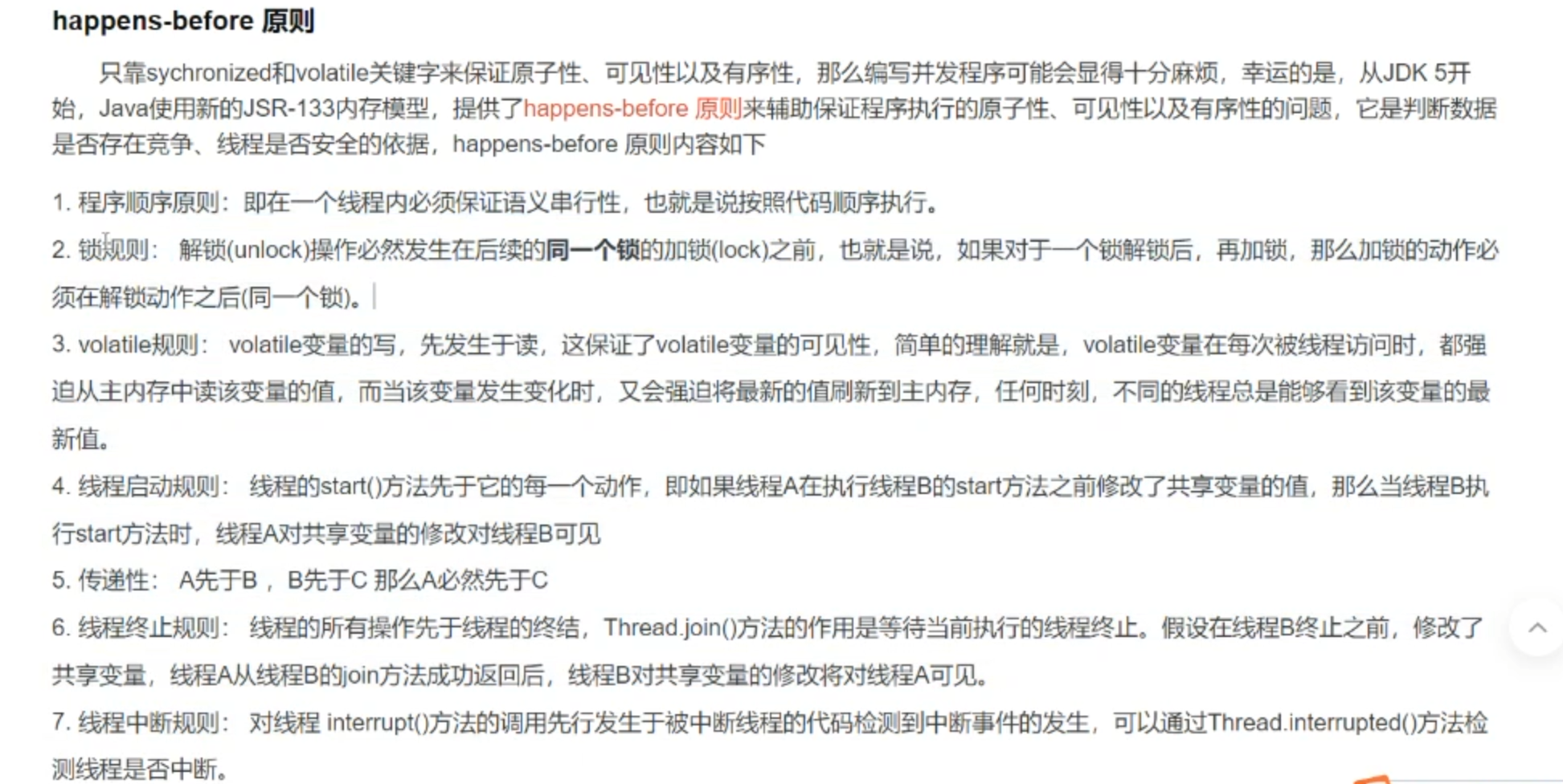

重排序遵循的原则:as-if-serial与happens-before原则。

as-if-serial:

不管怎么重排序,单线程程序的执行结果不能被改变。所以编译器和处理器不会对数据依赖关系的操作做重排序。

happens-before原则:

浙公网安备 33010602011771号

浙公网安备 33010602011771号