数字电源之——ADC采样保持窗口时间

2021-09-05 15:41 斑鸠,一生。 阅读(5741) 评论(0) 收藏 举报本文分析数字电源ADC采样时间的原理、误差来源、改善方法。

1、ADC采样原理

根据ADC采样,外部电路的不同。模拟信号的速度和效率的不同。

一些电路需要更长的时间传送到ADC的采样电容。

2、ADC采样保持窗口时间长短对ADC采样效果的影响

数字控制器采样时间过长,导致控制环路延时很长,影响闭环控制效果和响应。

采样时间过短,导致采样电容的充电时间不够,采到的电压低于实际电压值。

3、数字控制器的ADC模块的等效电路

对于DSP28035来说,ADCIN引脚可以用RC电路模拟表示。

采样电容Ch为1.6pF;

引脚寄生电容Cp为5pF;

开关电阻Ron为3.4k欧;

那么,Ron与Ch组成的电路的时间常数为5.44ns

Rs为上级电路信号源的输出电阻。如果Rs为50欧的话,那么,时间常数为0.25ns。

因此,电压采样电路,常常通过使用电压跟随器电路来降低输出电阻。

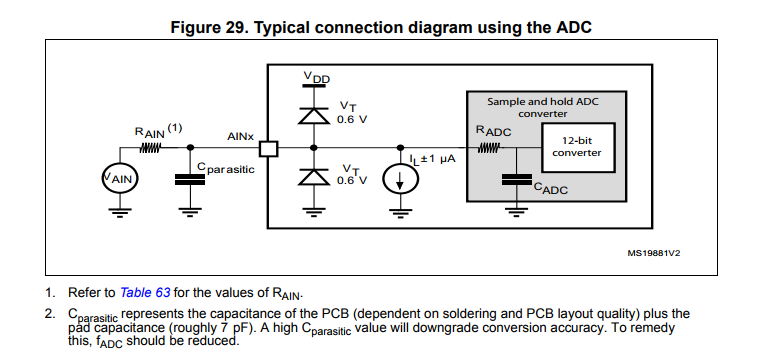

对于stm32系列单片机,它的采样电路等效模型为:

根据数据手册,CADC典型值为5pF。CADC比DSP的Ch还大些。该模型与dsp的ADC模型等效电路相似。

对于dsPIC33系列单片机,它的采样电路等效模型为:

数据手册有写,这个电容最大50pF。

因此,外部电阻Rs的大小,直接关系到数字控制器的采样窗口时间。后文,有详细的推导。

4、RC时间常数与Uc电压的关系

时间常数表示过渡反应的时间过程的常数。指该物理量从最大值衰减到最大值的1/e所需要的时间。

当t = RC时, Uc(t) = 0.63Uc_max;

当t = 2RC时,Uc(t) = 0.86Uc_max;

当t = 3RC时,Uc(t) = 0.95Uc_max;

当t = 4RC时,Uc(t) = 0.98Uc_max;

当t = 5RC时,Uc(t) = 0.99Uc_max;

可见,经过3~5个RC后,充电过程基本结束。

5、数字控制器如何设定ADC采样窗口时间。

如果上级电路的Rs电阻足够小的时候,那么窗口采样时间留3~5个Ron与Ch组成的时间常数。

如果上级电路的Rs电阻很大,那么ADCIN引脚的Cp上升时间很长,那么窗口时间还得加上3~5个由Rs与Cp组成的时间常数。(一般来说:正常运行的电路,Cp上的电压应该不会突变,那么Cp上的初始值就不是零,在这里的窗口时间就不用留3~5个时间常数,仅仅考虑Ron与Ch组成的窗口时间就可以了)

对于dsPIC的ADC输入等效模型,窗口时间留3~5个Rs与C组成的时间常数就可以啦。

浙公网安备 33010602011771号

浙公网安备 33010602011771号