CSAPP Architechture Lab

知识点

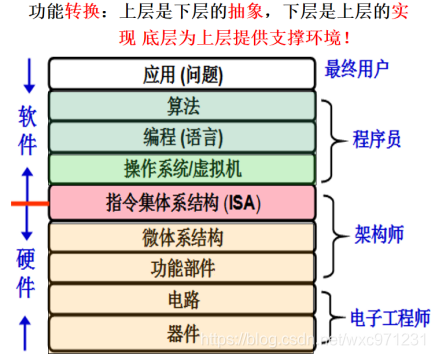

在上一章"程序的机器级表示"中,我们可以知道所谓ISA(指令集体系结构)定义了机器级程序的格式和行为: P113

-

定义了指令的格式(编码方式)

-

定义了处理器状态

-

定义了每条指令对状态的影响

软件设计师和硬件设计师以ISA为规则,分别编写出合法的汇编程序,制造出实现ISA描述的行为的逻辑电路

在上一章"程序的机器级表示"是在我们的图中ISA上层;在这章"处理器体系结构",则位于ISA下层,其重点描述了:

-

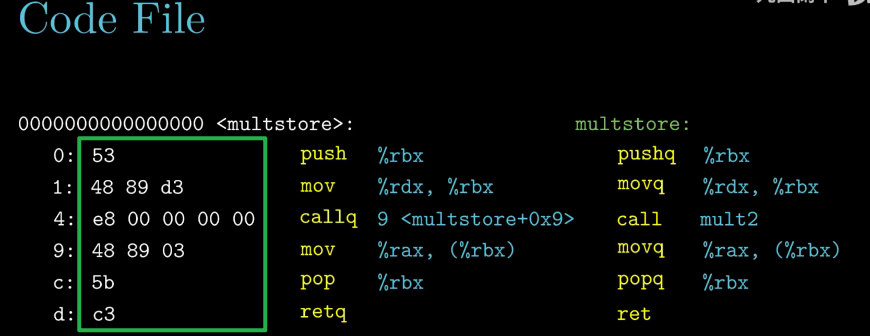

ISA定义的每条指令如何进行独一无二的编码 P245

from bilibili 九曲阑干 可以看到绿框中,这些数字是对指令编码后的16进制表示

-

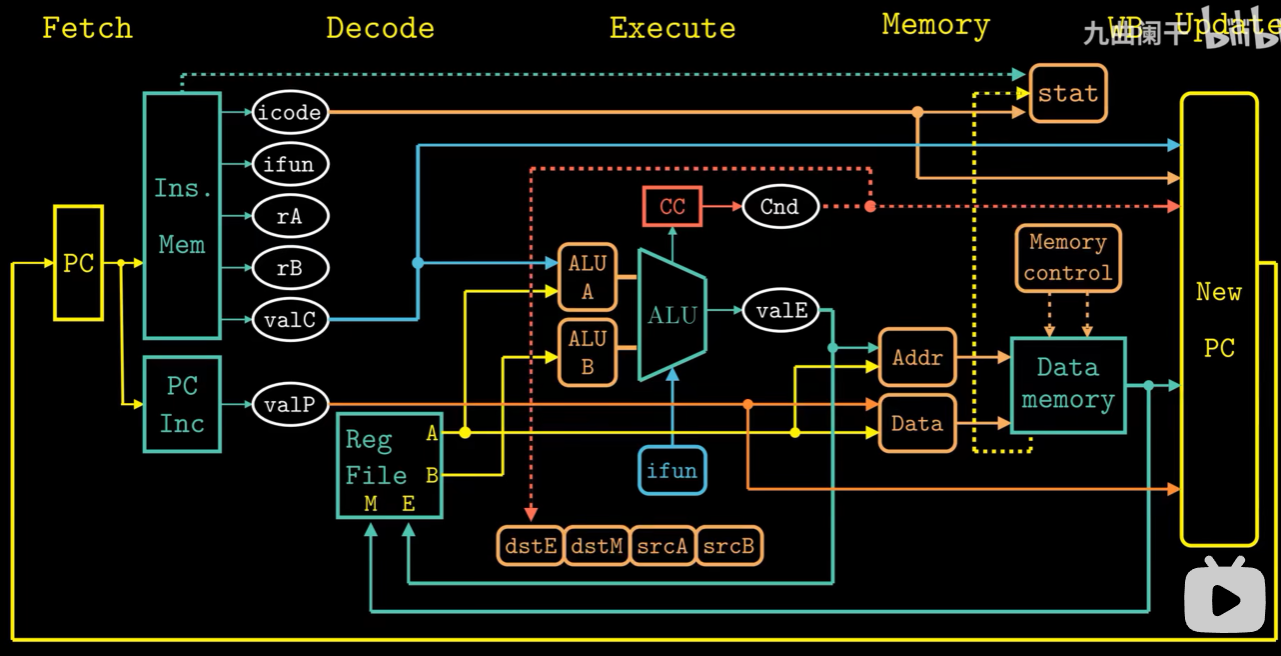

一条指令是如何分为

取指,译码,执行,访存,写回,更新PC这六个阶段,同时利用流水线技术对这六个阶段进行并行执行

时钟:我们需要时序电路,即有状态并且在这个状态上进行计算的系统,我们引入了按位存储信息的设备。存储设备都是由同一个时钟控制的,时钟是一个周期信号,决定什么时候要把新值加载到设备中,即决定什么时候状态进行改变。

-

硬件寄存器:即时钟寄存器(register),就是我们上面提及到的计算机中的一种按位存储信息的设备。

-

程序寄存器:程序寄存器就单单指CPU中寻址使用的寄存器

比如%rdi,%rdx,%rax这些寄存器,这些所有的程序寄存器组合到一起就是寄存器堆也叫寄存器文件(register file)。

我们一般是在"程序的机器级表示"中常常叫的是程序寄存器,而在"处理器体系结构"我们常常加的是寄存器文件

试想一下,为何上述一个指令的全阶段(取指,译码,执行,访存,写回,更新PC)只能顺序执行?

我能不能就按照这个结构进行指令全阶段的并行执行?

不能!因为各个阶段的执行的结果都还只在电路上,只有最后访存,写回,更新PC这些阶段当是时钟高频信号来了,才写到硬件寄存器中。

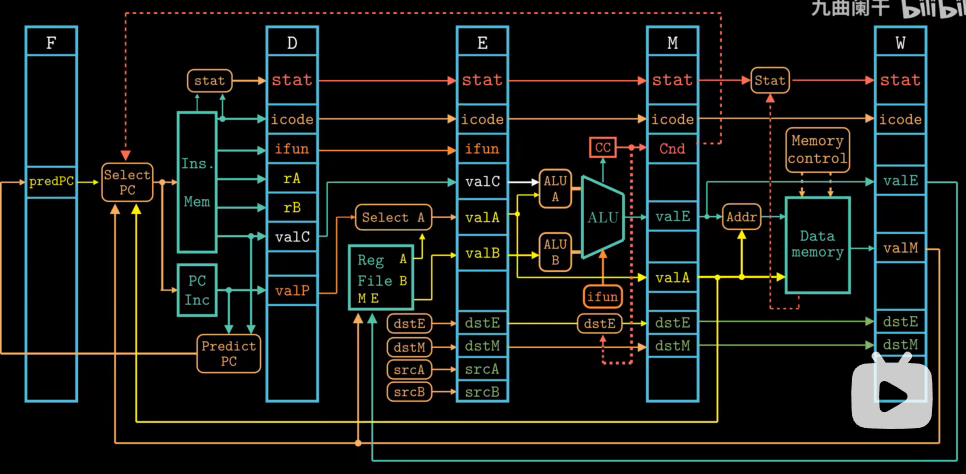

我们为每一个阶段加上硬件寄存器,保存每一个阶段执行的结果

这样,当第n条指令的取指阶段完成后,时钟高频信号来了,将信息保存在硬件寄存器中,这是第n条指令译码阶段的输入

然后便可以执行第n+1条指令的取指阶段,完成后时钟高频信号来了,将信息保存在硬件寄存器中,这是第n+1条指令译码阶段的输入。这个时候我们也已经完成了第n条指令译码阶段。

浙公网安备 33010602011771号

浙公网安备 33010602011771号