主存储器及其组织实现

写在前面:

由于存储器这一章知识十分繁多,笔记本写不下了

在这里记录:

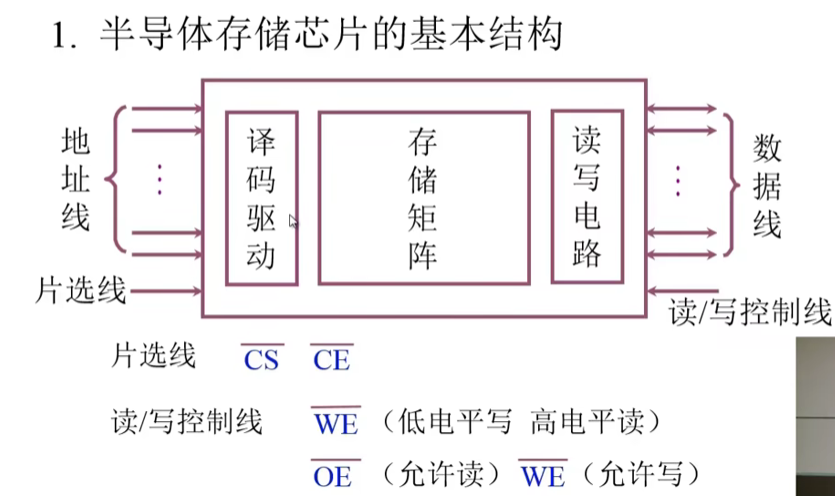

1.半导体存储器芯片的一般结构

2.MOS写常态存储器芯片

3.主存储器以及其容量,带宽扩展组织

的详细内容

主要参考资料是哈工大刘老师的视频

与本校江师大的计算机组成原理教材

半导体存储器芯片:

我们知道:

半导体存储器可以适用于高速缓存,主存,控存的功能

所以要知道主存储器的组织就要了解半导体存储器

而半导体存储器是通过一定数量的半导体存储器芯片组成的

后面介绍的MOS写常态存储器芯片(包括SRAM和DRA)都是半导体存储器的功能细化和分类

芯片的组成结构:

解释:

的含义是啥?

的含义是啥?

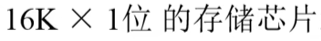

表示这块芯片有16K的存储单元,每个存储单元有1位

片选线是看选不选择当前芯片的信号线

有两种写法:

1. (片选端),低电平有效

(片选端),低电平有效

2. (使能端),低电平有效

(使能端),低电平有效

芯片内部的地址译码:

1.单译码方式(线选法):

解释:

简单易懂的方法,只通过行地址译码确定要读写的某行

这一行上的全部数据(位)被选中

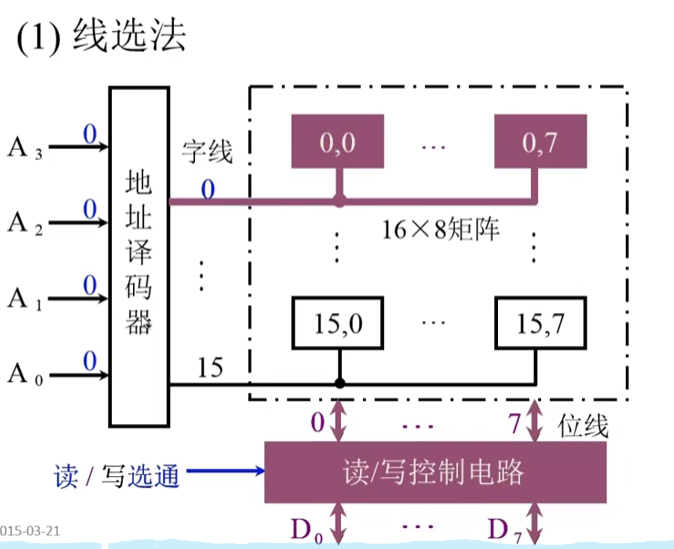

2.双译码方式(重合法):

解释:

如图只有行和列都被选中的数据(位)才真正被选中

用重合法如何确定数据的位数为多少?即存储字长为多少?

是根据一个位选信号选通多少根列线,对应同行记忆元存储信息

就有多少位存储字长

本例中只有1位存储字长

MOS写常态存储器芯片

MOS写常态存储器是一种随机读写的易失性半导体存储器,

即需要电源才能工作,只要电源正常,就能长期稳定的保存信息,

否则断电将会失去保存信息

根据读破坏性可分静态的(SRAM)和动态的(DRAM)

SRAM:

下面将对上述问题进行详细讲解:

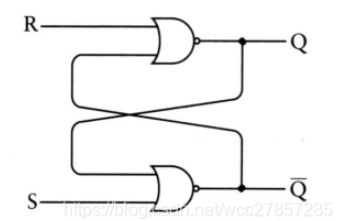

1.SRAM保存0和1的原理是什么?

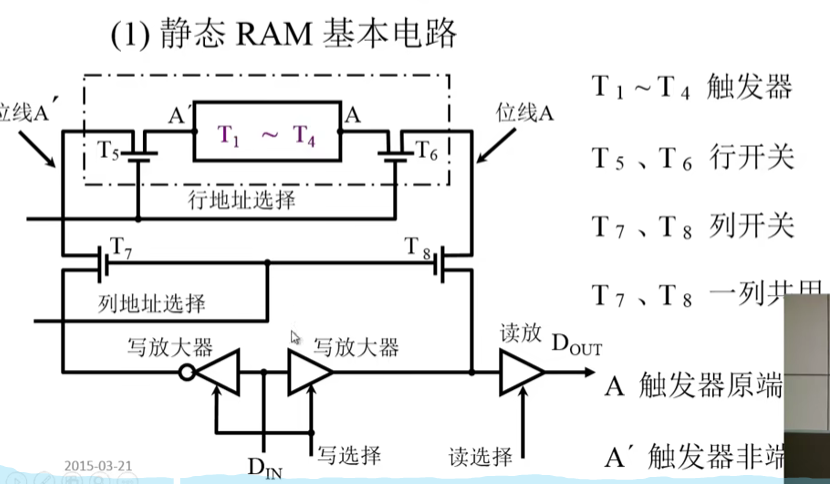

2.SRAM基本单元电路的构成

解释:

1.

A’类似于 ,A类似于

,A类似于

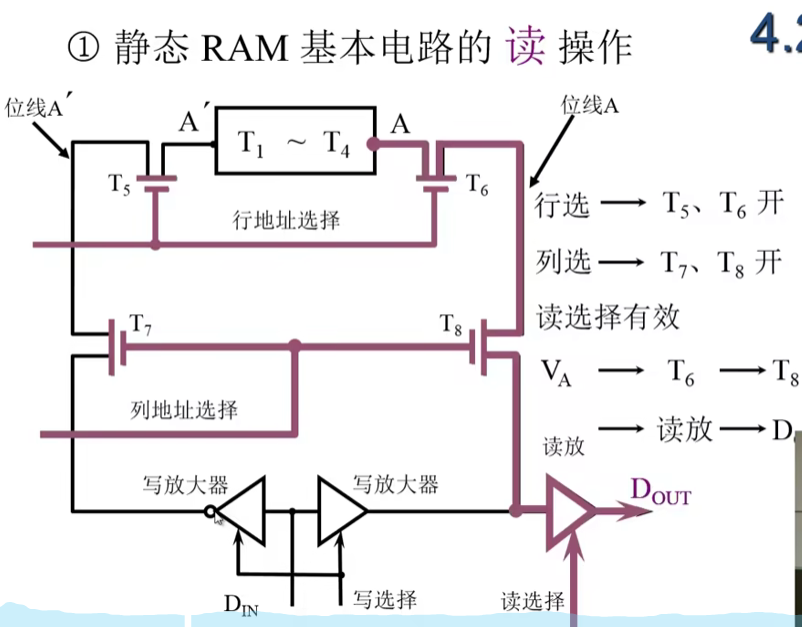

3.读操作:

解释:

其实这个时候A’也在输出信号,但是其遇到了

信号过不去了

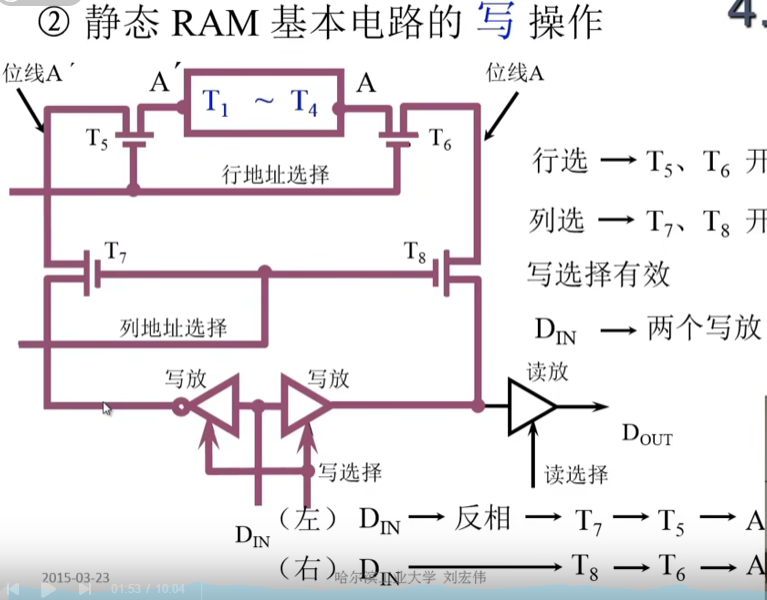

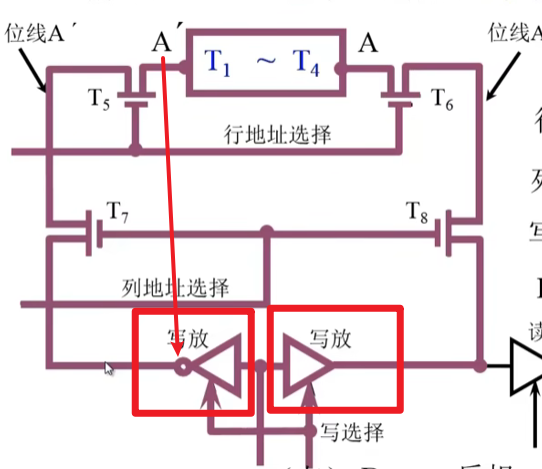

3.写操作:

解释:

可以看出这里经过了取反,即使两端同时在写,

也是写的相同信号,没有问题

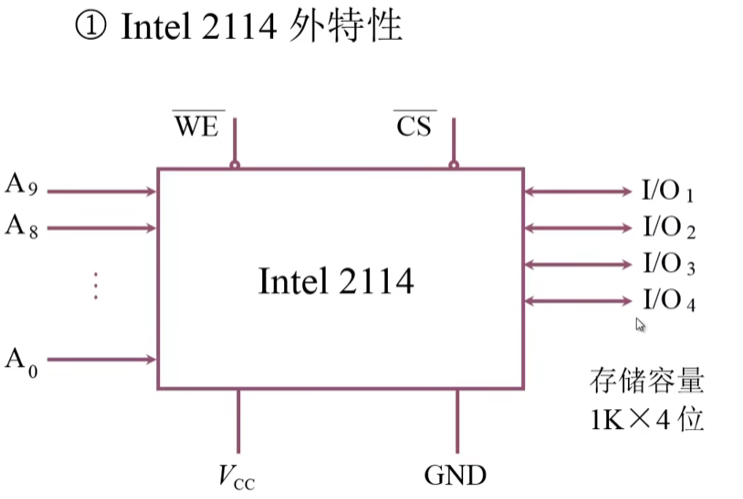

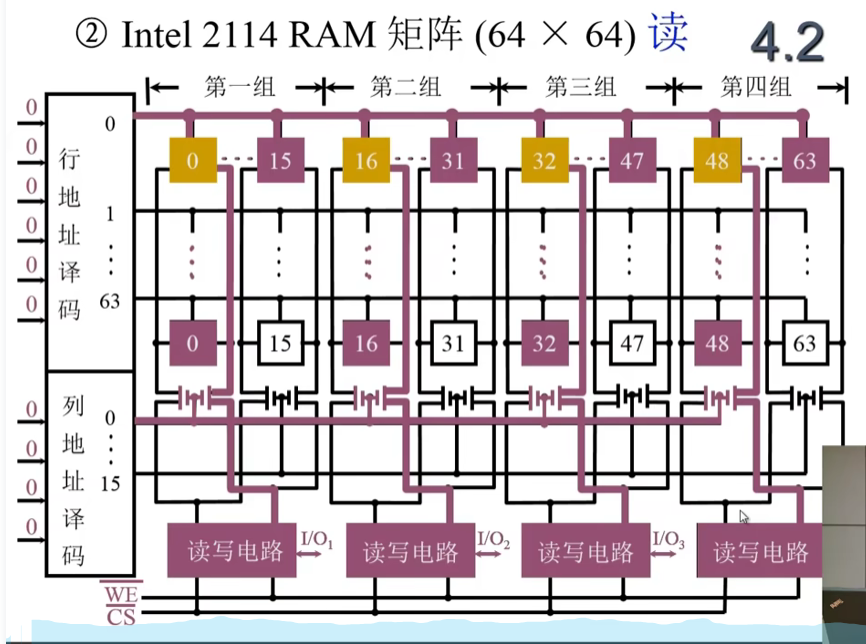

4.经典芯片结构

从SRAM的读写方法可以看出:

SRAM芯片的译码方式必须为重合法

那么如何设计可以使得一次列选,选中4位?

(因为输出/入的数据要四位)

解决:

已知:此芯片为1K X 4位,即2^10个存储单元,每个存储单元有4位

即有2^12个记忆元

即可以分成64*64的矩阵

行地址译码的范围为0~63,要6根地址线,

还剩下4根地址线,给列地址译码,其范围为0~15

可以将64列 ,分成4组 ,每组16列

有16种列选信号,

每一个列选信号控制了每一组中的一列

DRAM:

1.保存0和1的原理是什么?

电容,通过电容有无电来保存状态

2.基本单元电路的构成:

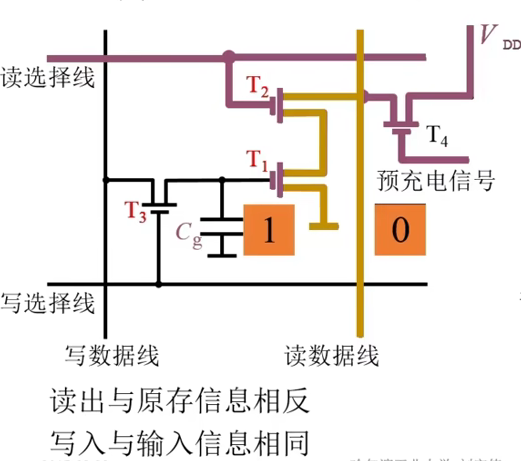

1.三管记忆元DRAM

解释:

1.当要读出时,预充信号发出,读选择线导通,T4,T2导通

Vdd放电,读数据线上有电

1.如果Cg(电容)上有电,则放电,T1导通

此时读数据线上通过T1导通的线一直放电,导致最终是0

即Cg上有电为0

2.如果Cg上无电,最终读数据线上为1

即Cg上无点为1

所以

2.当要写入,很简单

写数据线上为1,则Cg有电

写数据线上为0,则Cg无电

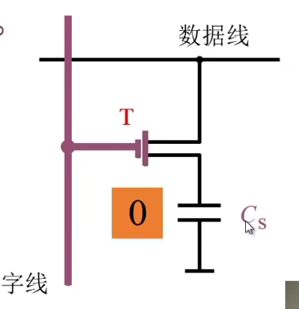

2.单管记忆元DRAM:

解释:

字线是选择线,当字线被选中

T导通,Cs可以根据自身有无电进行读写

1.当Cs没电,数据线上为0

2.当Cs有点,数据线上为1

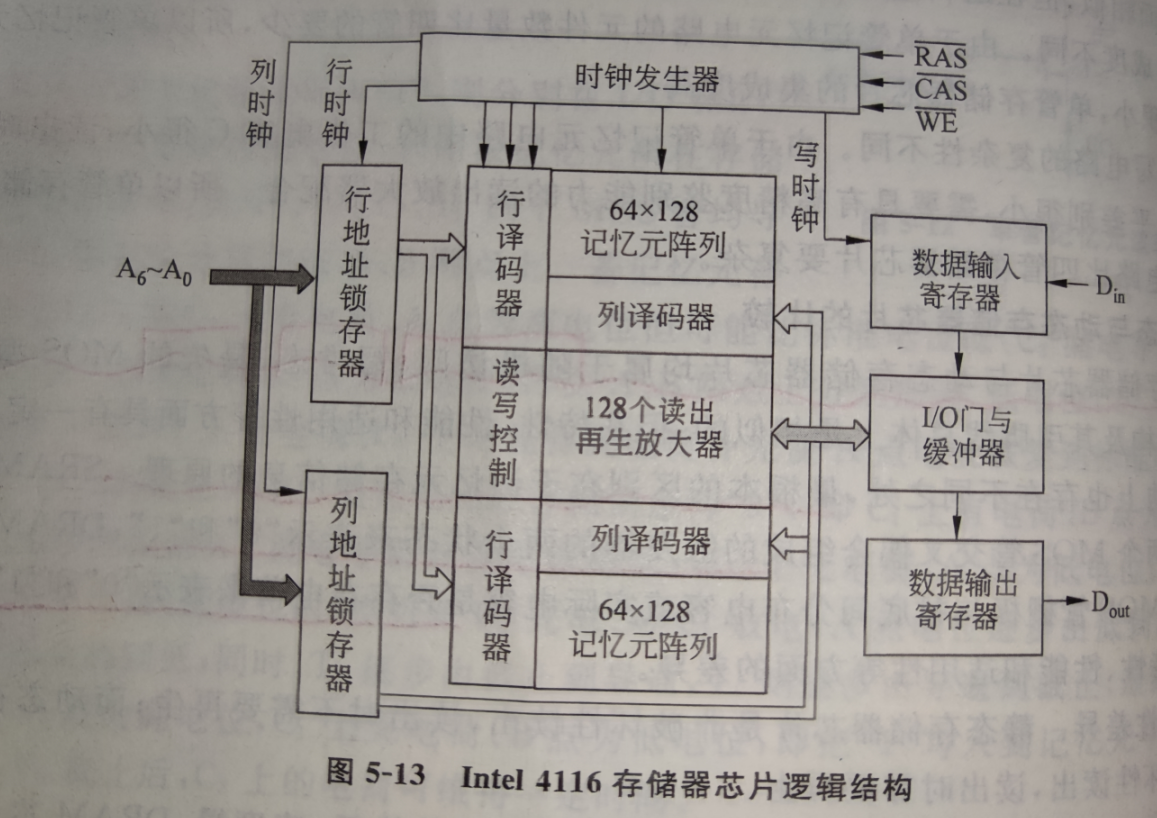

3.典型芯片结构:

解释:

1.这是16K X 1位 的单管DRAM

以重合法来译址,那么其是个128 x 128的矩阵

2.16K,本来是要14根地址线的,但是这里只给出7根地址线

这是因为其想要地址线分两次输入

每一次可以选择2^7=128个字选信号

如果不是这么做,想要即选出128行中某一行,

同时选出128列中的某一列

达到选中1位的效果是很难的

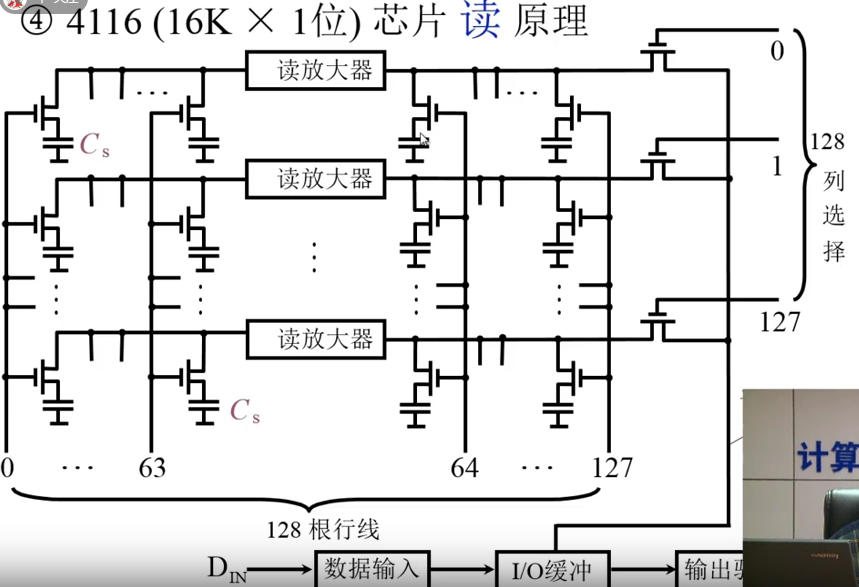

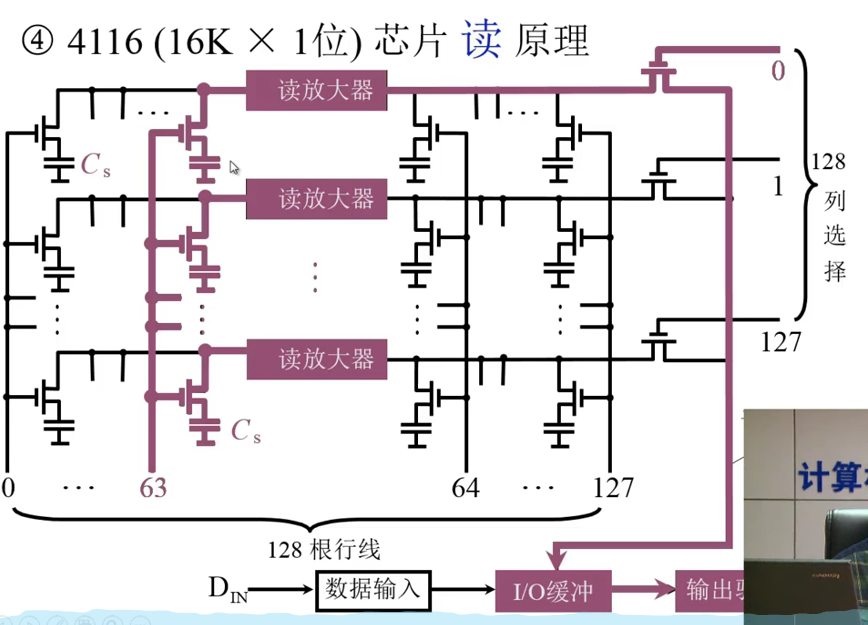

4.读,写操作:

这里的读放大器是一个跷跷板电路

即读放大器有两端,如果某一段为1,则另一端为0

通过模拟很容易得到如何操作

通过这个电路:

读:要分在读放大器左侧还是右侧

在左侧:电容有电为0,电容无电为1

在右侧:电容有电为1,电容无电为0

写:同理

5.DRAM为啥要刷新,如果刷新:

为何要刷新?

因为电容容易漏电

如何刷新?

首先,刷新与行地址有关,我们是一行一行刷新

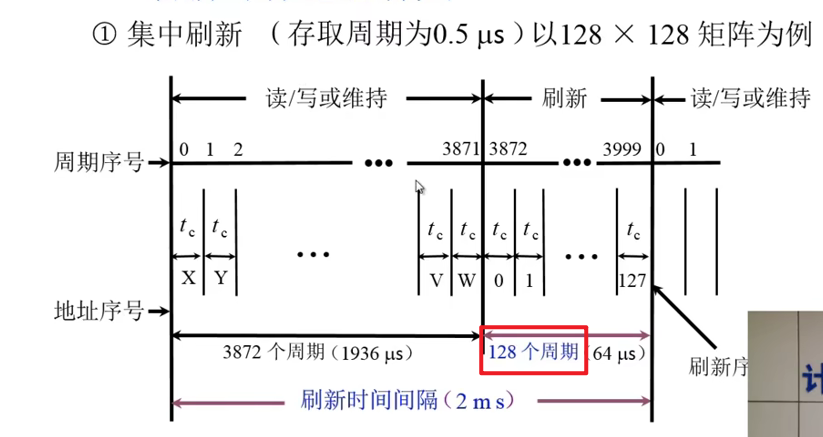

1.集中式刷新

解释:

128行都要刷新到,而且是集中一个时间刷新

在刷新的时候被称为死区,IO与CPU无法访问

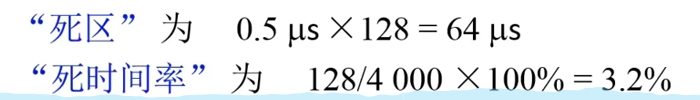

2.分散式刷新:

解释:

为啥这里存取周期从上面的0.5us变成了1us了?

因为他将原本一个只要存取操作的周期

变成了既要存取,在存取完后还要刷新算作一个周期

于是周期时间翻倍

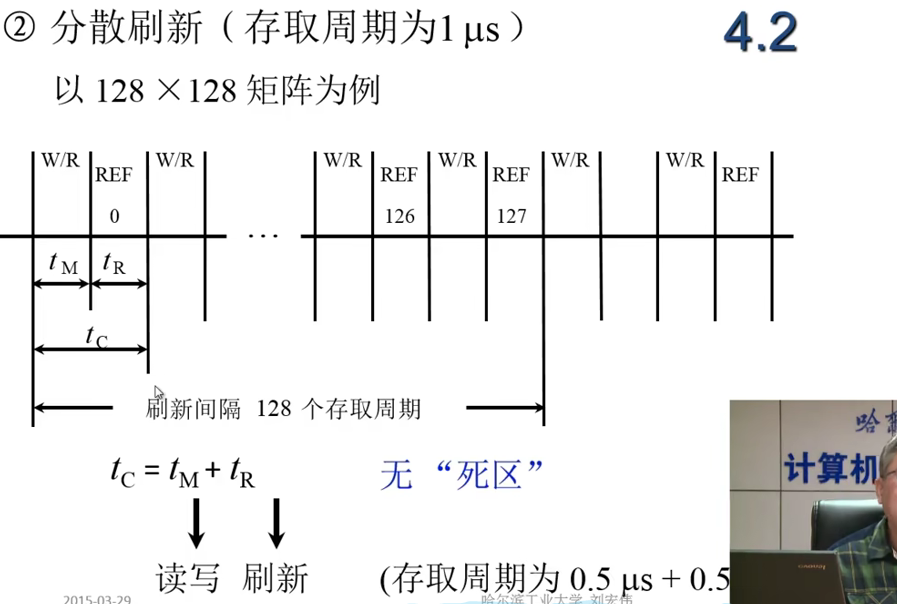

3.异步刷新:

解释:

将

因为有128行,所以我将2ms分成128份

每份有15.6us

对于整体来说为分散刷新,对于每份来说为集中刷新

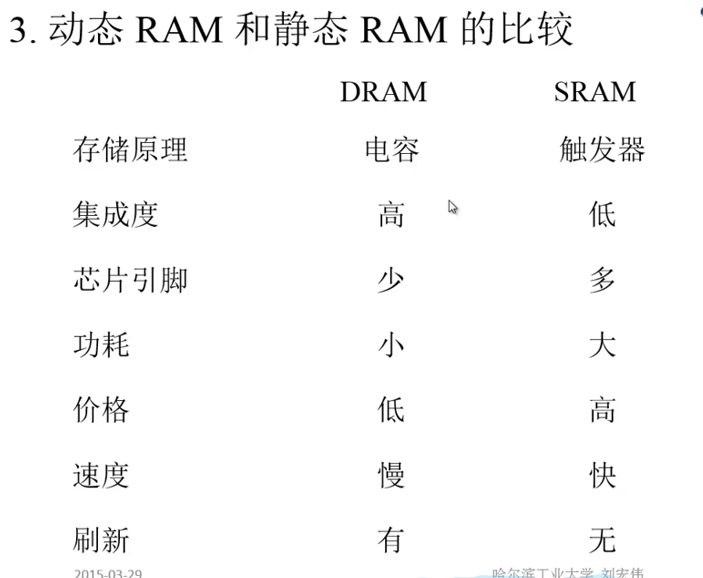

4.SRAM与DRAM的区别

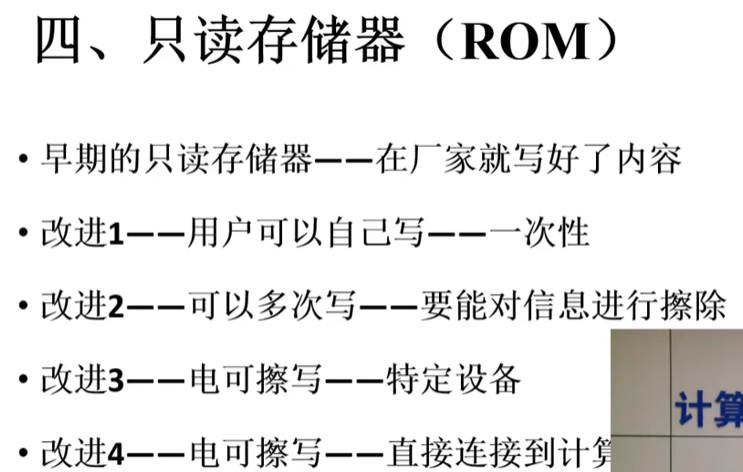

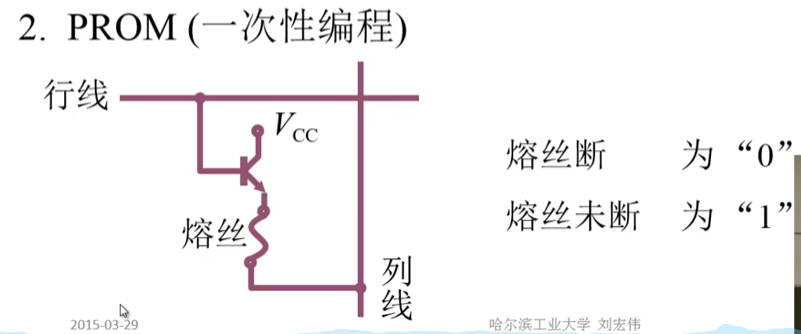

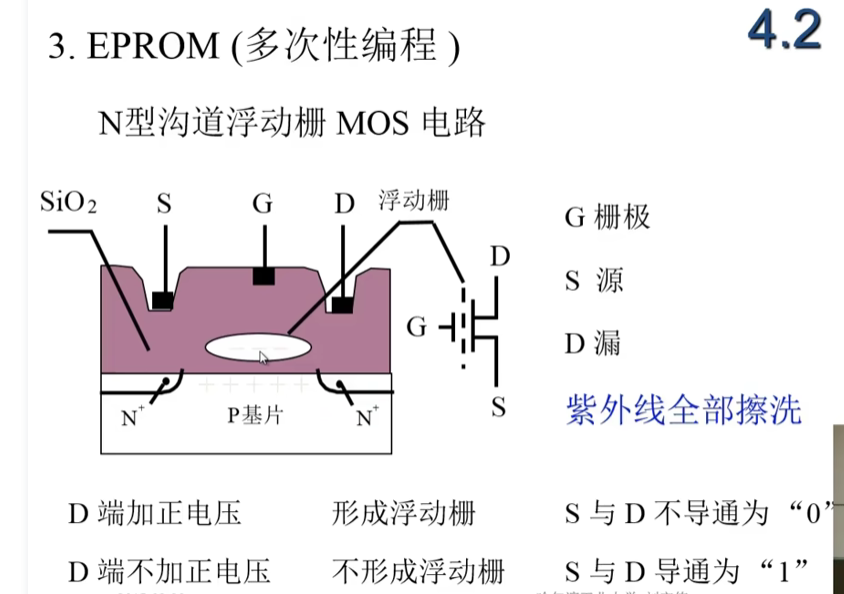

只读与混合MOS存储器:

写常态 MOS 型随机存储器芯片是易失性的,实现非易失性是应用必然要求。

但为实现非易失性,只读存储器芯带来了一个新的问题一不能在线写或不能重复写。

为使半导体存储器既具有写常态和非易失性两重特性,便出现了MOS型混合存储器芯片。

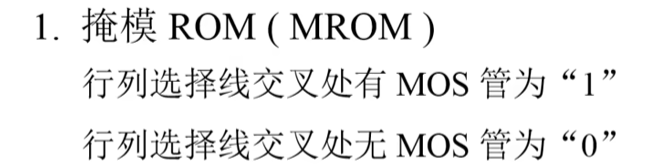

早期:

解释:

商家已经作好的,不能进行更改其中的信息

其信息保存为通过行列选择线交叉处是否有MOS管来判断信息为何

改进1:

改进2:

改进3:

改进4:

主存储器及其组织

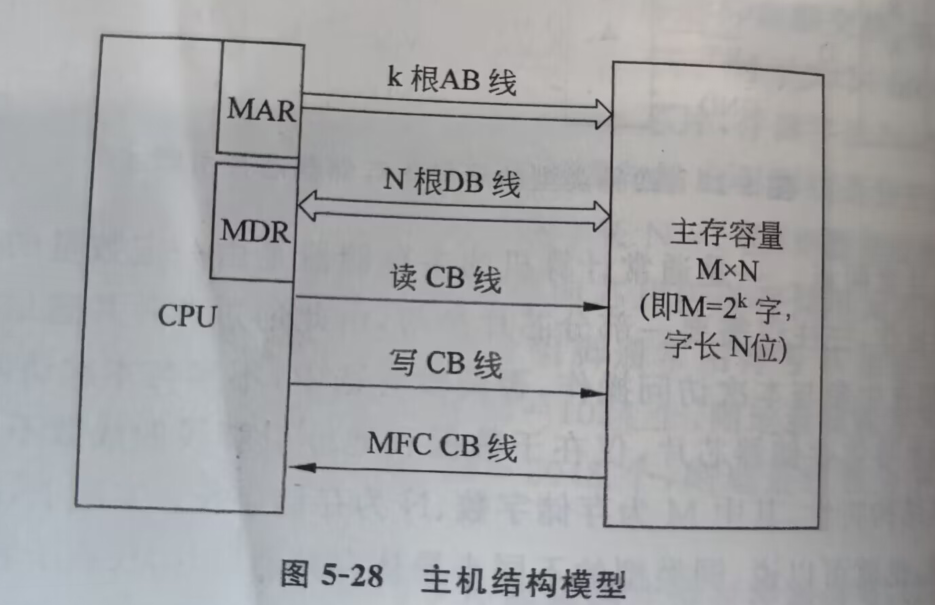

主存储器的组成结构和主机结构模型:

解释:

CB线是控制线的意思

MFC是应答信号(读和写分同步和异步两种方式,只要异步方式要用到MFC)

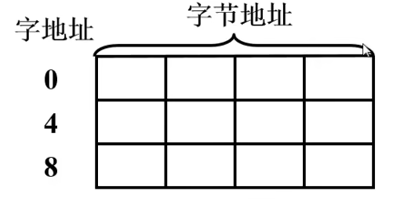

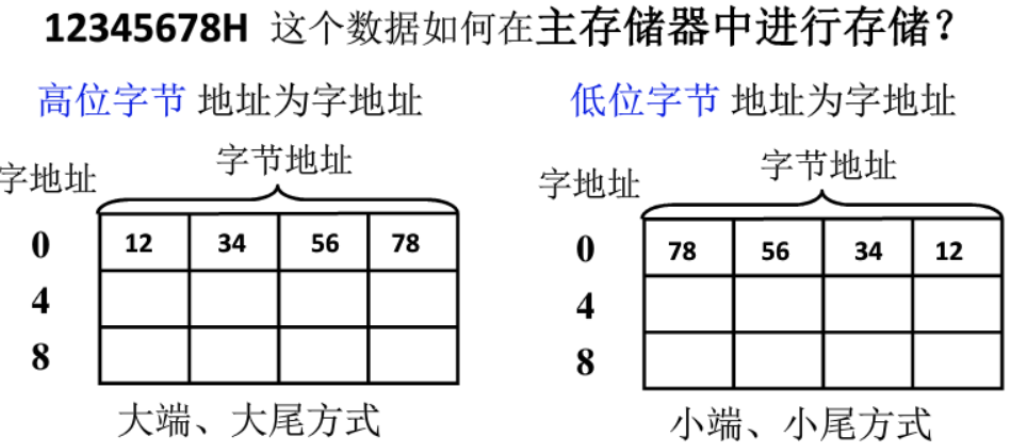

主存储器的数据存放方法:

编址单位:通常把存储单元所包含的二进制位数即存储字长称为编址单元

常用的编址单位有:1.字编址

2.字节编址

1.字编址:

即存储字长==机器字长==一个字有多少位

所谓的字地址是按字编址的结果

假设 这每一行都是存储单元

这每一行都是存储单元

一个存储单元为32位,即存储字长为32位

我们知道一个字节为8bit(即8位)

那么我们说这一个存储单元有32/8=4个字节

即一个字中有4个字节

字地址即:

感性的可以感觉到

感性的可以感觉到

按字寻址:

计算机以此方式寻址时,每一个地址值指向了一个字

一个字里面有任意个字节,那么计算机如何知道其地址指向的到底是字中的第几个字节呢?

这便需要地址线中分出一部分标出其所指的到底是字中的第几个字节:

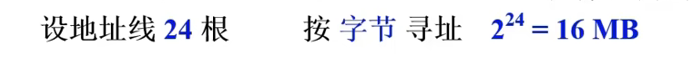

假设存储字节为32位,地址线为24条 ,问如果按字寻址,可以寻找的访问是多少(以W,即字为单位)?

那么一个字有4个字节,要用2条地址线来区分到底是哪一个字节

还剩下22条地址线,则访问范围为 2^22=4MW

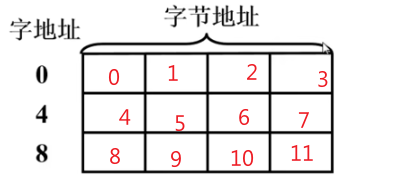

按字节编址:

即存储字长为一个字节

按字节寻址:

一个地址线表示的数(即状态)与一个字节地址相对应。

注意这里的B==8bit,即字节的意思

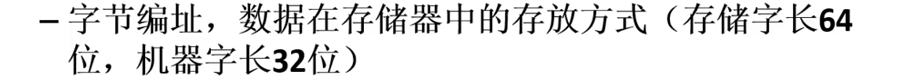

存储方式:

背景:

1.随机存放:

解释:

这样可能会将紧凑的,要一块取出来的数据

放到了不同编址单元上

导致可能一个周期是取...xx00上的双字,但是没取完

还要再花一个周期到...xx08上去取

正如图所示:

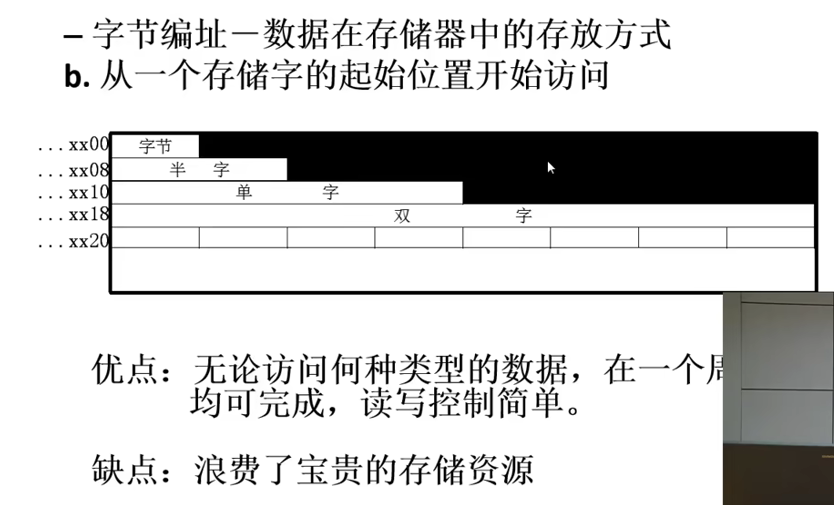

2.字对齐方式:

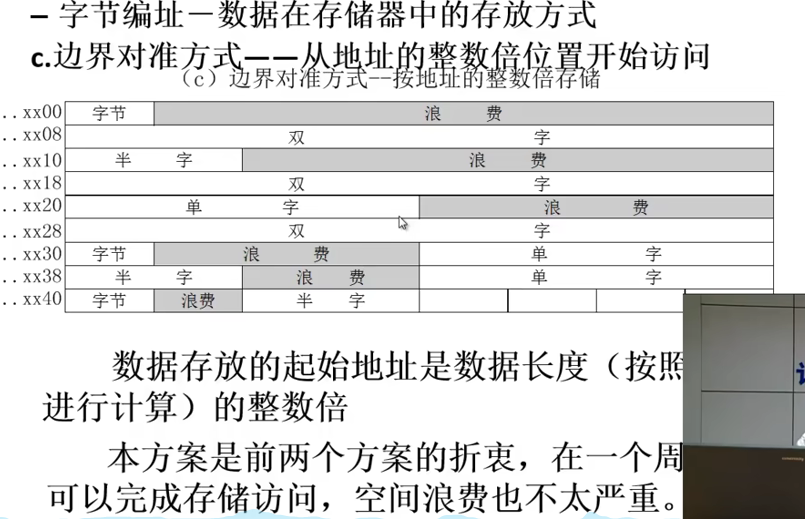

3.边界对齐:

解释:

如这里双字是有64位,即8个字节

那么这个双字保存的地址的最末尾3位必须是000(2进制下)(即8字节的整数倍)

可以保证:

如果想要存储的地址是数据字长的整数倍时,

那么这个这一行就可以保存的下这个数据

而不会保存到下一行去

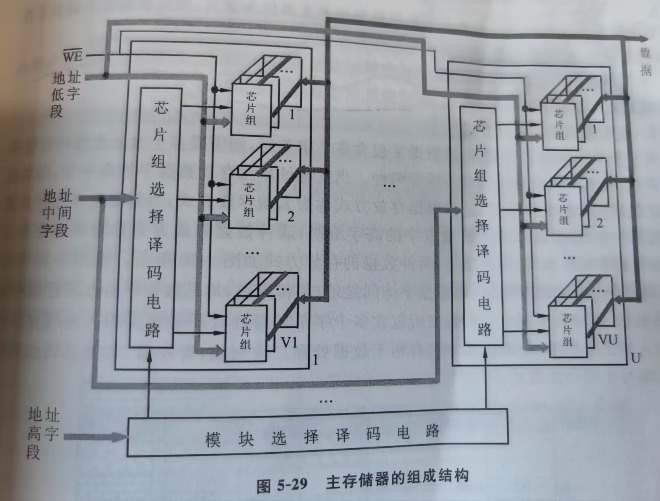

主存储器模块的组织:

存储模块通常需要将一定数量的存储器芯片组织而成

其中需要考虑存储字数(即存储单元个数)和 存储字长的差异

这需要我们来组织和扩展

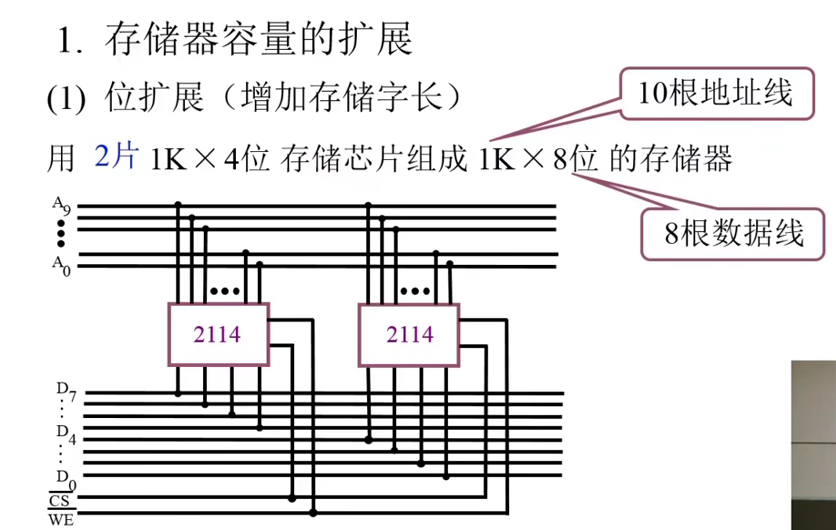

1.当需要扩展存储字长时:位并扩展法(位扩展)

解释:

1. 为片选信号线

为片选信号线

在进行位扩展时,一定要注意让参与位扩展的芯片的片选线连接在一起

保证这些芯片同时被选中

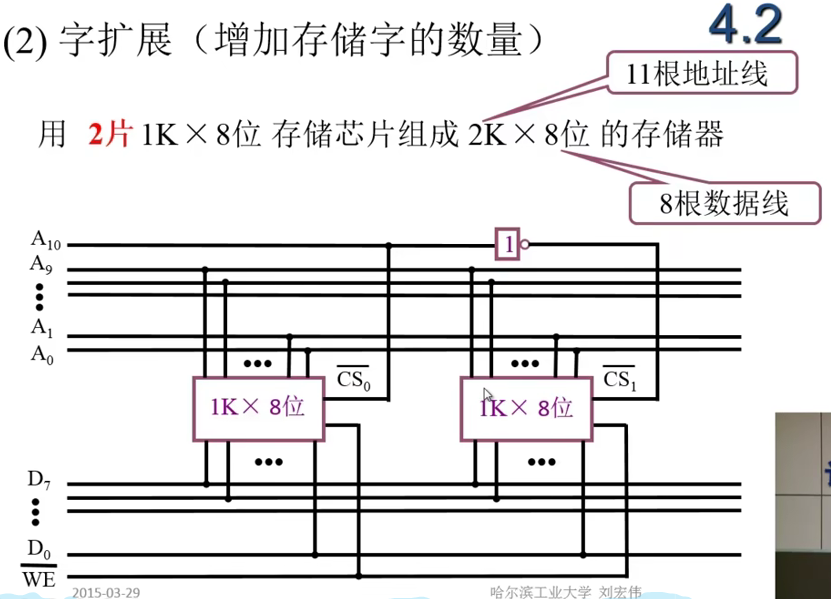

2.当需要扩展存储单元时:字串扩展法(字扩展)

解释:

1.字扩展时注意让参与字扩展的芯片的片选线要分开

即不能同时选中,必要时可以译码器来实现选哪一块芯片

2.在这里2K即有11根地址线,但对于只要其中一块芯片工作10根地址线即可

余下的1根作为判断选择哪一个芯片的逻辑电路连接到芯片的片选线上

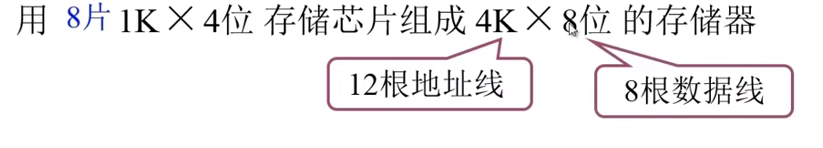

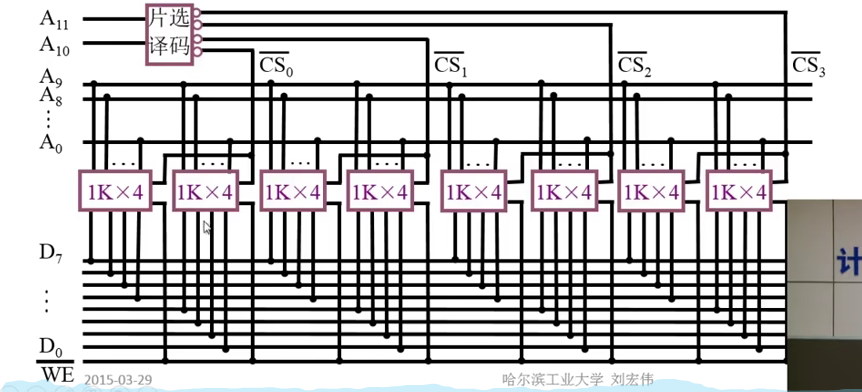

3.当既要扩展字长也要扩展字数的时候:位并字串扩展法

先用2块1k X 4位的芯片组成 1块 1K X 8位的芯片

让他们的片选线连接在一起

重复上面过程,到有4块 1K X 8位的芯片

每次工作需要选择1块 1K X 8位的芯片

地址线只要10根

余下2根用来做片选逻辑电路

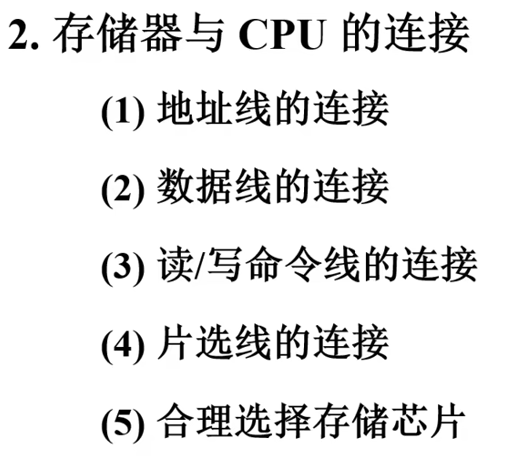

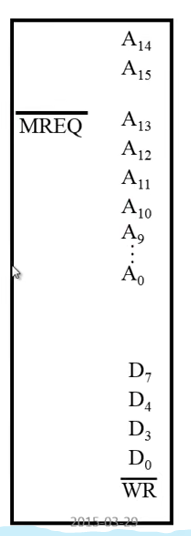

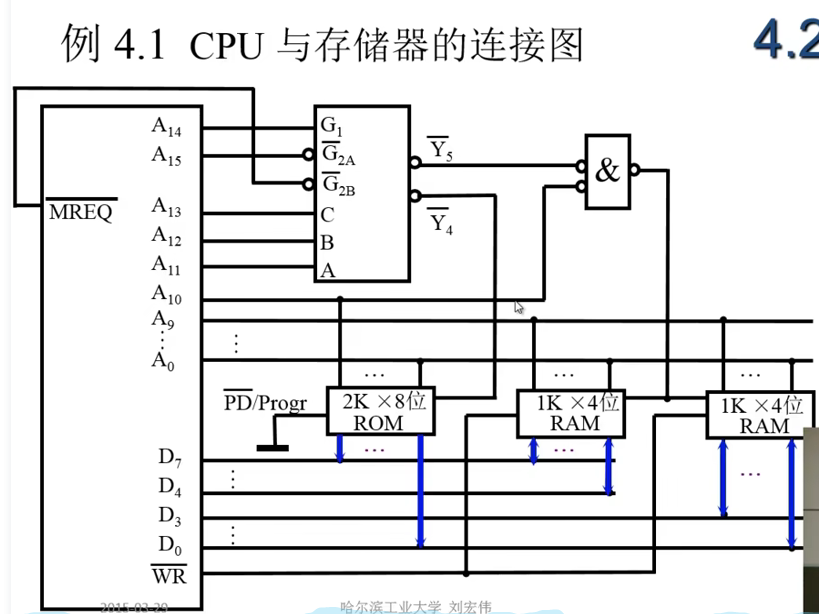

主存储器模块与CPU的连接

这里所几点重要的:

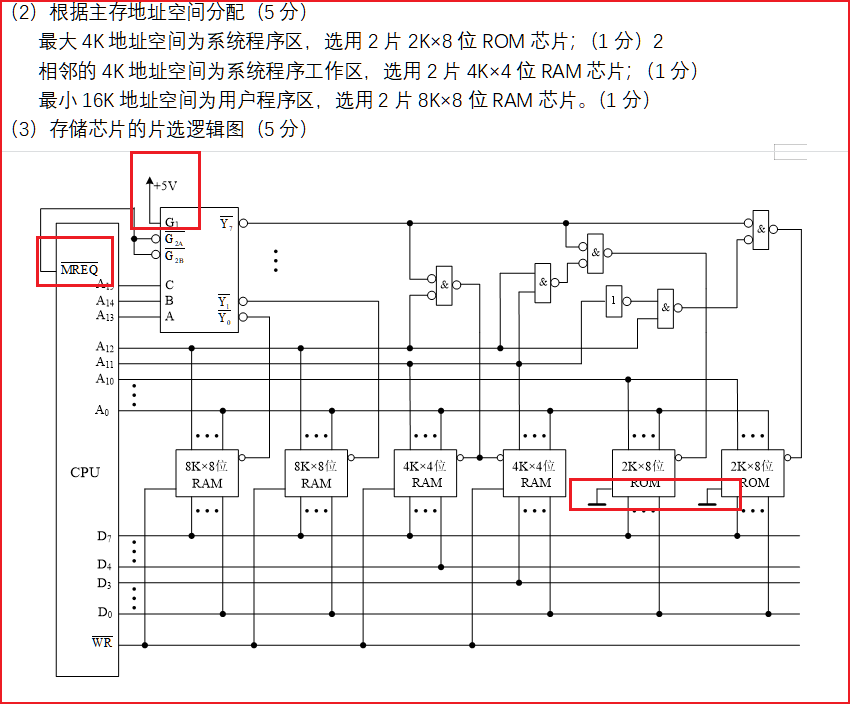

1.CPU上的 一定不能忘记连接,其是决定输出到IO设备还是主存储器的信号线,即是存储器请求

一定不能忘记连接,其是决定输出到IO设备还是主存储器的信号线,即是存储器请求

低电平有效(输出到主存储器),即在连接CPU与主存储器时要将其连接到0这个信息位

其一般是用到片选信息中去

2.ROM为只读存储器,一般其中的内容是不大会变化的

其一般用于系统内存等地方

RAM其一般用于经常要读写的地方,如用户内存等地方

所以ROM的工作端要接地,表示其只读,而不写

3.CPU上的地址线一根也不能浪费

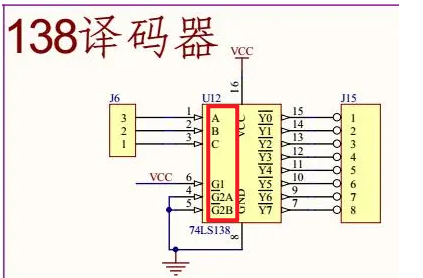

这个还涉及了138译码器:

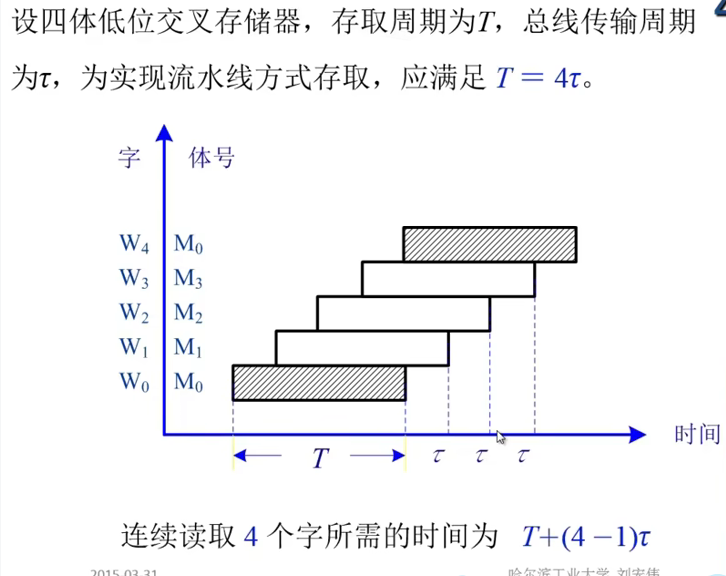

主存储器的带宽扩展:

主存储器为中心的计算机,对主存储器的速度要求很高。

衡量主存储需速度的参数包含延迟和带宽,当采用存储层次方法组织存储器之后,主存储器的延迟得到释放

但带宽又成为主存储器的关键。因此,在设计半导体存储器芯片时,不仅要考虑延迟,还要考虑带宽。

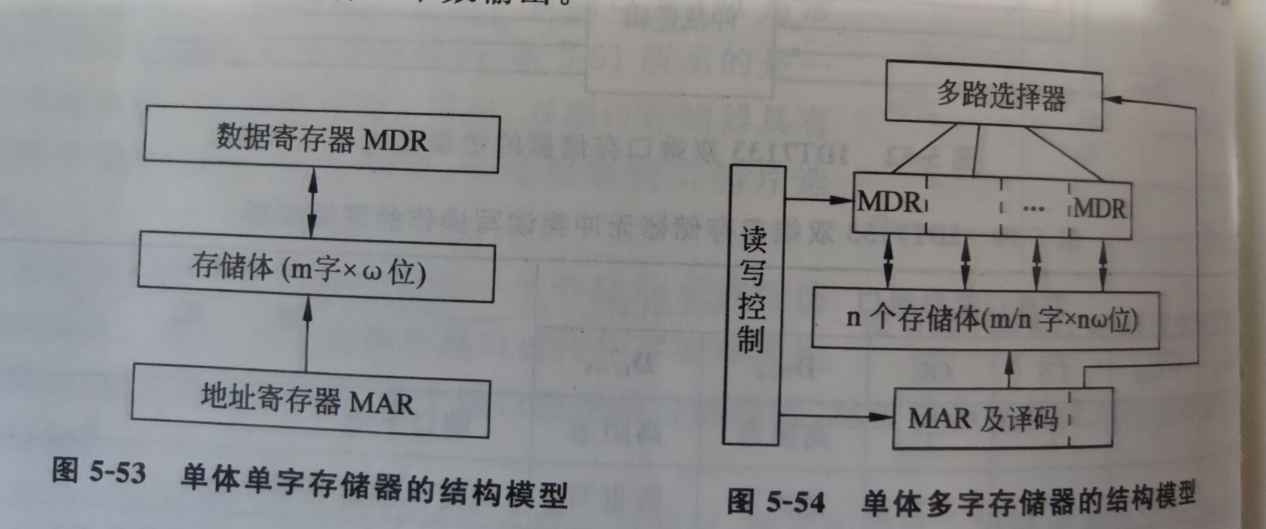

一般主存储器为单体单字,每个存储周期只能访问到一个存储字

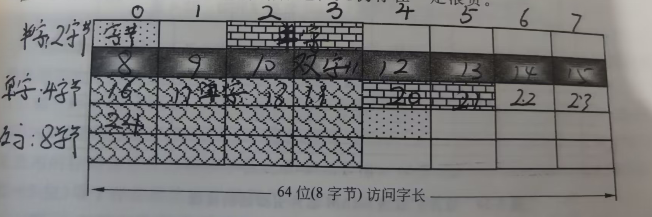

详细看P281,这里只介绍重要的多体并行(多体多字)系统

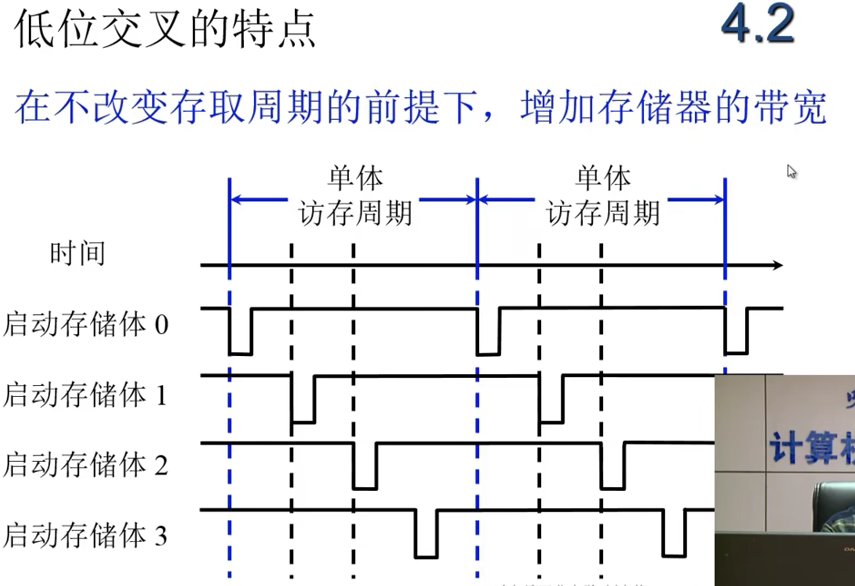

为何称其多体?即其有多个存储体

为何称其并行?即一个周期中本来分为寻址+数据到CPU这两大块时间

当寻址完毕,

数据到CPU这个期间,

存储器空闲,可以利用这个时间立马进行下一次对存储器的操作

这样一次存取周期可以对存储器进行多次存取操作

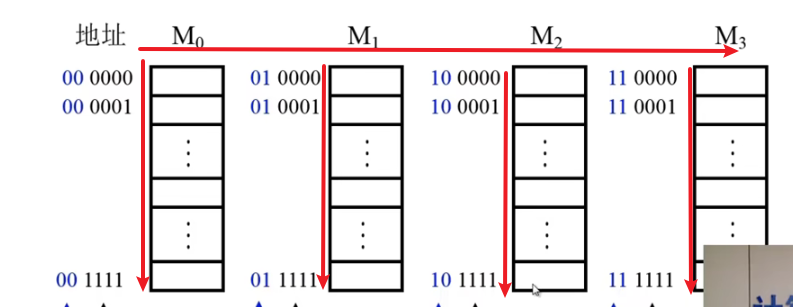

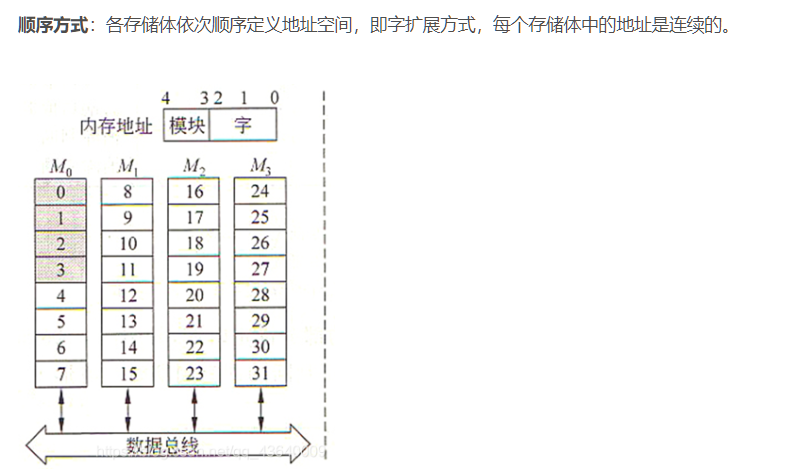

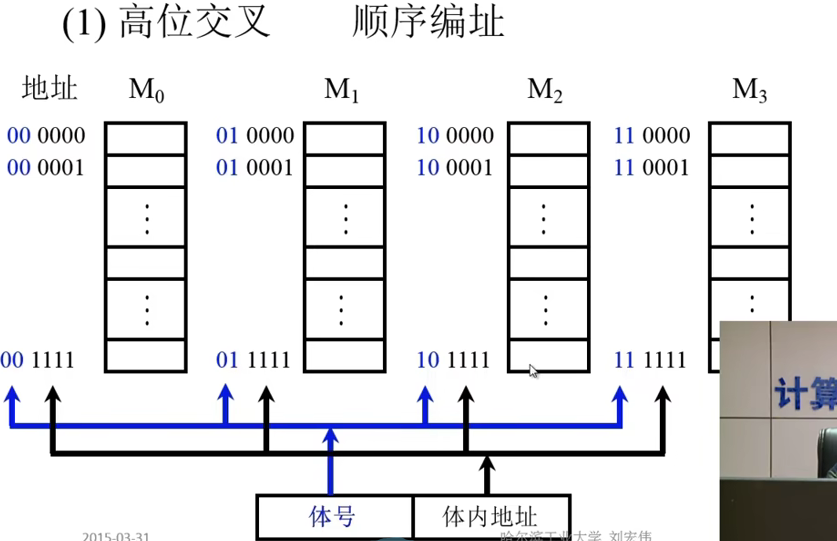

高位块选编址法:

解释:

地址分为体号与体内地址

体号用来区分那个存储体

体内地址用来访问存储体中的信息

地址的高位用来当做体号

这样编码,导致根据局部性原理,数据在存储体中的存取,如图

很可能导致其中一个存储体十分繁忙,其余的存储体很闲

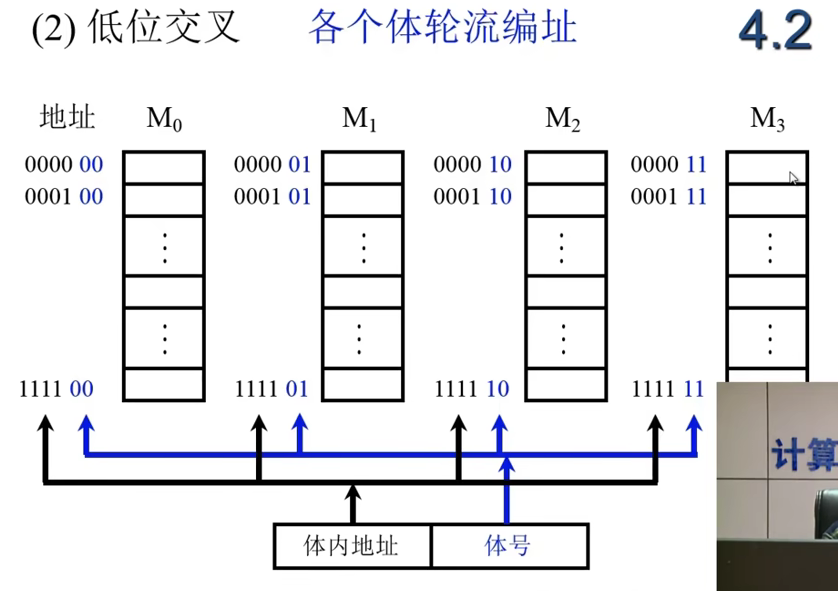

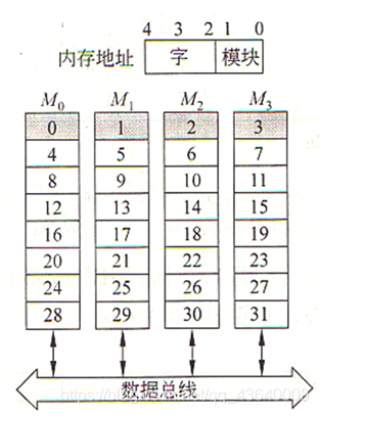

低位块选编址法:

解释:

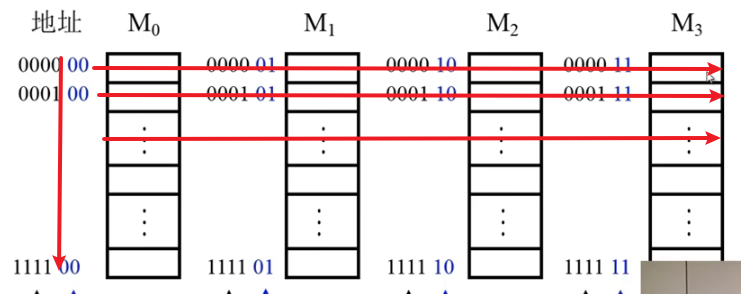

这个与上面的区别是,地址低位用来编码体号

导致数据存取如图:

这样可以达到

每次并行地从不同存储体中取到数据

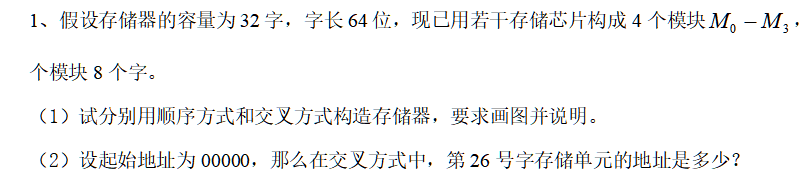

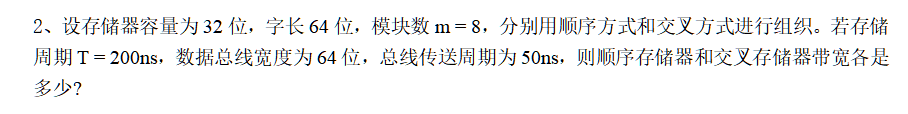

其中的题目:

解:

其实这个顺序方式就是高位交叉(高位块编址)的方式

交叉的方式就是低位交叉的方式

需要注意的是 第xxx号字存储单元,是从第0号开始算的

写题记录:

解:

带宽W=单位时间内传输的二进制位数

顺序方式:

一个存储周期包括传输和保存的时间

则其进行一次存储T=200ns,位数为64位

W=64/(200*1e-9)=3.2*1e8bit/s

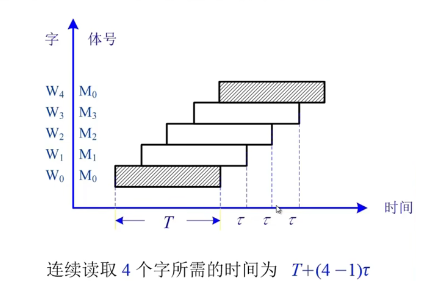

交叉方式:

一开始花t=50ns进行传输,t过后,总线处于空闲状态

可以利用这个空闲时间进行另一个的传输

最终成了如下图:

则开始为T=200ns,以后每经过t完成了一个模块的存储

则总时间TT=T+(m-1)*t

传输的位数为m*64bit

解:

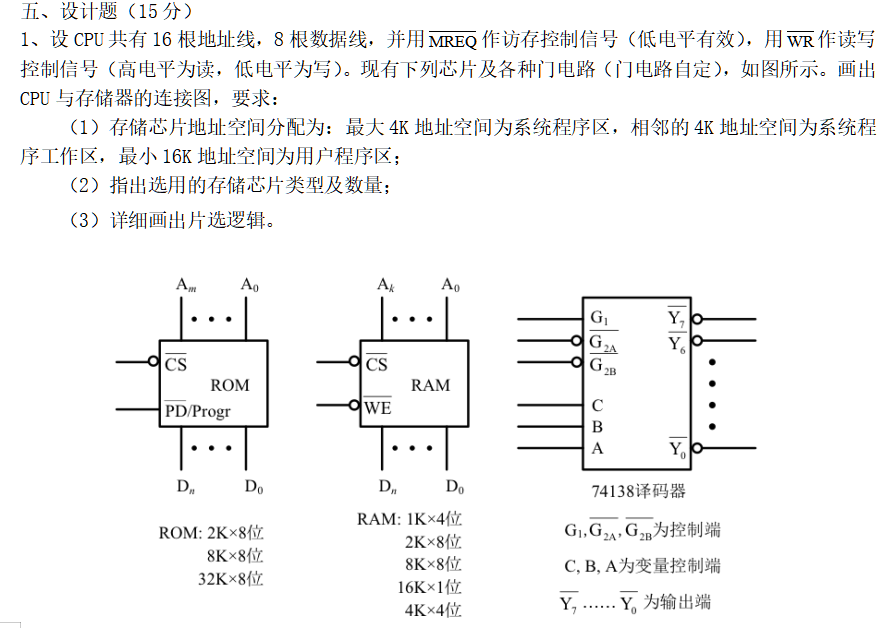

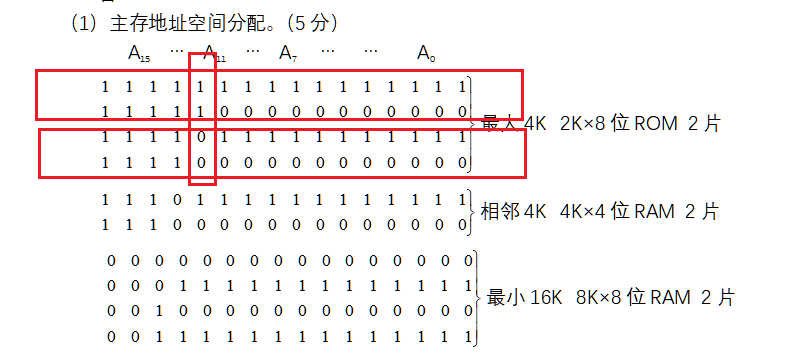

写这种题首先就是要确定地址位空间的配置,这个写好了问题就迎刃而解了

注意这里:

系统程序区为ROM,系统程序工作区为RAM,用户程序为RAM

最大4K即地址二进制数最大,其余同理

注意这里特意写出来是为了将两块芯片进行片选准备的,其余同理

根据地址数的二进制来确定每一个芯片的片选

浙公网安备 33010602011771号

浙公网安备 33010602011771号