CPU

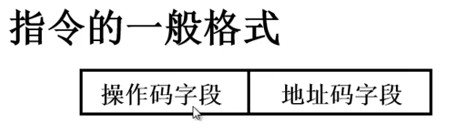

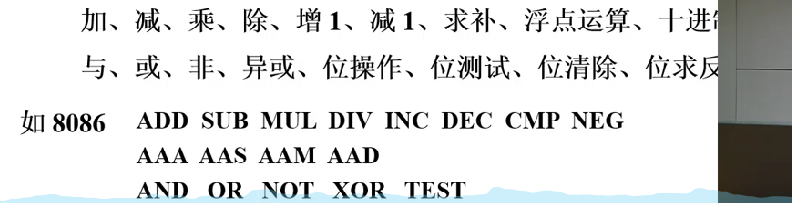

操作码字段:

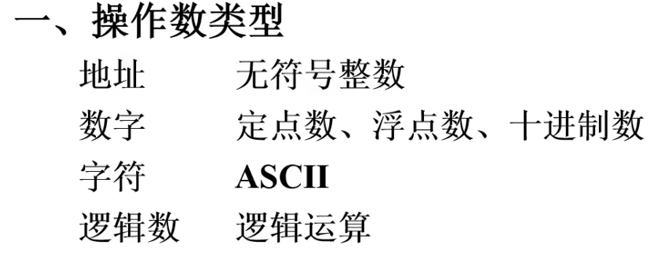

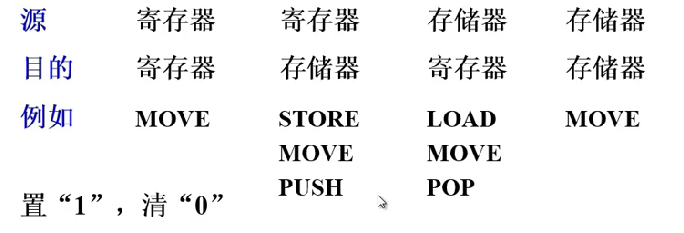

操作数类型:

即指令要处理的数据的类型

这些数据在存储器中的存储方式为何?可以到存储器那章去复习

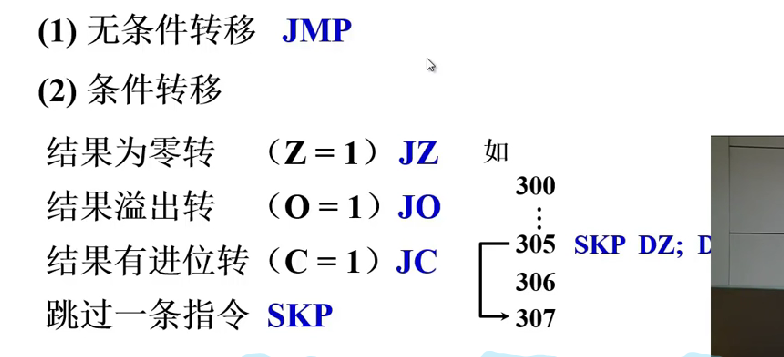

4.转移

5.调用和返回

6.陷阱(中断)

7.输入输出

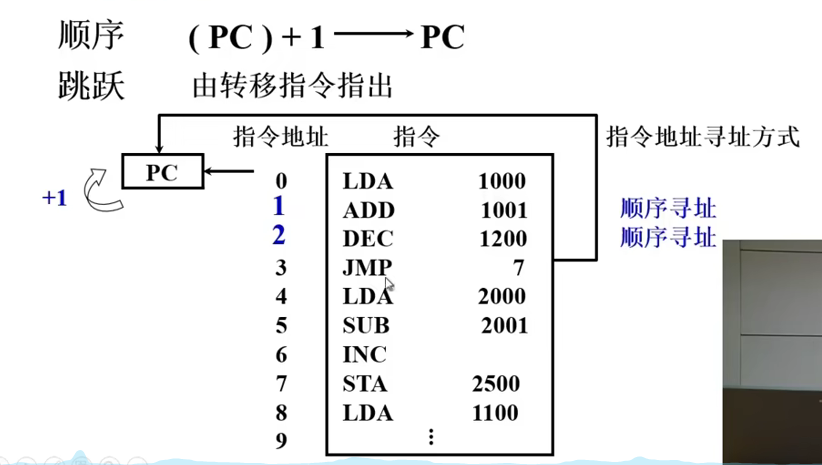

这个顺序 (PC)+1->PC

的+1 应该写成+X比较好

这个X的大小是当前指令占主存单元数量

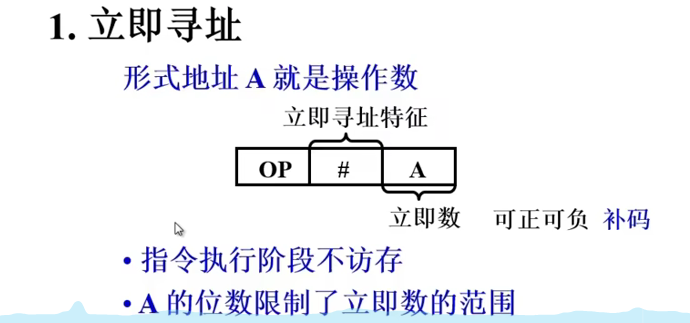

其立即数A本身随着指令就在CPU中,可以不用访存

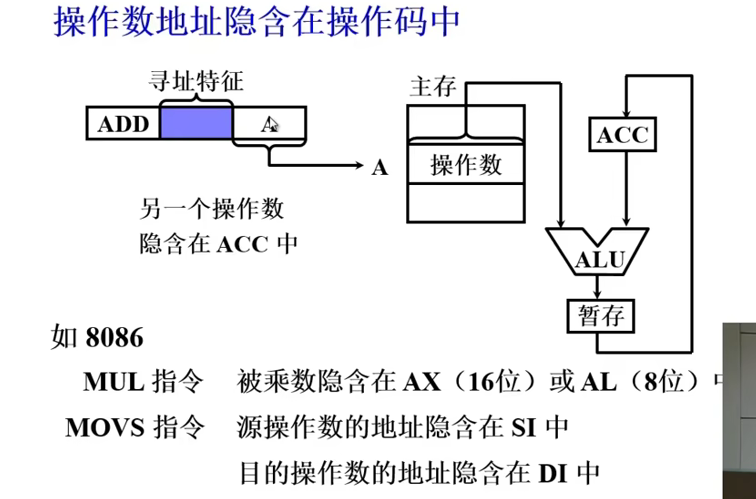

其中一个操作数隐含在ACC(累加器)中,另一个操作数需要到存储器中找

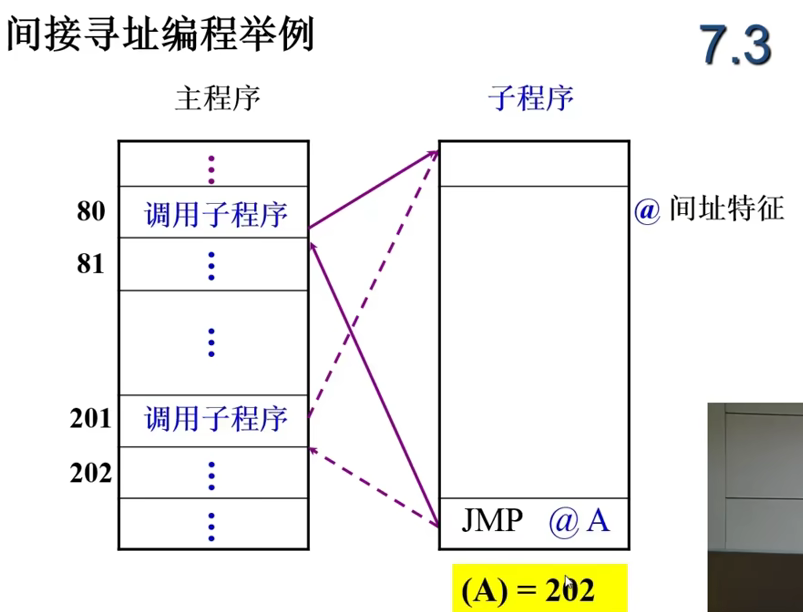

如下是程序调用与返回的案例,

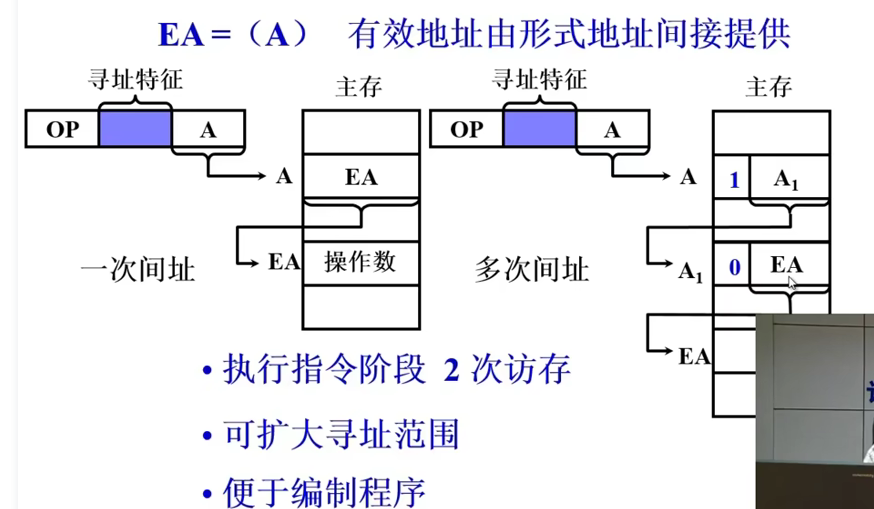

通过间接寻址的方式,即利用A保存的是真正地址

通过A地址中保存的真正地址进行跳转

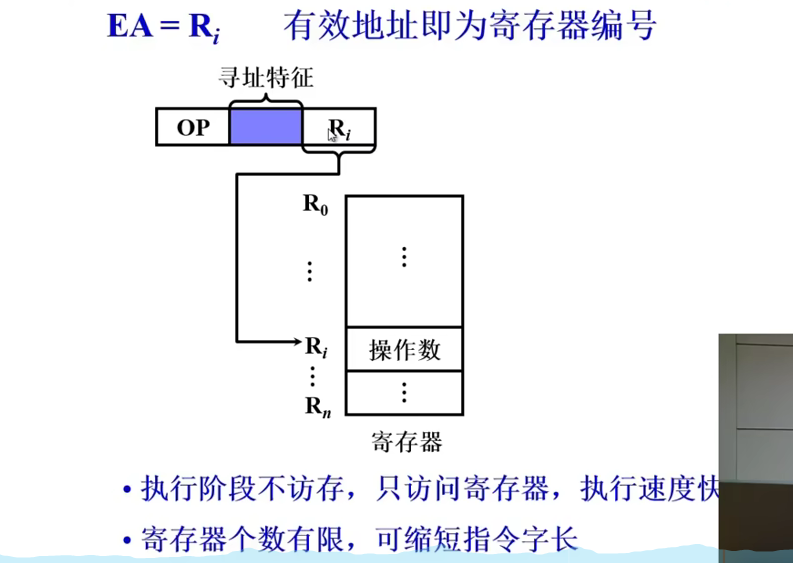

寄存器个数较少,即使地址码较短也没关系

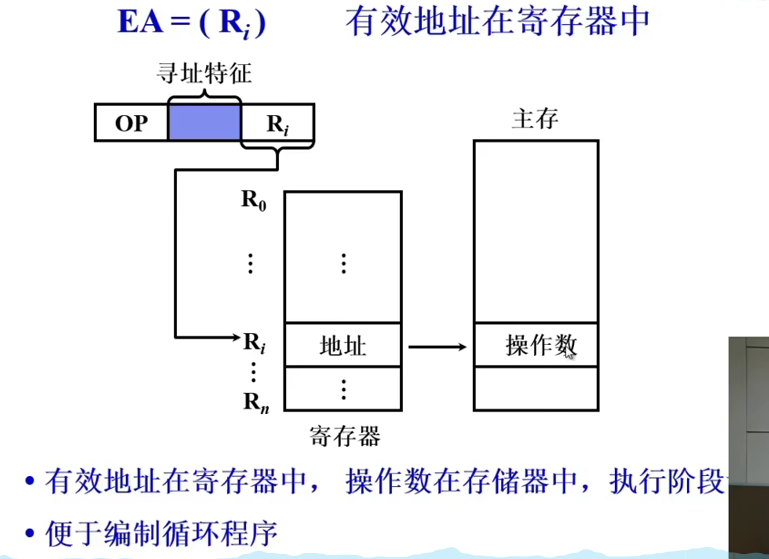

我们想要修改操作数的地址,只要修改寄存器中保存的地址

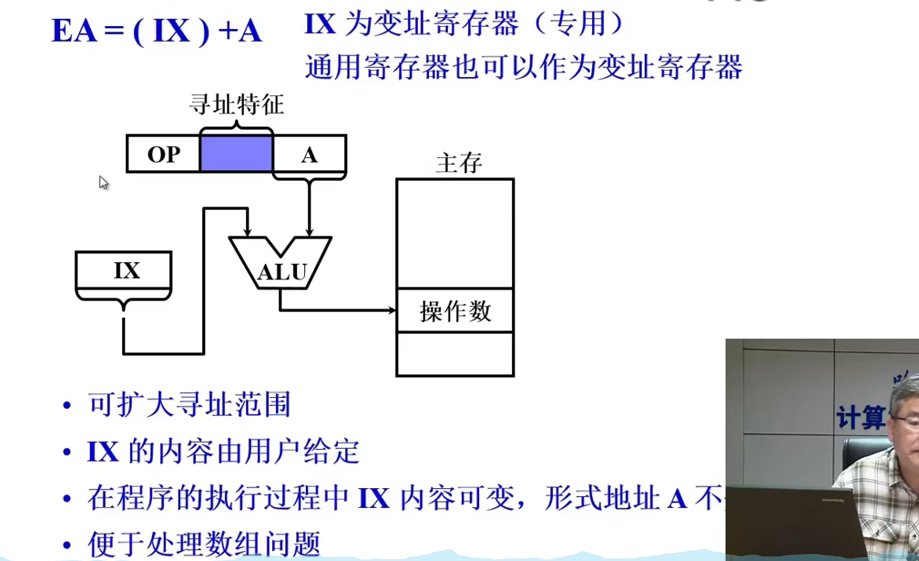

与基址寻址不同的是,IX容易变,A不可变

如果对数组进行操作,A是数组的起始地址

IX可以是下标

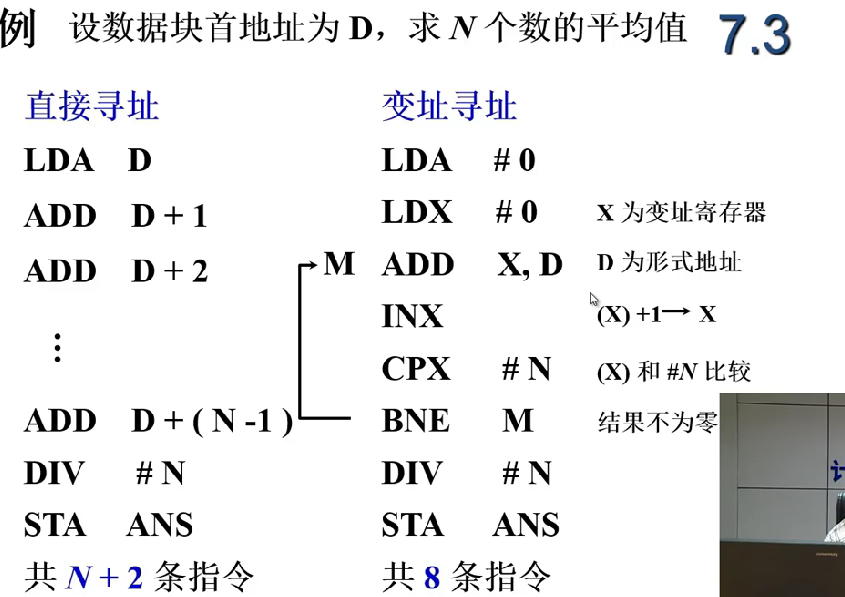

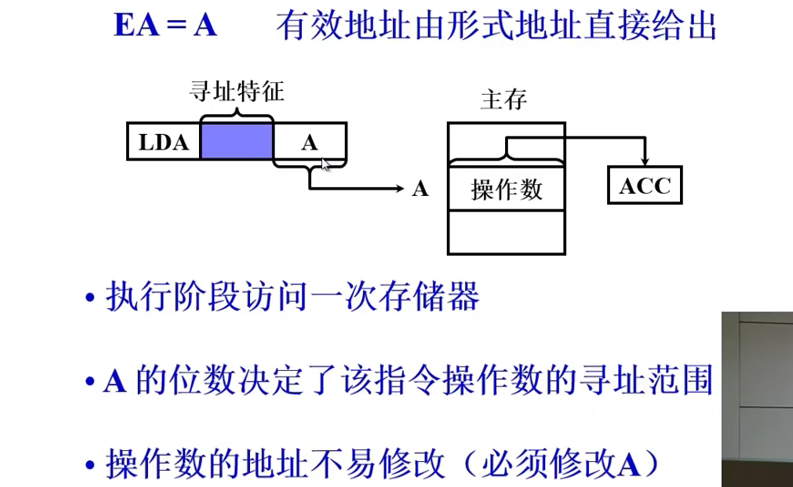

与直接寻址的比较:

直接寻址一条指令只能指明一个数据

而变址寻址可以通过循环对IX进行变动,达到遍历目的

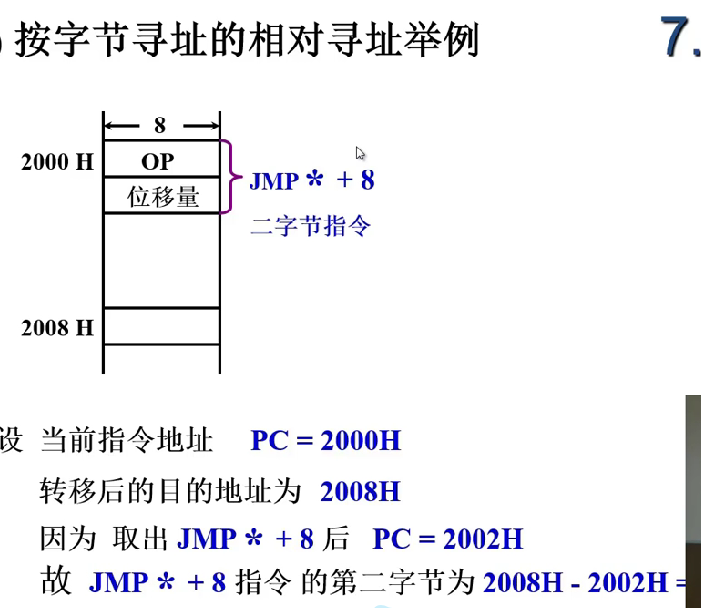

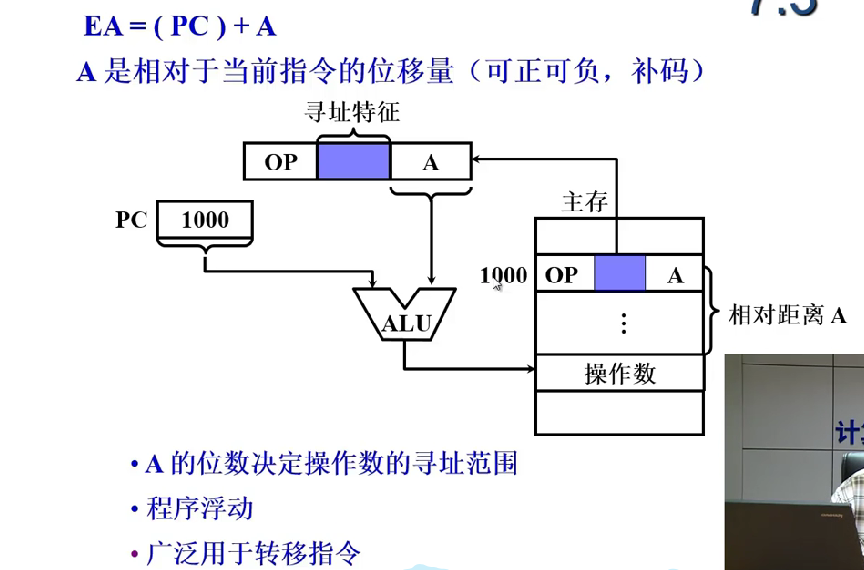

A是偏移量

注意PC中的值是在取完一个指令,还没等这条指令运行就变动的

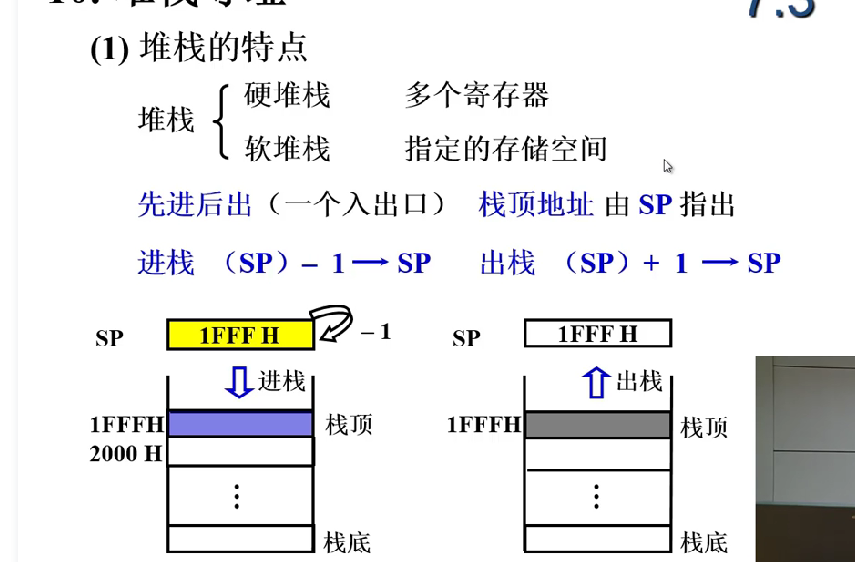

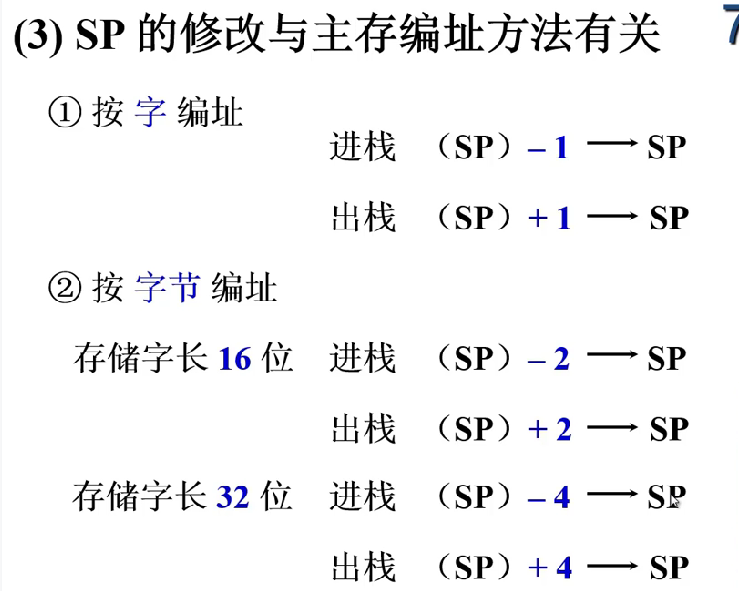

要注意的是SP是从栈底往栈顶中,地址的编码大小不断减小的

解释:

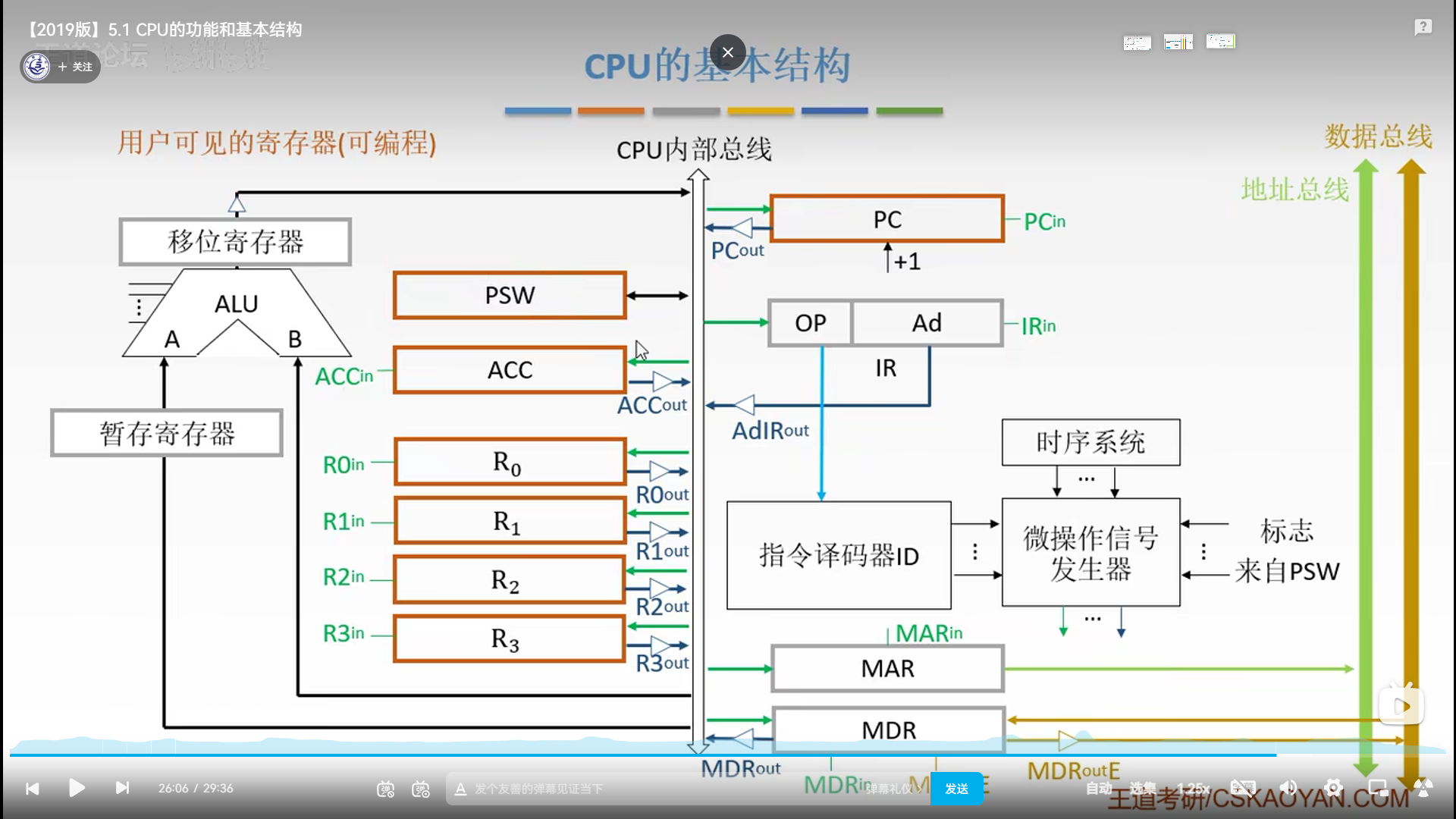

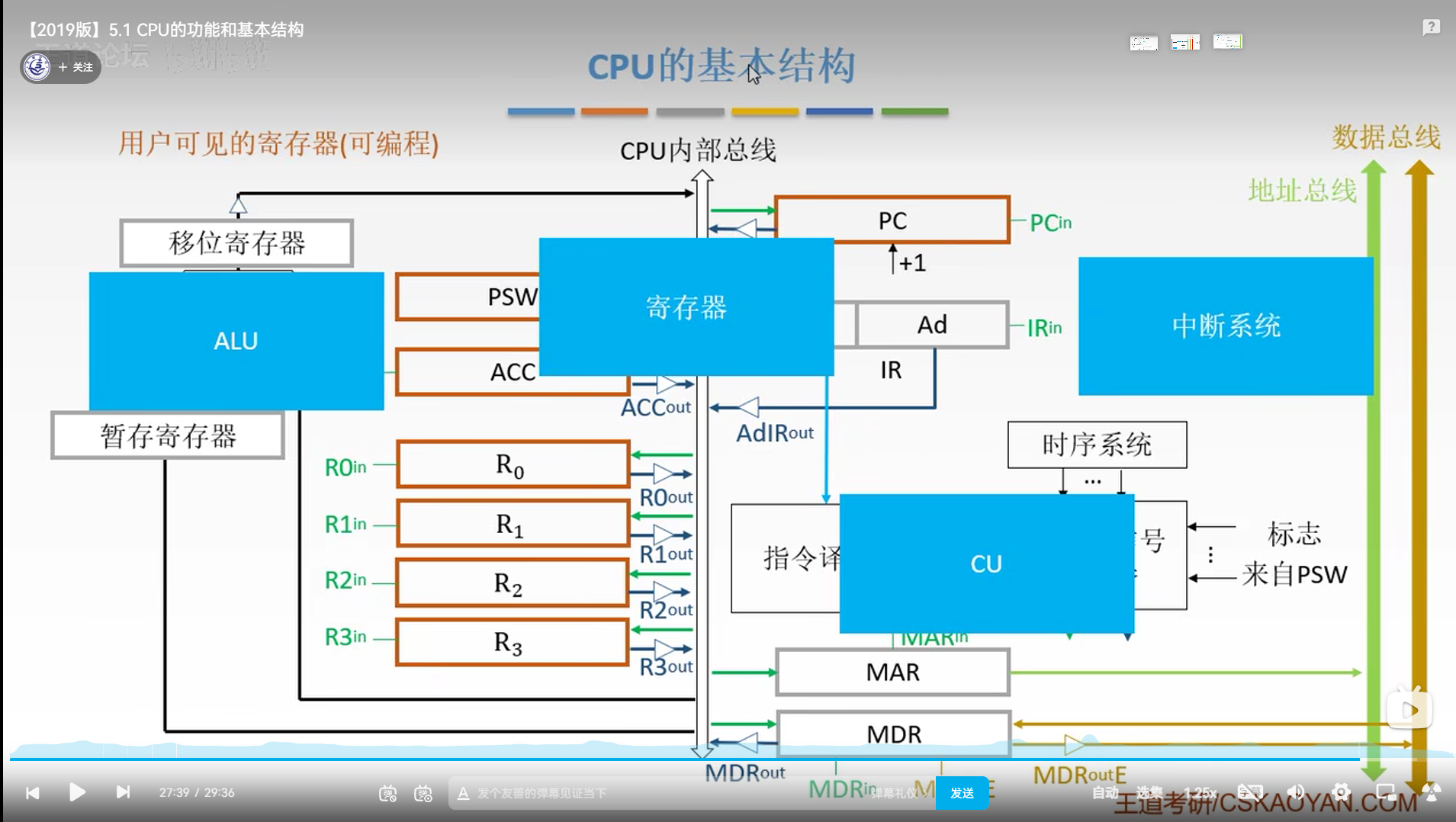

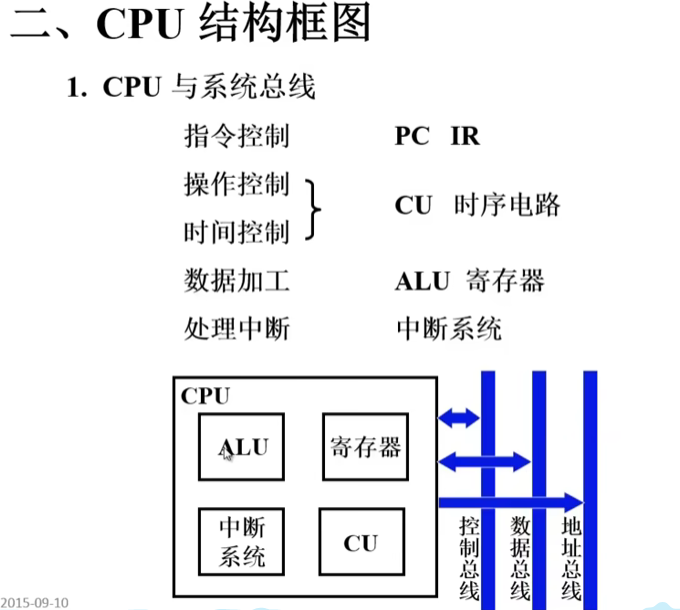

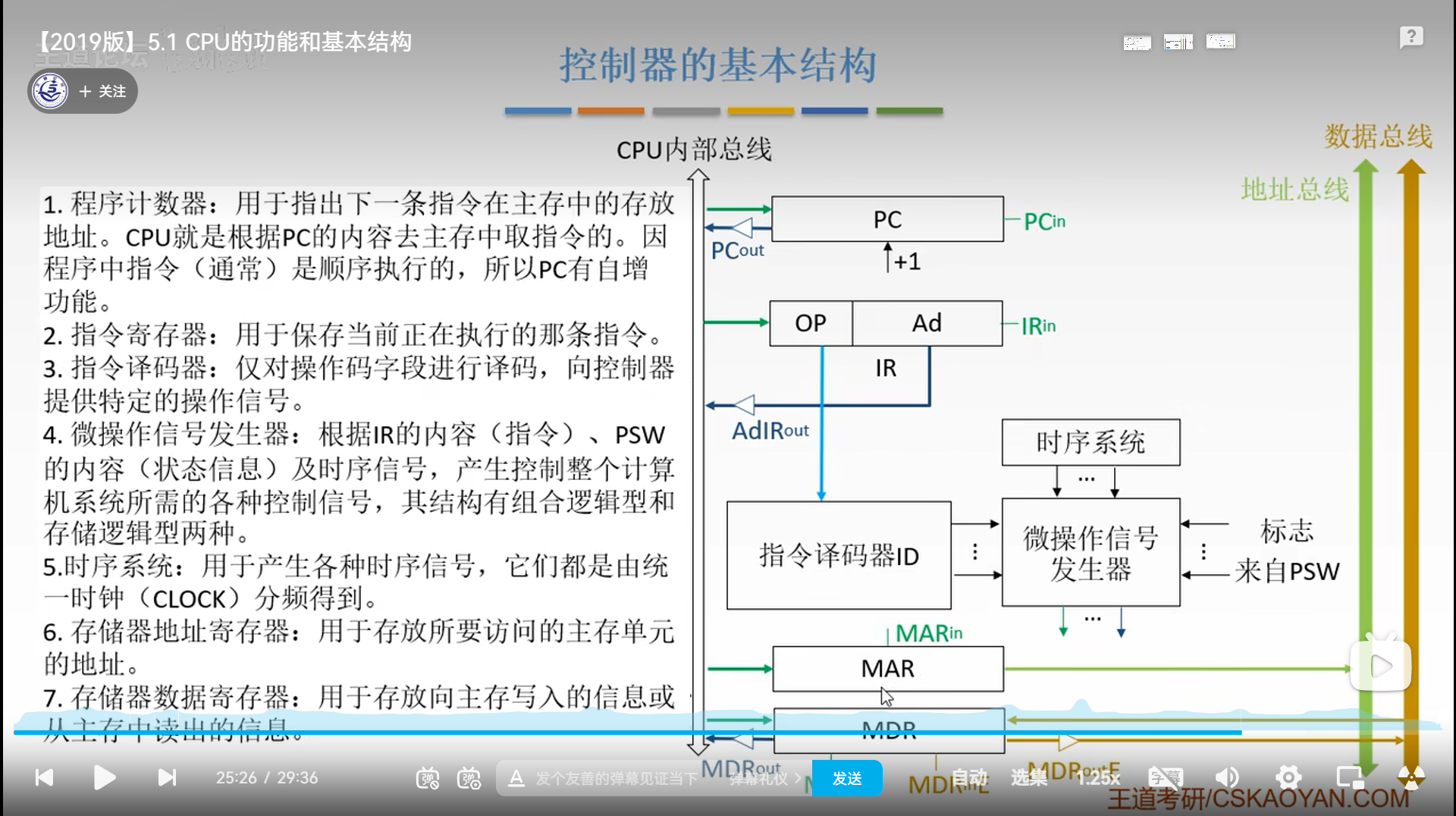

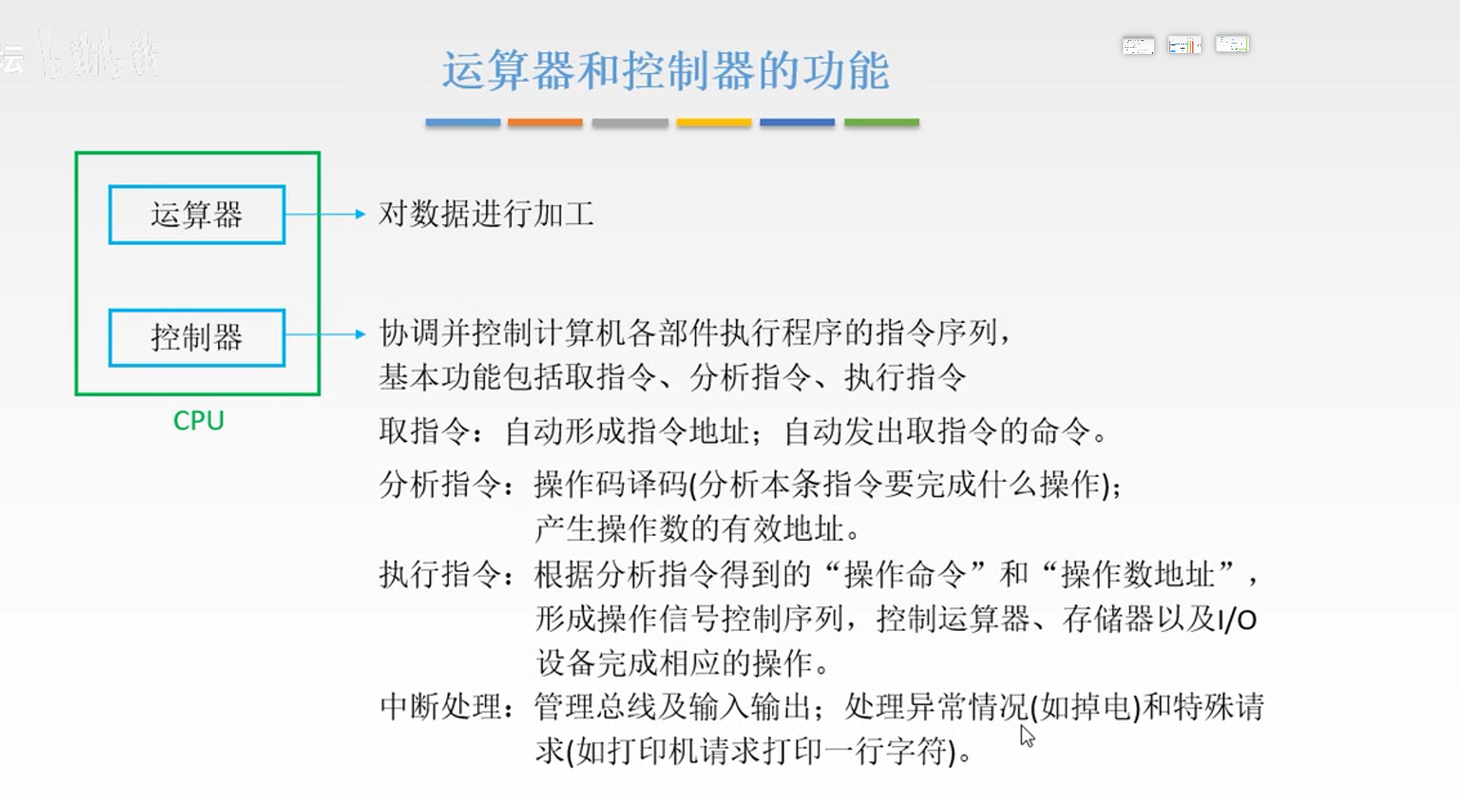

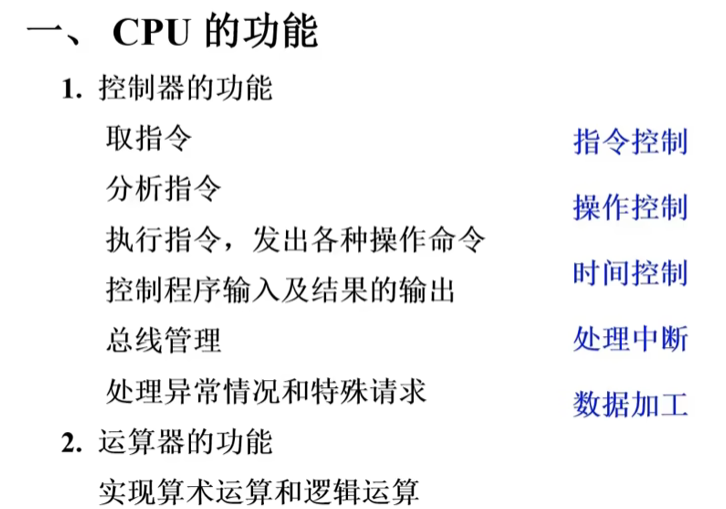

根据CPU的功能得出CPU的结构

1.由于需要到主存中取得指令,需要知道指令的地址,其保存到PC中,

PC的值的改变是在取指周期中进行的

同时指令需要在CPU中暂时保存,其保存在IR(指令寄存器)中

2.操作和时序的控制都需要CU(控制器)来实现

同时CU和操作都受到时序的影响

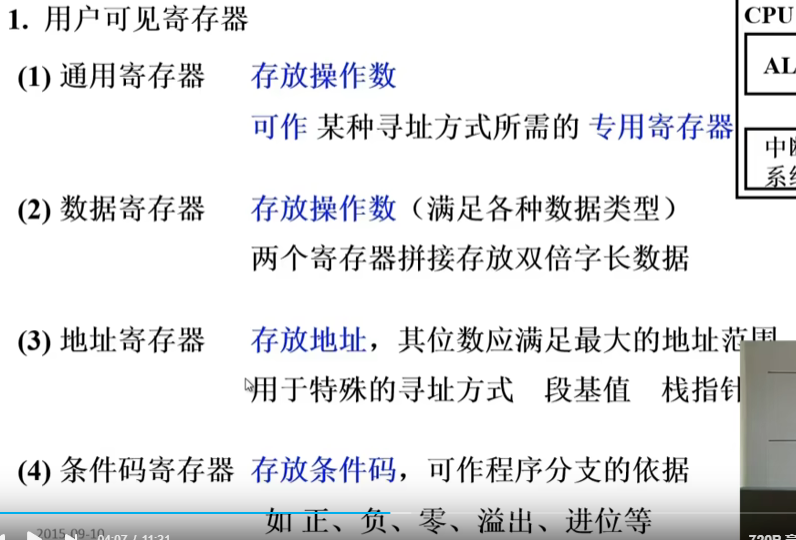

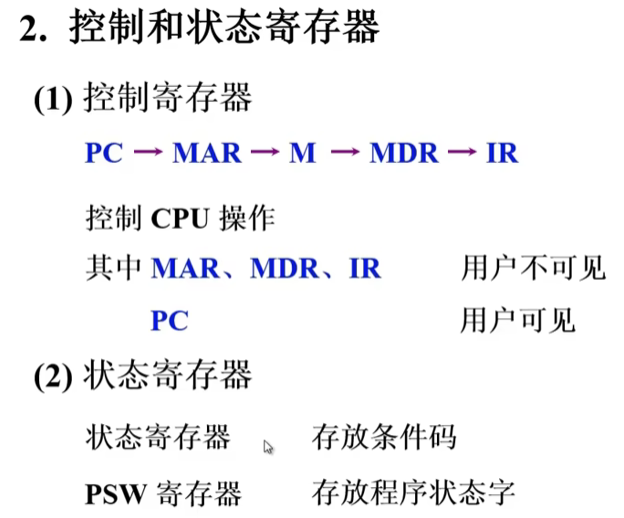

CPU的寄存器:

解释:

MAR是主存地址寄存器:

其在CPU中的作用是:

将要访存的地址先保存到MAR中,然后MAR中的数据放到地址总线中

地址总线再给主存发送信息(打通信息传输通道一样的感觉)

MDR是主存数据寄存器:

在CPU中的作用是:

将主存中通过数据总线发送过来的数据保存到MDR中

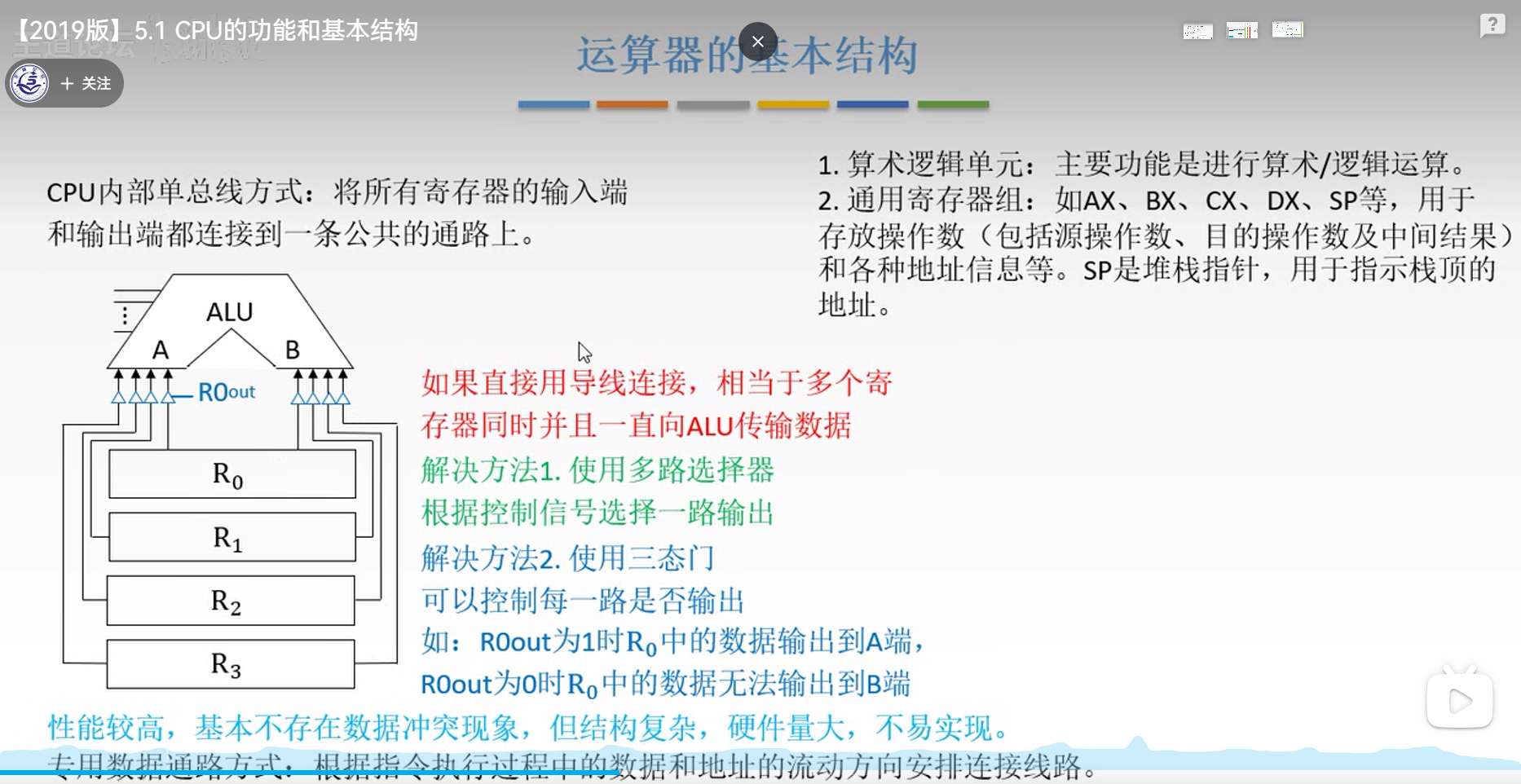

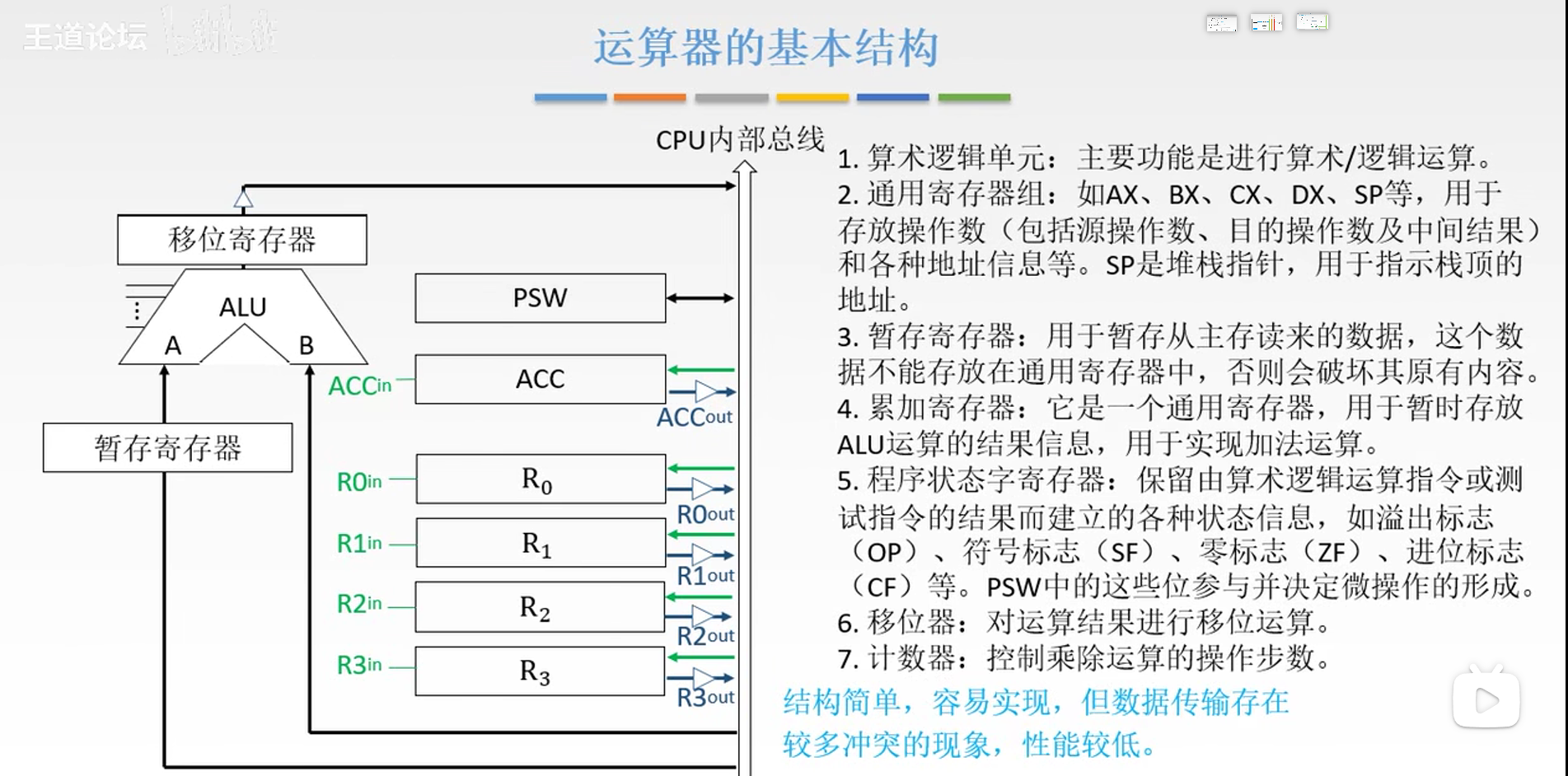

运算器基本结构

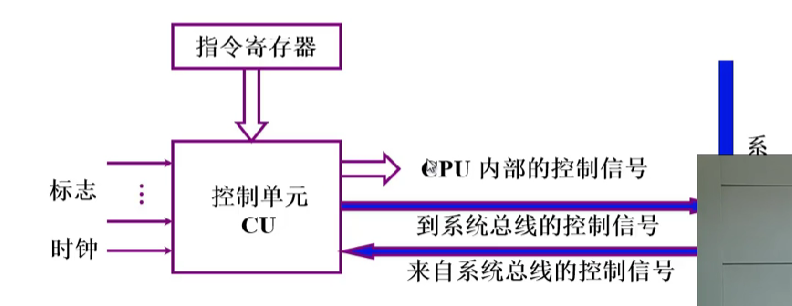

控制器的基本结构

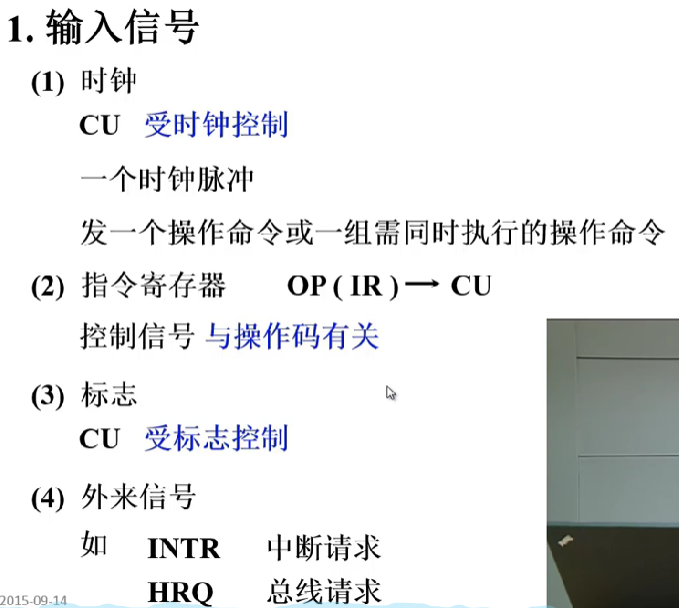

控制单元的输入信号:

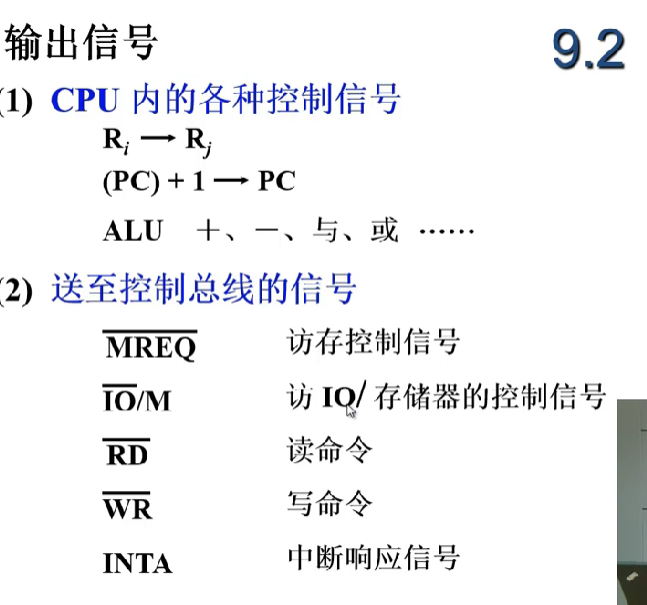

控制单元的输出信号:

控制信号的发出:

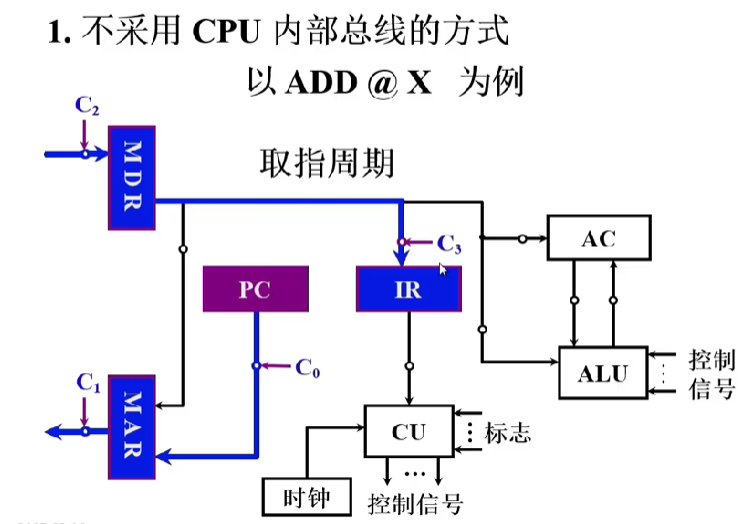

不采用CPU内部总线的方式:

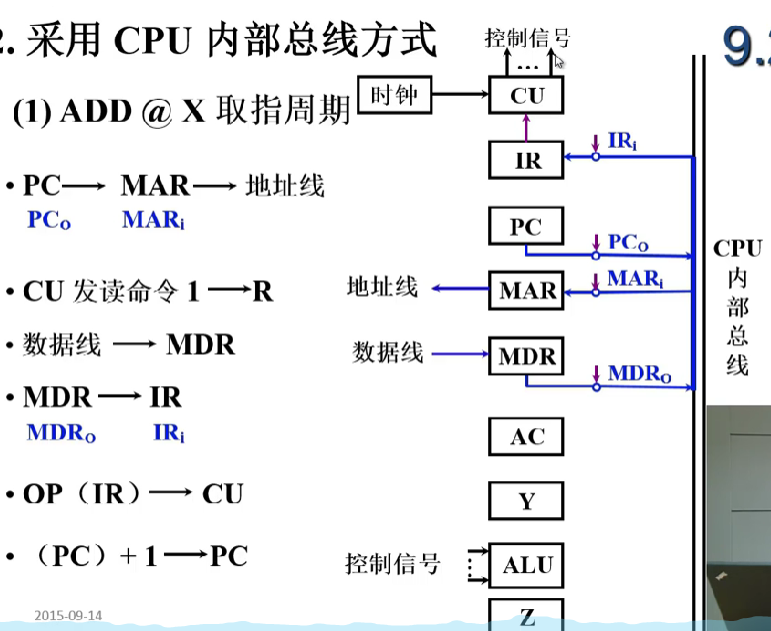

采用CPU内部总线的方式:

指令执行过程

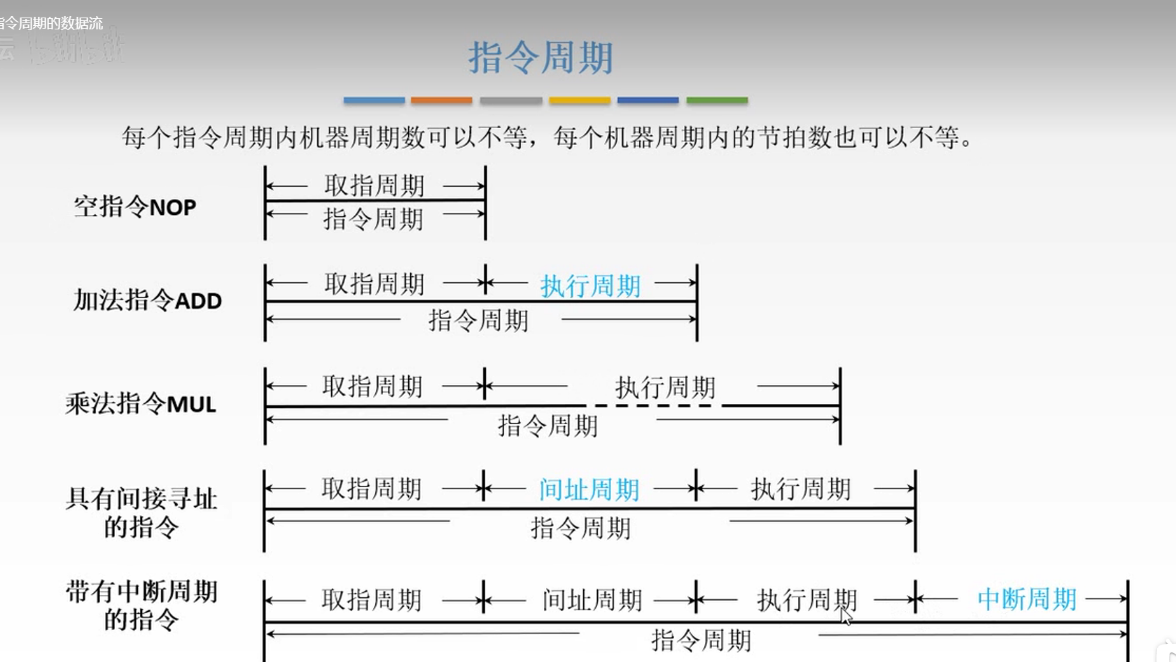

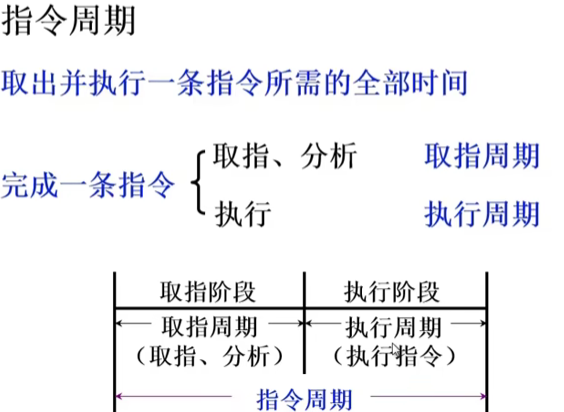

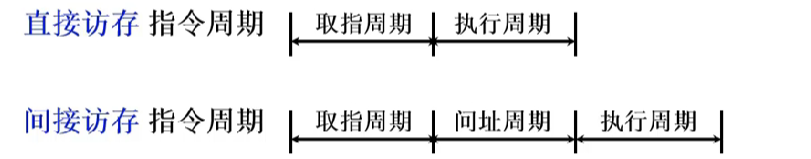

指令周期:

解释:

对于间址周期的解释:

如果只有取指周期和执行周期,那么一般

取指周期时就将操作数保存到了CPU中,

执行周期时就直接将操作数拿过来进行操作

或者是再访问一次主存将真正的数据拿过来

但是根据指令那章我们知道,我们还要间接寻址和基址寻址等方式

在指令中的操作数部分不是直接的数据地址或数据

为了找到真正的数据,我们还需要多次访存

如果将这些时间算入执行周期,那么执行周期会十分长

于是我们有了间址周期

间址周期干的事就是找到有效地址

到了执行周期我们就用有效地址在访问一次主存,

找到真正的数据

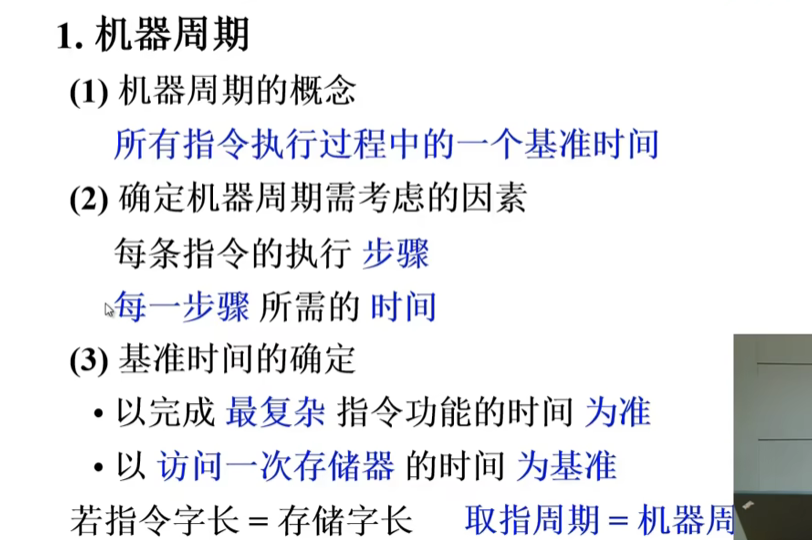

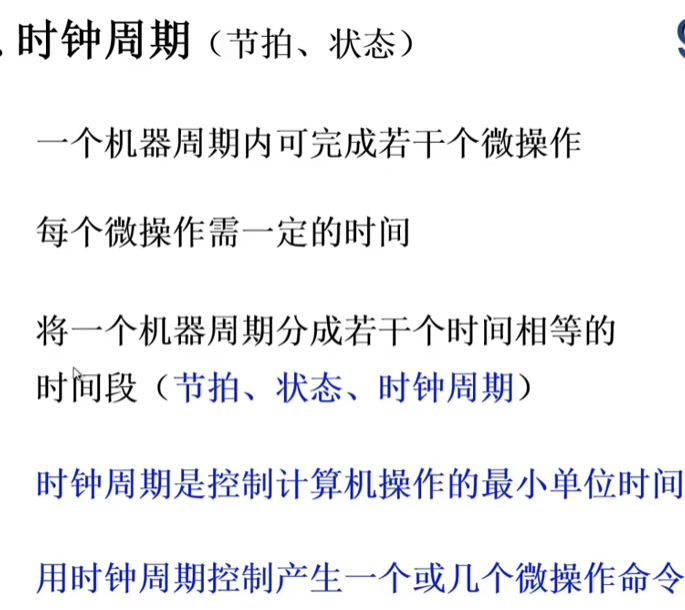

时钟周期:又称为振荡周期,由单片机片内振荡电路OSC产生,常定义为时钟脉冲频率的倒数,是时序中最小的时间单位。

它控制着计算机的工作节奏,使计算机的每一步工作都统一到它的步调上来。

显然,对同一种机型的计算机,时钟频率越高,计算机的工作速度就越快。

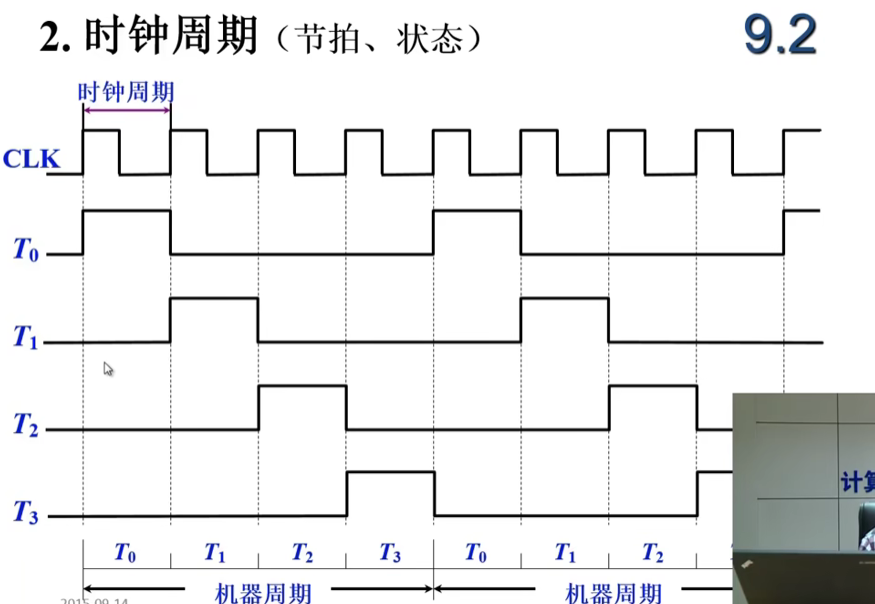

机器周期:也称为CPU周期。在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段(如取指、译码、执行等),

每一阶段完成一个基本操作。

完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个时钟周期组成。

指令周期:CPU每取出一条指令并执行这条指令,都要完成一系列的操作,

这一系列操作所需要的时间通常叫做一个指令周期。

换言之指令周期是取出一条指令并执行这条指令的时间。

由于各条指令的操作功能不同,因此各种指令的指令周期是不尽相同的。

机器周期:

解释:

注意:这里机器周期的概念:所以指令执行过程中的一个基准时间

而不是理解成 所以指令执行过程的总时间

这个基准时间是:所有微操作中最复杂的操作所要花费的时间

一般访存是最花时间的,所以

时钟周期:

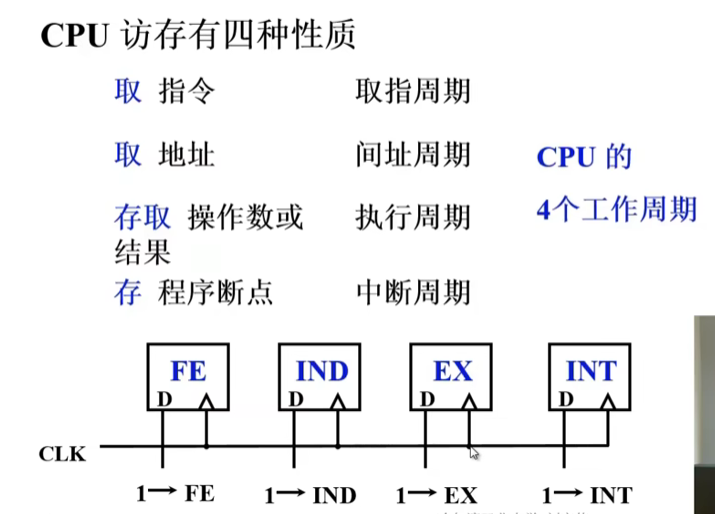

工作周期的标志:

解释:

CPU有四种情况下会进行访存,

为了知晓是哪一种情况下访存(或者说这一次访存的目的是什么)

我们要打上标记

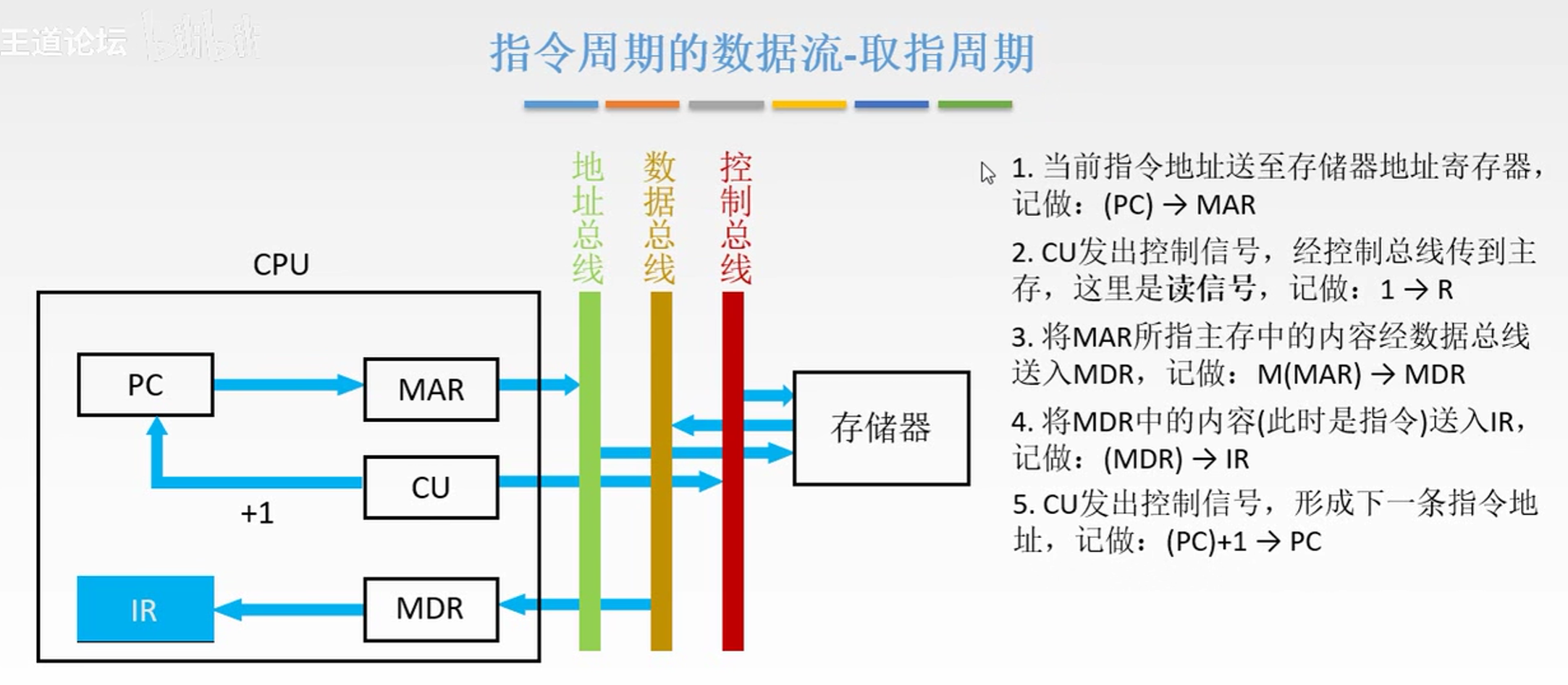

取指周期的操作

解释:

注意:PC是在取指周期最后进行+1

在以微程序设计的CU中:

同时一般我们说的 微操作(命令) 其实就是 如:

(1)(PC)-> MAR 1->R

(2) M(MAR)-> MDR

(3) (MDR)->IR (PC)+1->PC

(1),(2),(3)就是微指令了,微指令包含多个微操作

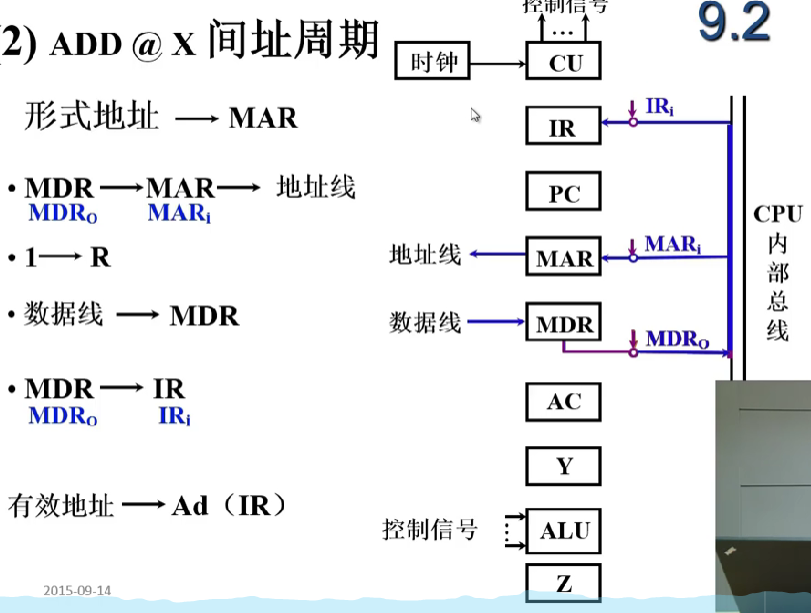

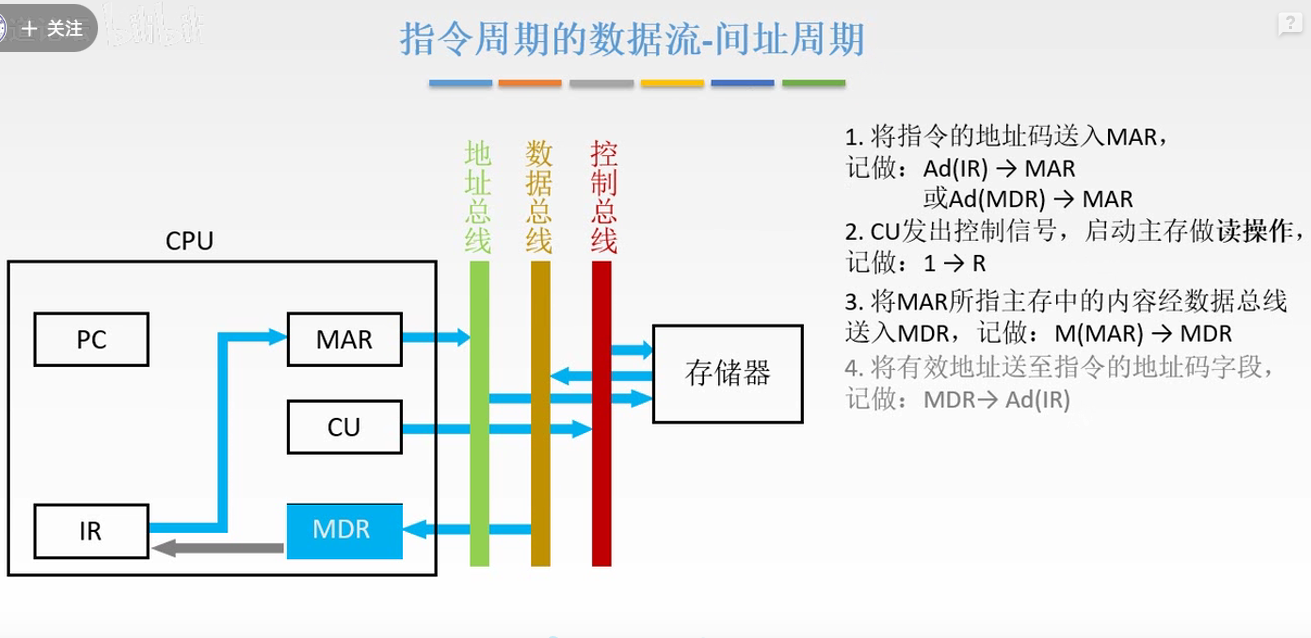

间址周期操作:

解释:

Ad()的含义是:取地址码部分

因为我们知道IR是指令寄存器,IR中保存的是指令

指令包括操作码,操作数(地址码)部分

Ad()就是取指令中的地址码部分

Op()同理,取指令中的操作码部分

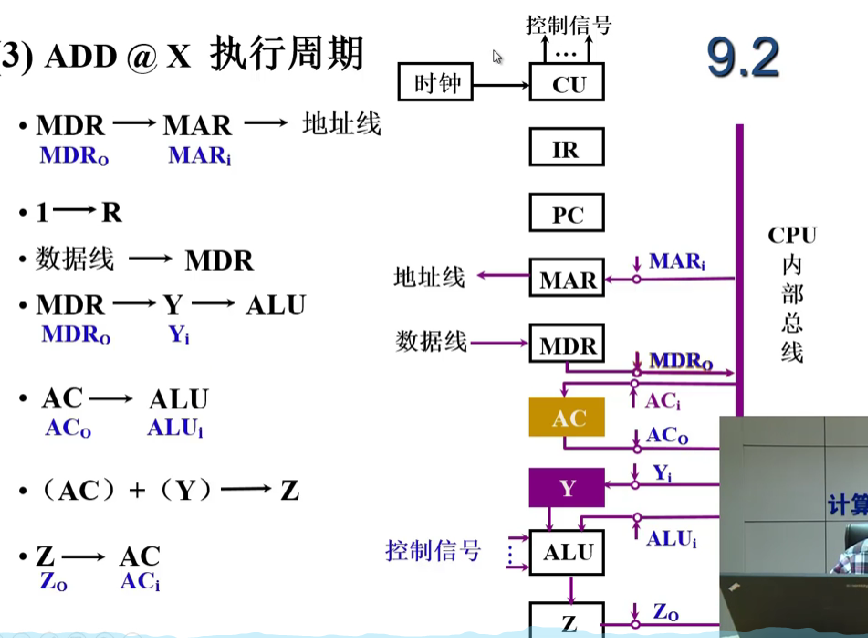

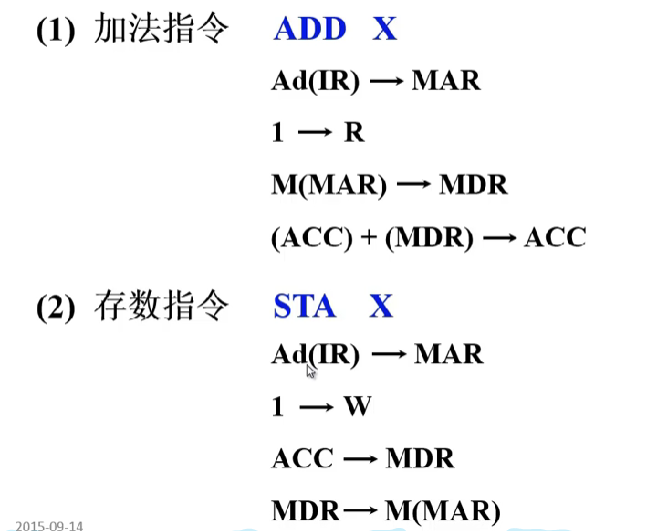

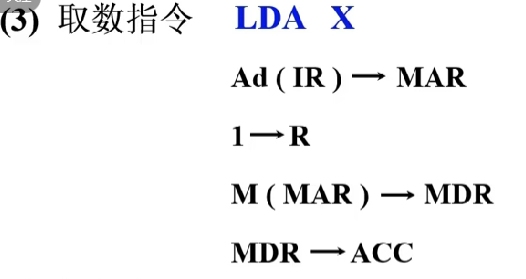

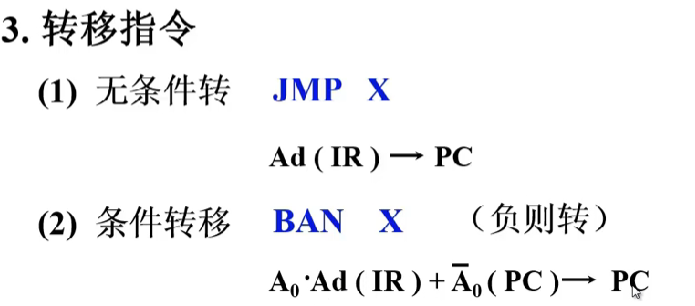

执行周期的操作:

不同指令的执行周期不同

不同的操作指令:

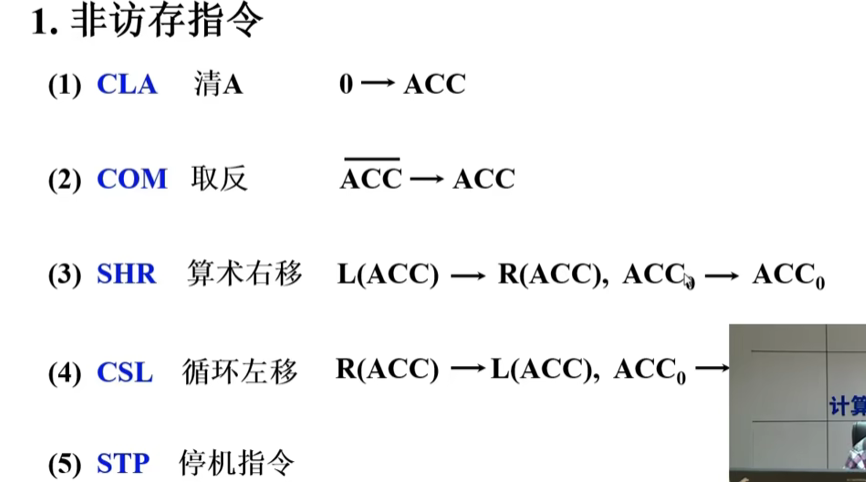

非访存指令:

解释:

CLA 清除ACC中的数据的指令

COM是对ACC中的数据每一位取反(二进制下)

访存指令:

解释:

加法指令其表示要将指令中地址码中受指向的数据与ACC中的数相加

为了取得地址码中受指向的数据,则要进行访存

存数指令即将数X保存到指定存储器中

取数指令即将数据取得保存到ACC中

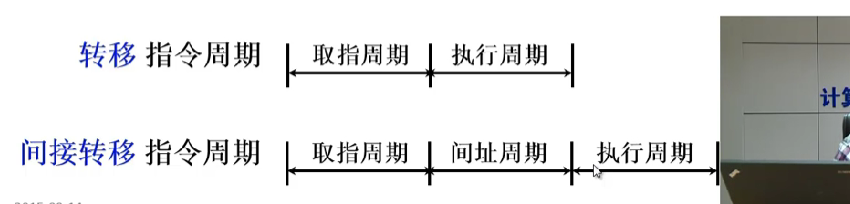

转移指令:

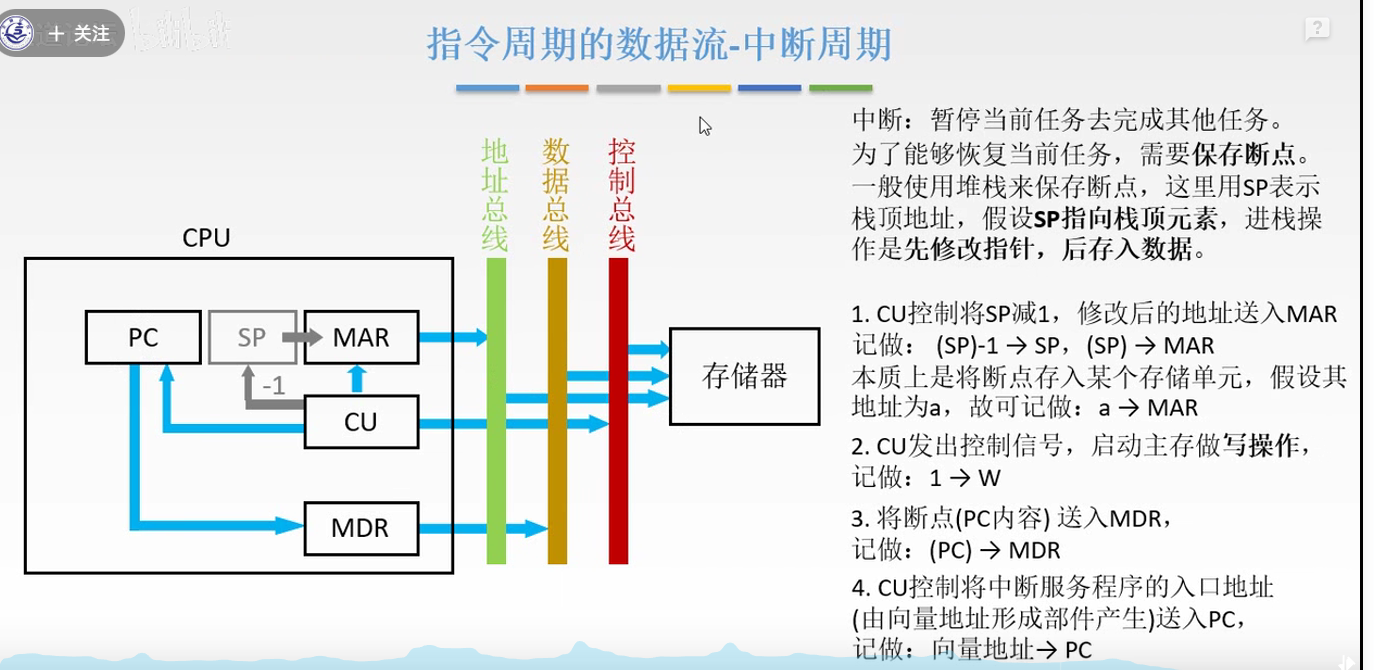

中断周期的操作

解释:

中断周期操作包括三部分:

1.保存断点

即保存PC中的数据到主存中,PC中的数据是原来下一次执行指令的地址

CU给出要保存到主存中的地址

2.形成中断服务程序的入口地址

由CU给出,用来指明下一次执行的指令是什么

3.硬件关中断

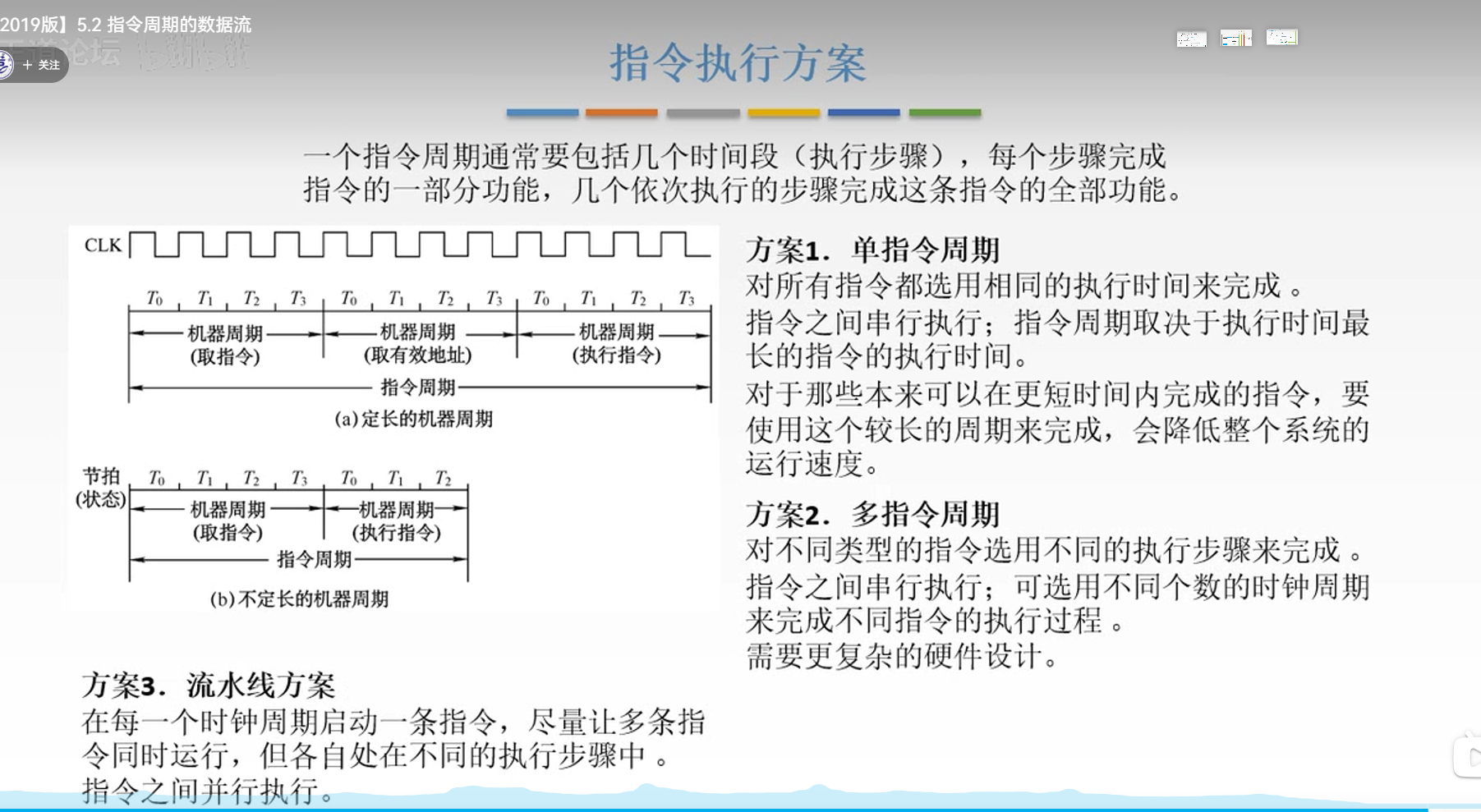

指令执行方案

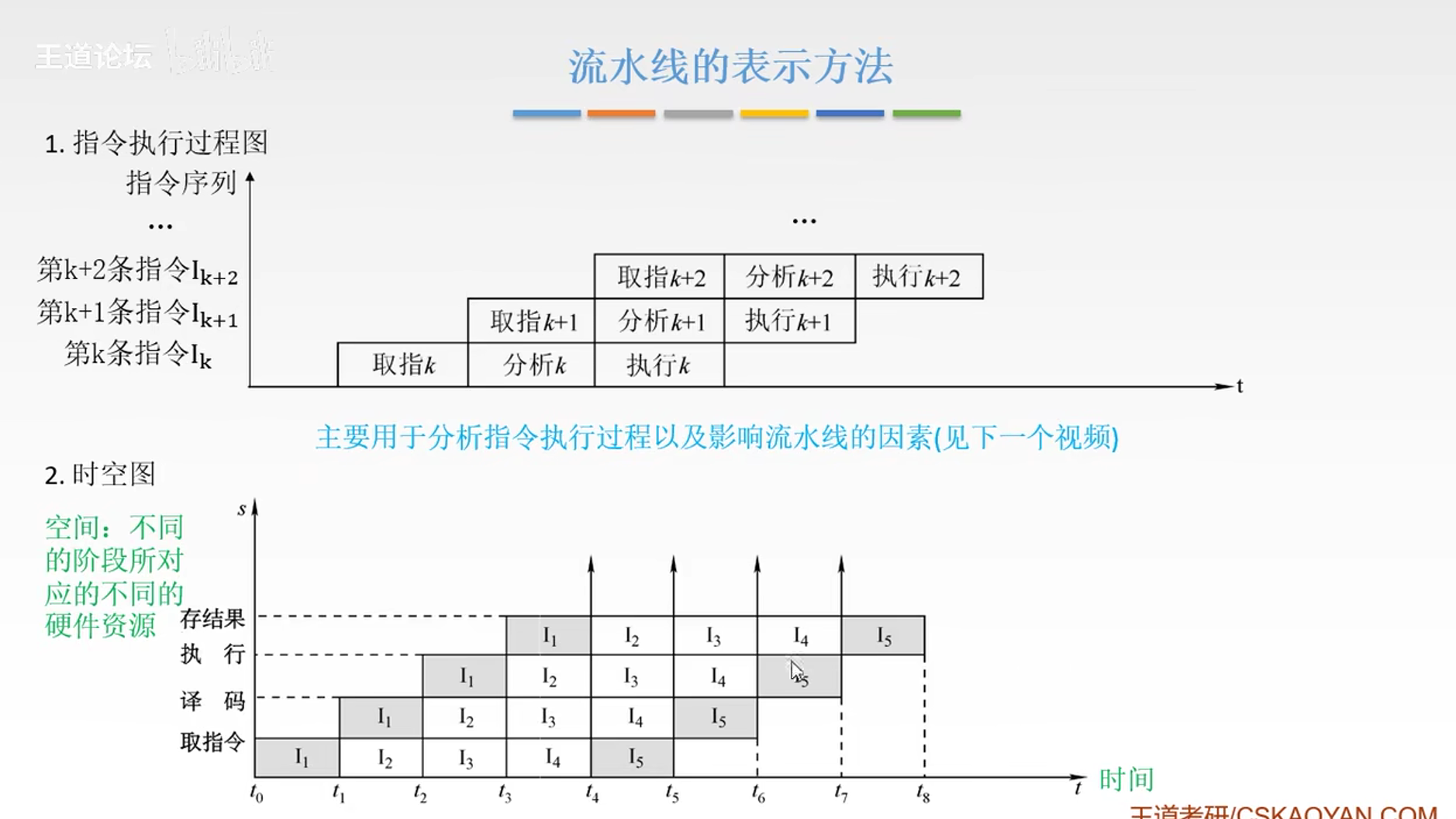

指令流水线:

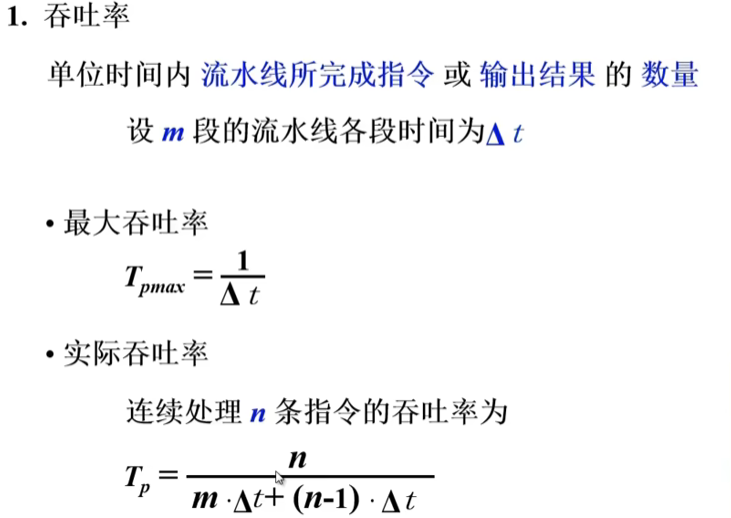

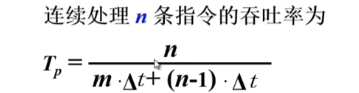

吞吐率:

解释:

我们这里是假设满负载运作,每 就会出一个结果

就会出一个结果

在结合这张图来看

实际吞吐率是开始需要 ,然后每经过

,然后每经过 就会出一个结果

就会出一个结果

所以结果为

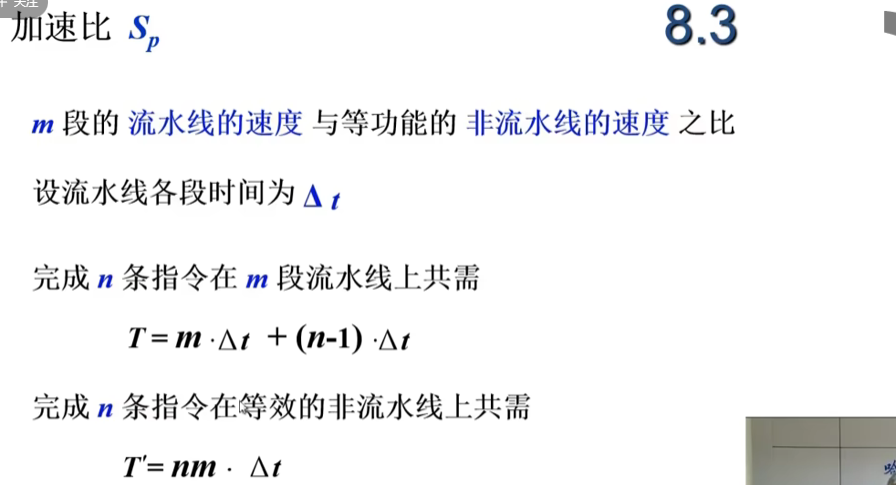

加速比:

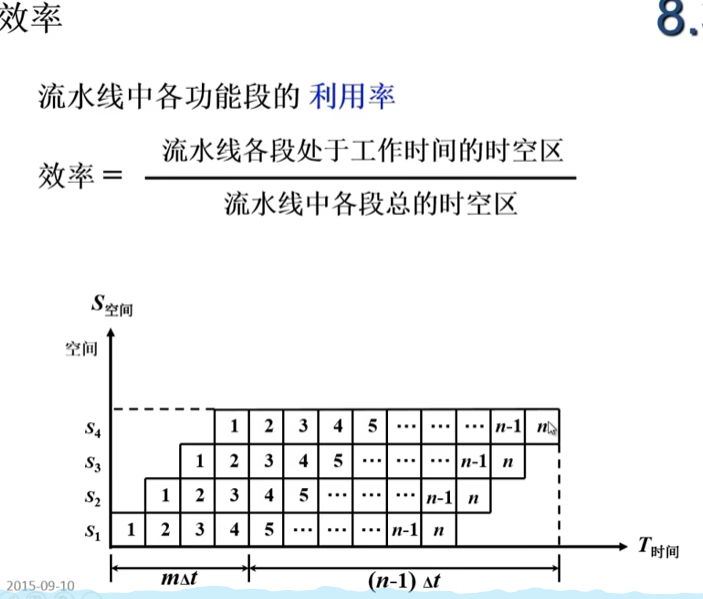

效率:

控制器的设计方案

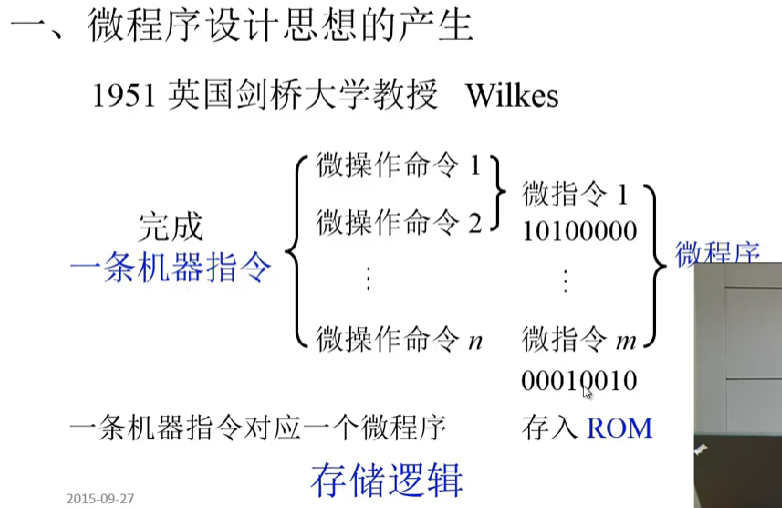

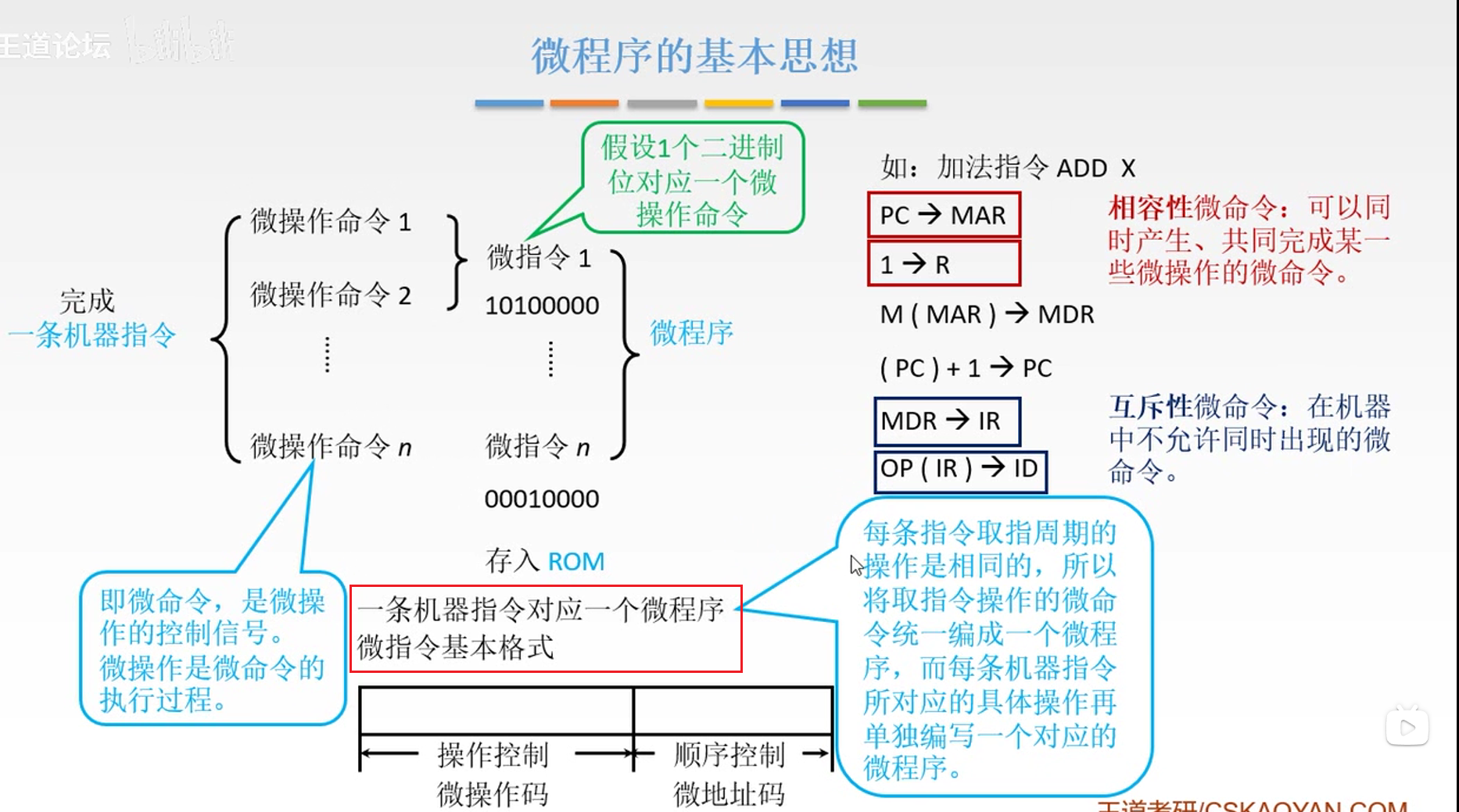

概念梳理:

解释:

微指令上的1/0,代表某一个微操作是否需要执行,1表示执行,0表示不执行

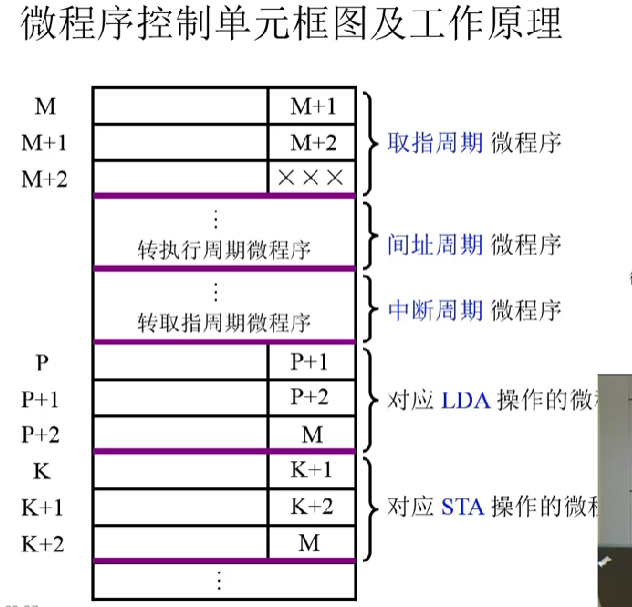

《控制存储器的构造》

解释:

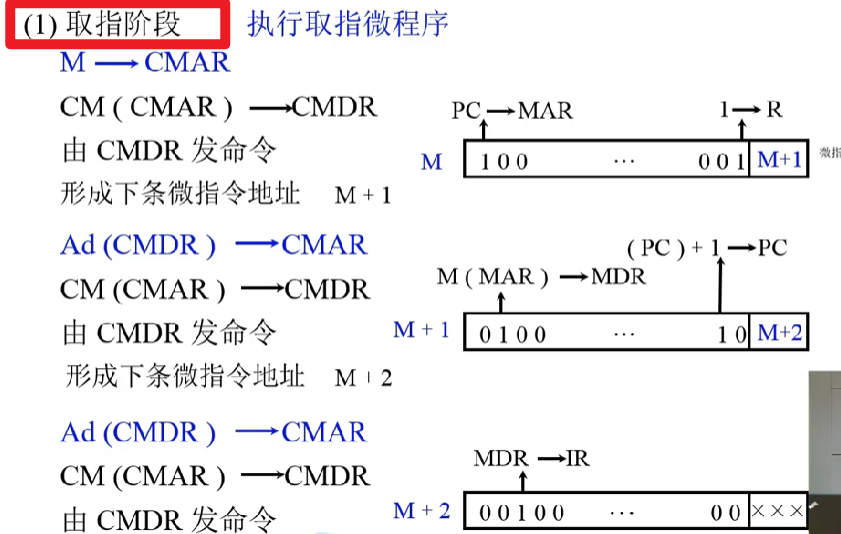

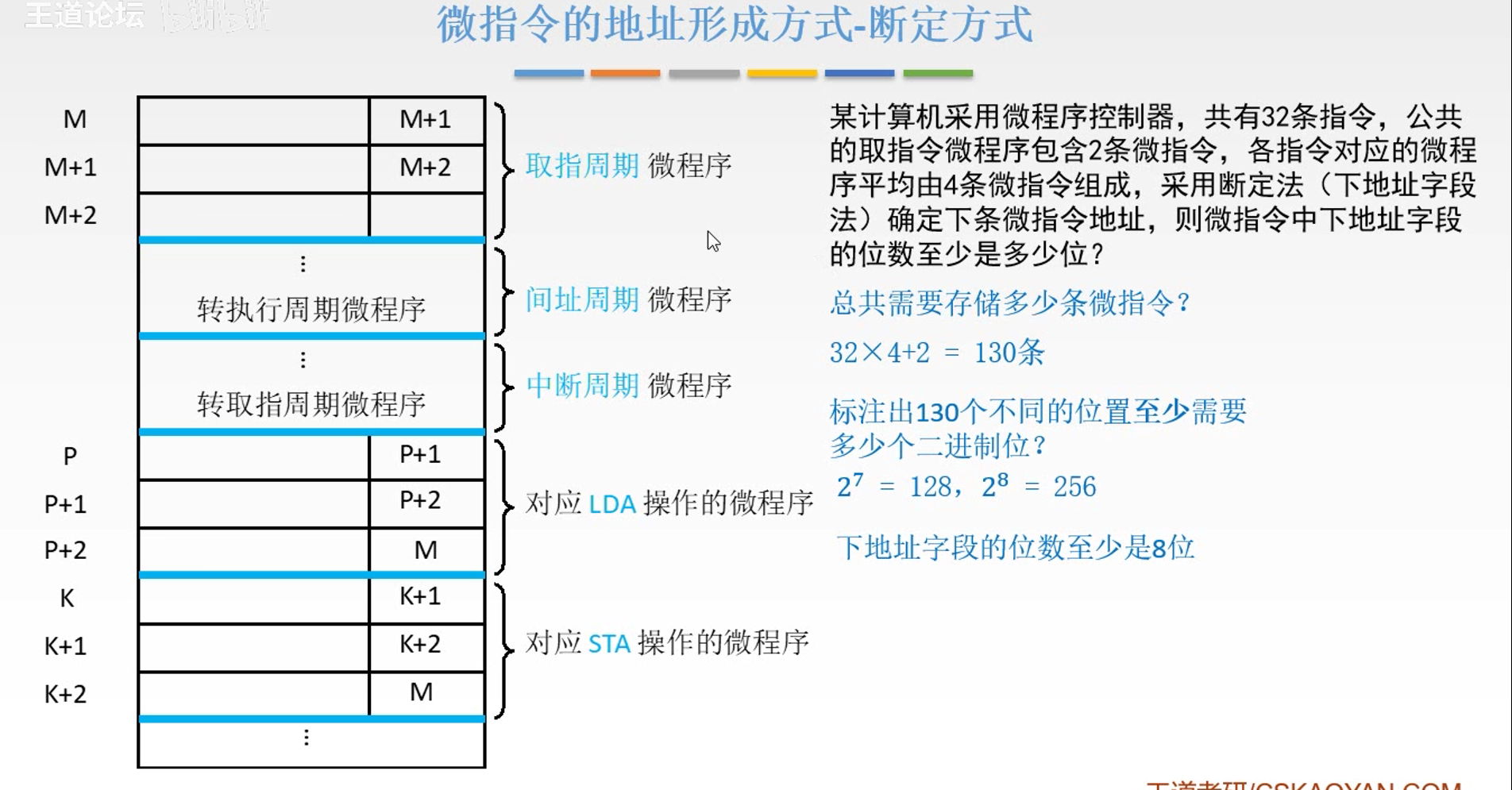

如图为取指周期的微指令((1),(2),(3))

如图为取指周期的微指令((1),(2),(3))

每一个微指令中都包含了一个或多个微操作(命令)

通过微指令中的01表示出来

解释:

因为某个周期要做的事有些是固定的,则取完一条微指令后

可以通过顺序取下一条微指令

如取指周期

为了取指

第1条微指令要干的微操作就是(PC)->MAR,1->R

紧接其后的第2条就是要M(MAR)->MDR

.....

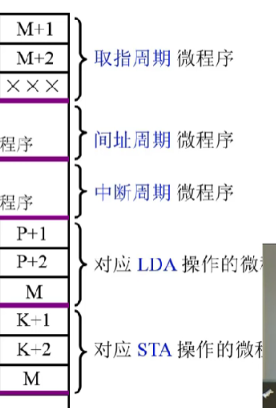

所以可以看到

这里的xxx,表示无法确定下一条微指令是啥

比如这里取指周期最后一条微指令的下地址为xxx

因为要执行下一条微指令是要根据指令的操作码部分来决定的

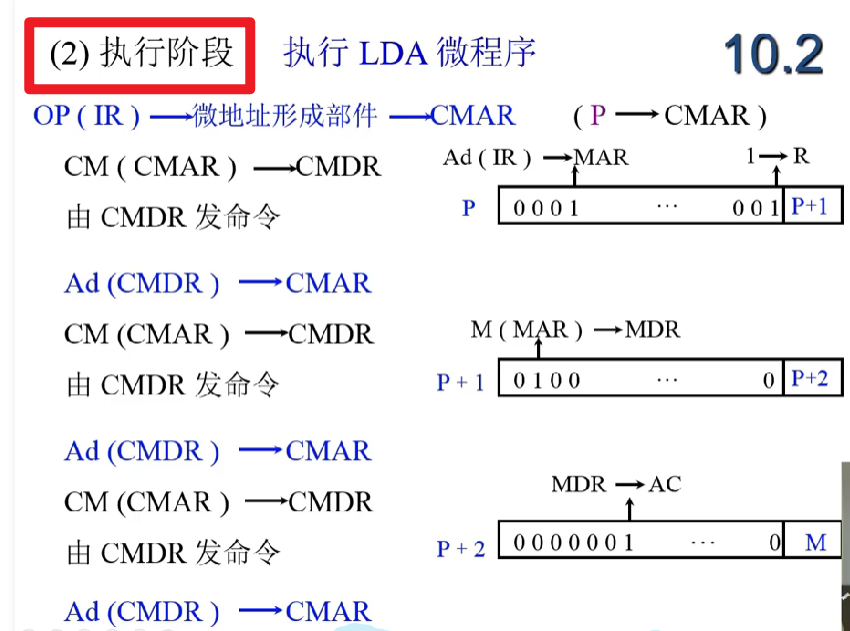

同时,执行周期要干的事,如这里的LDA操作

其最后一条微指令的下地址为M,即干完后接着取下一条指令(再进入取指周期)

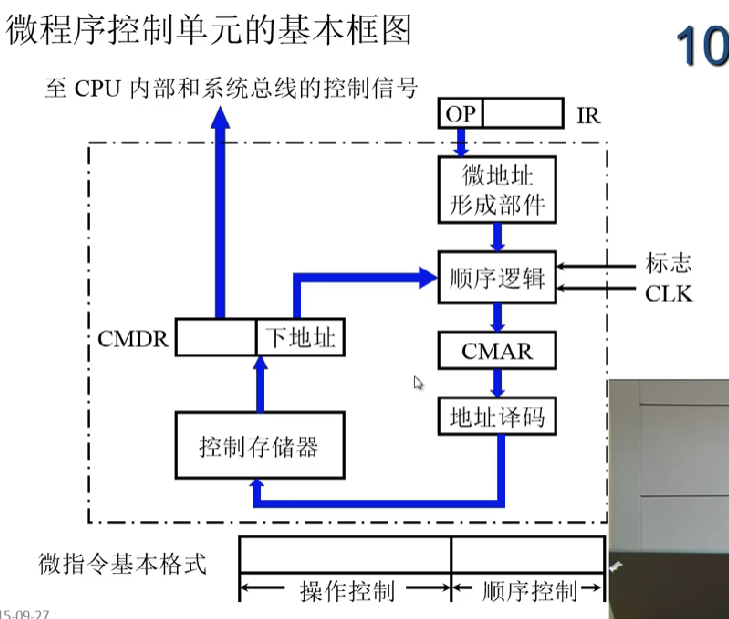

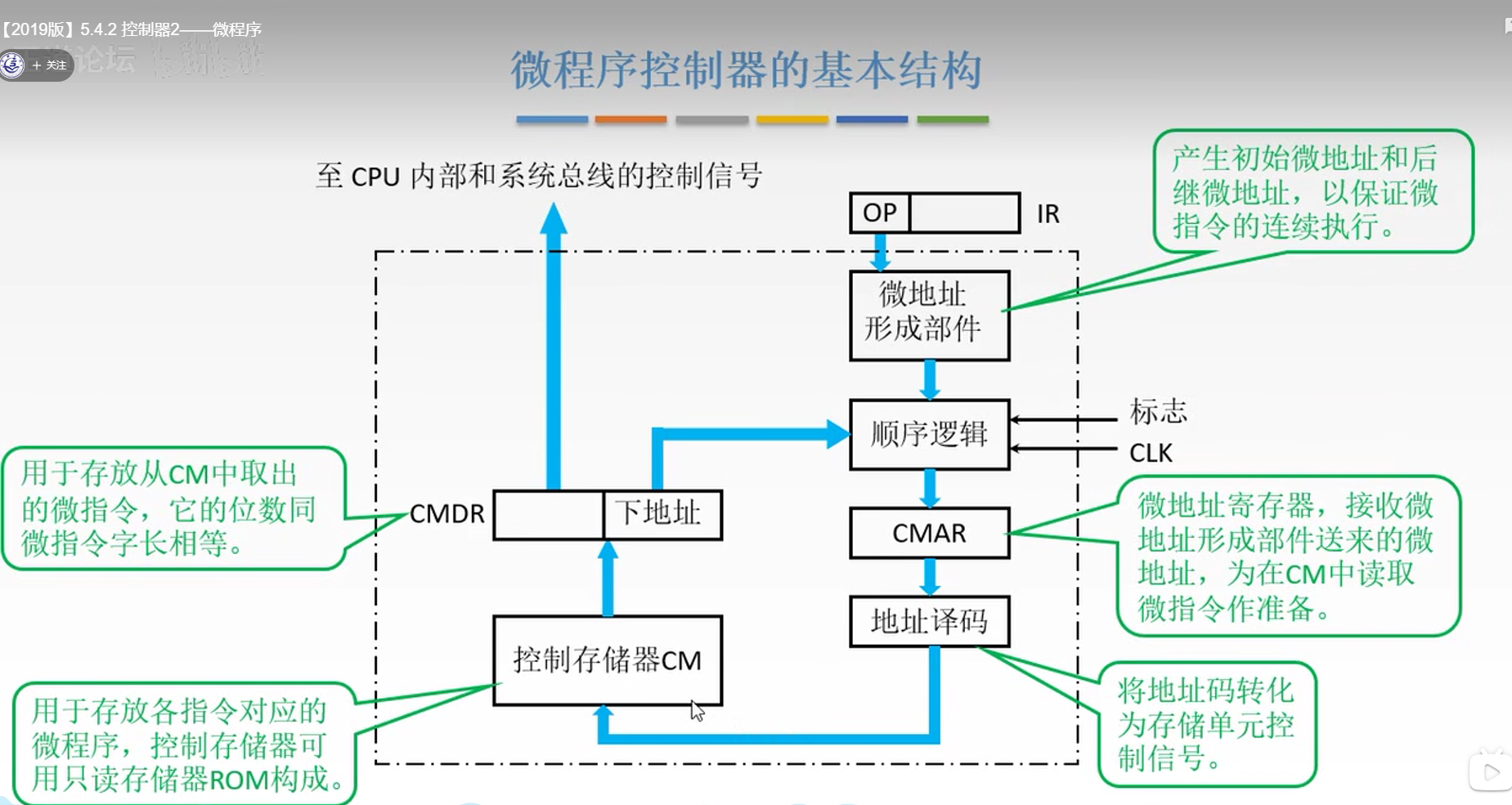

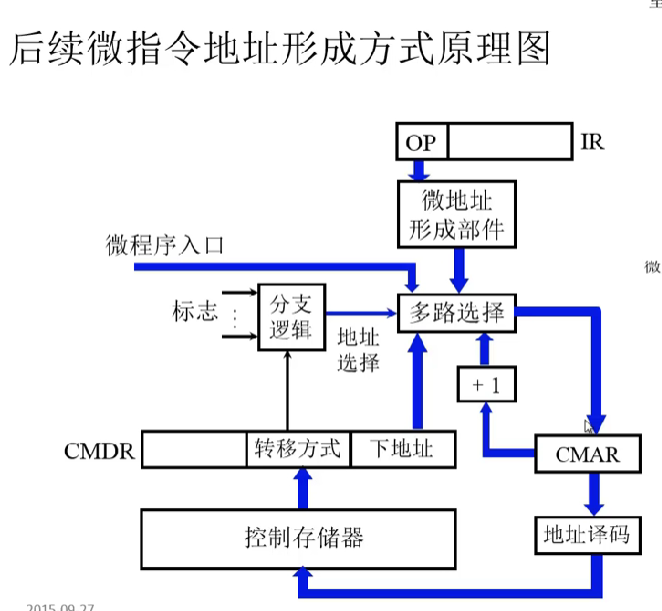

《控制单元的构造》

解释:

CMAR为控制存储器地址寄存器

CMDR为控制存储器数据寄存器

微指令基本格式中

顺序控制给出了下一条微指令在控制存储器中的地址

顺序逻辑用来决定最终下一条微指令在控制存储器中的地址

微地址形成部件是通过指令操作码来产生初始微指令地址

控制单元的工作过程

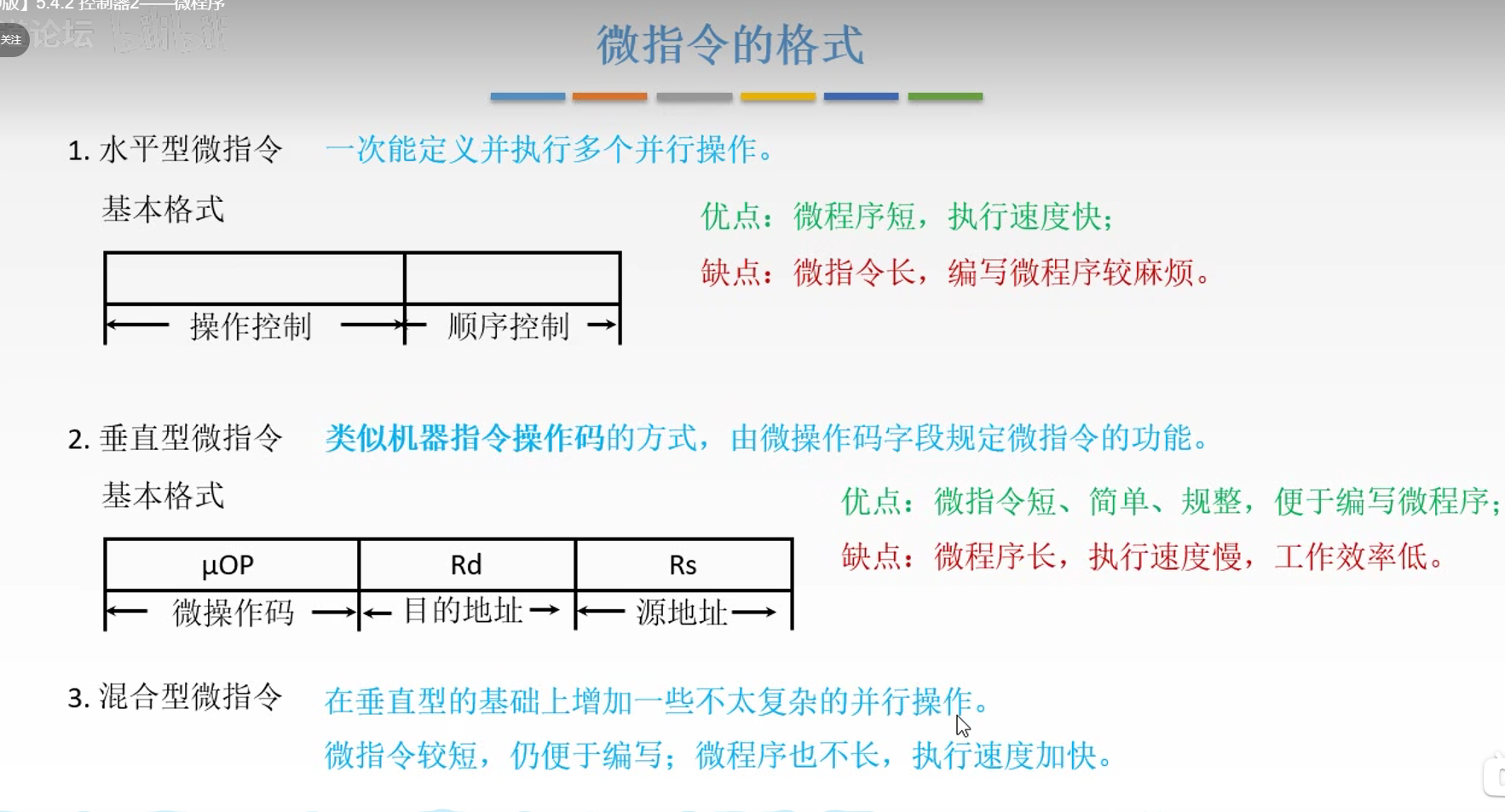

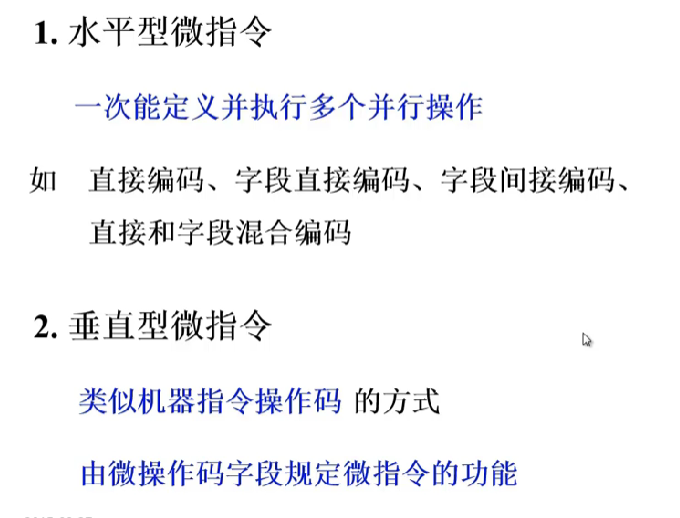

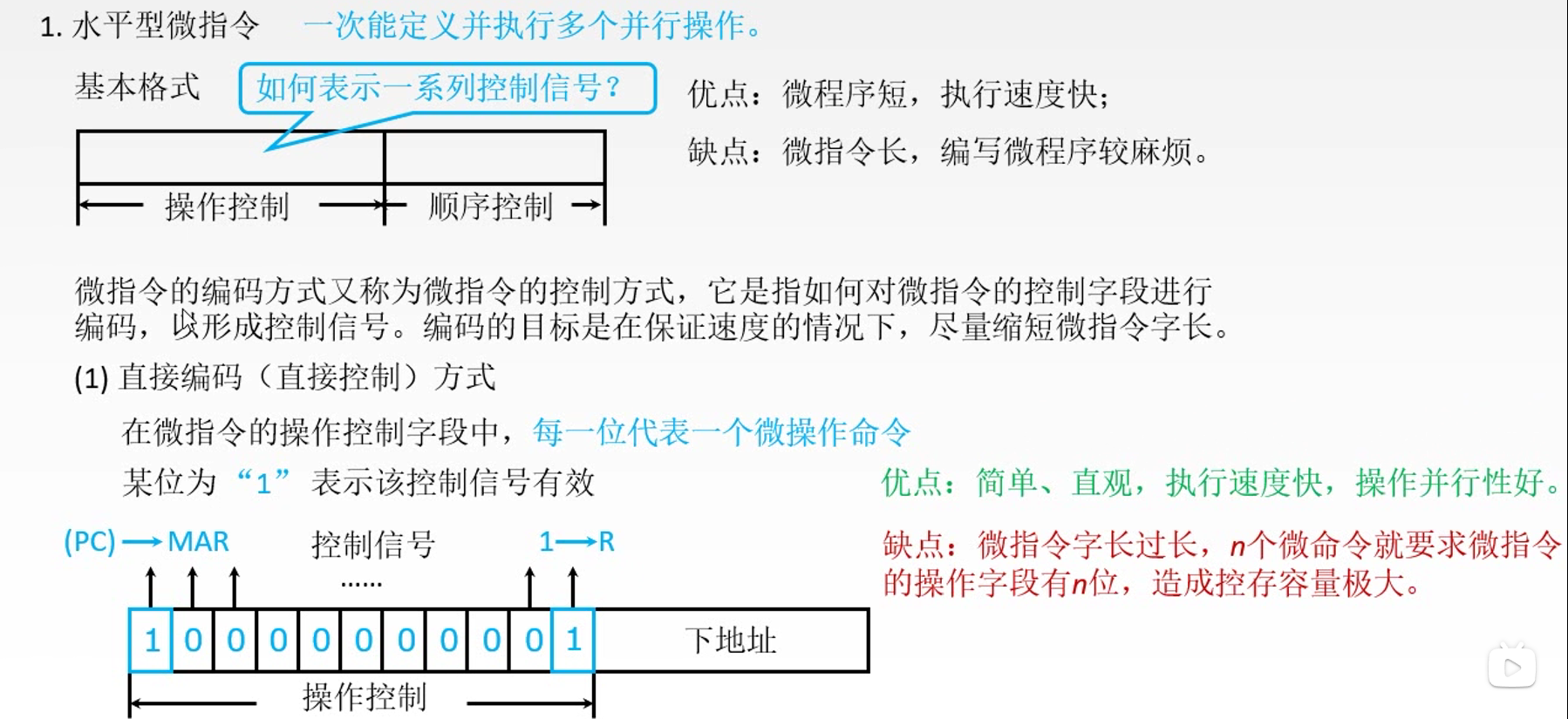

《微指令的格式》

解释:

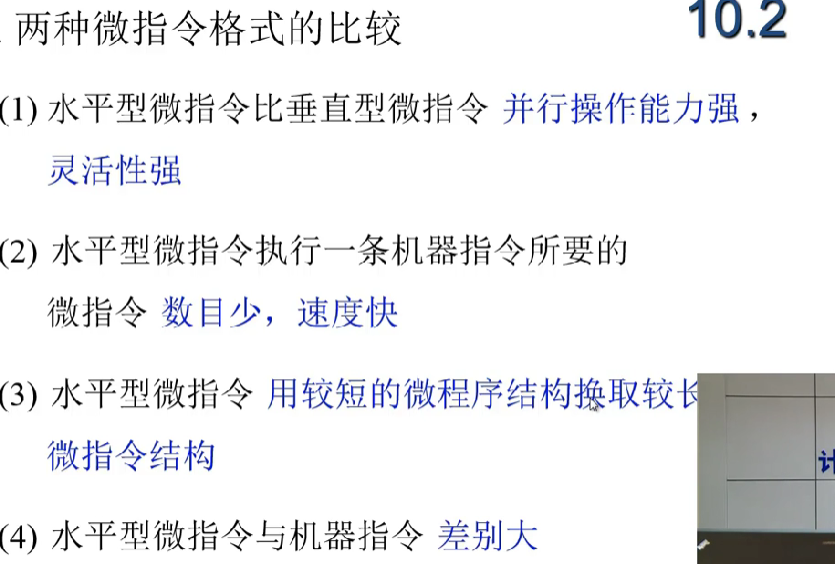

水平型微指令其编码方式是通过二进制下某一位为0/1来决定是否执行某一个微操作

所以水平型微指令会较长一点

但是其能够并行完成微操作,所以微程序会更短一点

垂直型微指令其编码方式是通过n位二进制位有2^n种状态,每一个状态来决定一个微操作

所以垂直型微指令会较短一点

但是其不能并行执行微操作,所以其微程序会更长一点

《水平微指令的编码》

《直接编码》

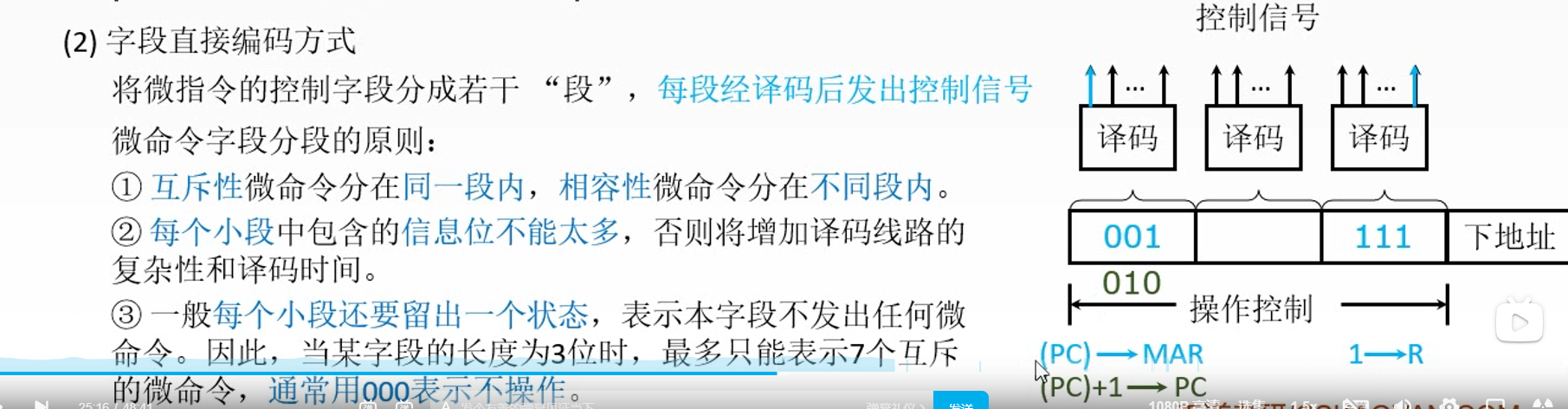

《字段直接编码》

互斥性微命令分在同一段内,相容性微命令分在不同段内,

这是因为通过译码每一次只有一个微命令可以执行,

如果将互斥微命令分在不同一段内则可能会导致微命令的互斥,

也会导致本来可以同时进行的微命令而不会同时进行

这个设计思想的核心是以如n位二进制可以表达2^n的状态,则这一点可以用来表示2^n的微命令

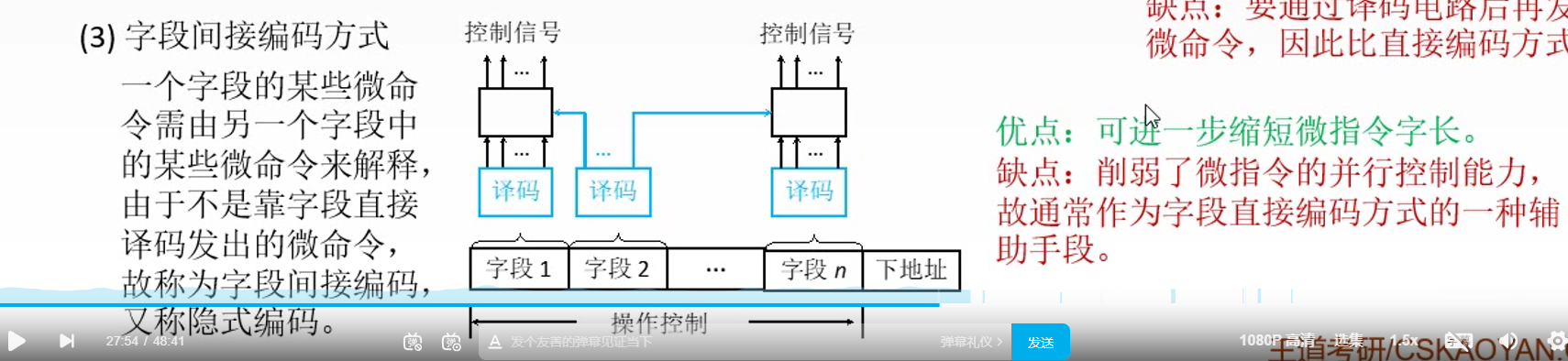

《字段间接编码方式》

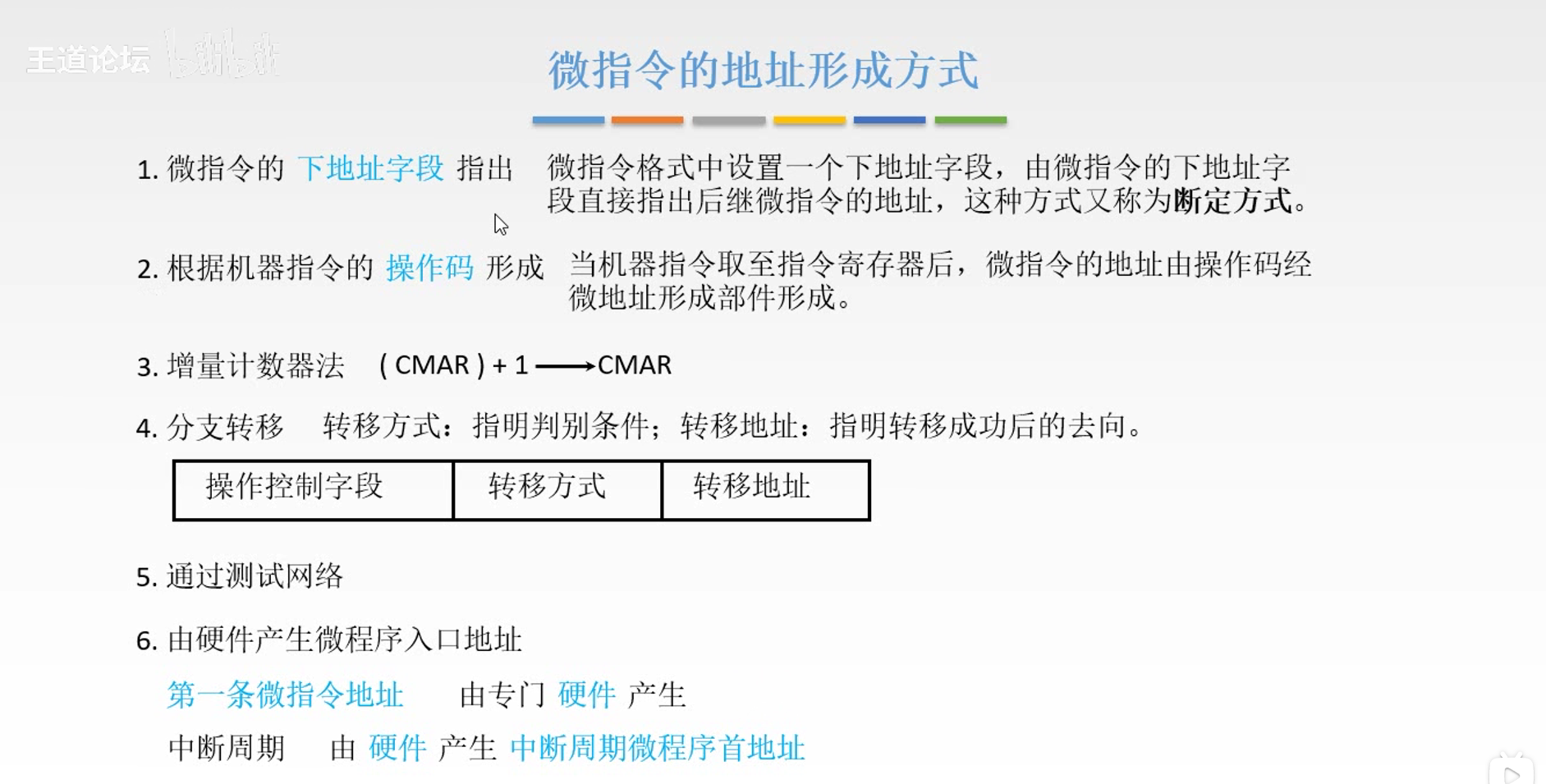

《微指令的地址形成方式》

写题记录:

解:

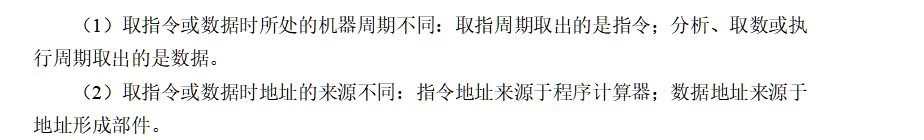

对于第4问很容易答成:通过CU来识别主存储器

这里要说明具体是如何识别的

浙公网安备 33010602011771号

浙公网安备 33010602011771号