简单计算机模型MARIE

CPU

CPU中的寄存器

- 保存数据、地址、控制信息

- 常见:存储信息的寄存器、数值移位的寄存器、数值比较的寄存器、计数寄存器、存储中间结果的寄存器、控制循环的索引寄存器、管理处理堆栈的堆栈指针寄存器、保持各种工作状态和操作模式溢出进位的寄存器、和给程序员使用的通用寄存器。

CPU中的算数逻辑单元ALU

- 执行逻辑运算和算数运算

- 通过控制单元发出的信号,ALU可以执行规定的计算

- 在ALU执行的操作会影响状态寄存器的某些数据位(状态寄存器存放特殊的操作状态,溢出进位借位等等),指示是否有溢出等发生

CPU中的控制单元

- 取指令:使用程序计数器PC确定要执行哪一条指令

- 指令译码:确保数据适合时间出现在正确的地方

- 通知ALU使用哪一个寄存器,执行哪些中断服务程序

总线

多条线路组成,允许多位数据并行传递

总线周期:完成总线信息传送所需的时钟脉冲间隔

总线分类有哪些?

- 按照对象个数分为:点对点和多点总线

- 按照功能分为:数据总线、控制总线、地址总线、电源线

- 按照传输的信息种类黑使用的设备不同分为:

- 处理器内存总线:比较短,告诉总线,通常是专门设计的,最大限度提高带宽

- IO总线:允许多种类型的不同带宽,兼容性强

- 底板总线:主板上的总线,供所有设备连接使用

- 按照相对内外分为:

- 系统总线:CPU内存等内部组件

- 外部总线(扩展总线):外围设备,扩展插槽

- 局部总线:外设直接和CPU数据总线相连

- 按照时序来分:

- 同步总线:时钟控制,脉冲来到时事件才会发生,顺序由时钟脉冲决定,设备之间由时钟频率来同步,总线的周期时间是时钟频率的倒数,任何的时钟偏移(时钟浮动)都导致问题,总线缩短时间浮动就不会太大。注意总线周期不能短于信息在总线上传递的时间。总线长度限制了总线频率

- 异步总线:协议控制,各控制线通过异步总线相互协调

总线仲裁是什么?

任何时刻总线只可以被一个设备使用,只有主控设备可以保留总线,从设备通过响应主控设备来读写数据。对有多个主控设备的系统来说,需要总线仲裁机制保证所有主控设备都可以使用总线

- 菊花链仲裁方式:优先级来轮流,可能饿死

- 集中式并行仲裁方式:

- 自选择分配式:

- 采用冲突检查的分配式:

时钟

- 控制指令的执行速度,脉冲到达时才可以执行操作,对系统各部件进行协调,就像一个交响乐的指挥。

- 特定指令执行需要固定的时钟周期数,指令执行的速度通过时钟周期的数目来测量,而不是秒。(记住周期是频率的倒数)

- 大多计算机只有一个主控时钟,按照规定时间间隔发送脉冲,各寄存器必须等待脉冲发生才可以输入新的数据

时钟周期和电路传输延迟之间什么关系?

- 提高时钟速度被在寄存器之间传递所需要的时间间隔限制,否则会数据丢失,最小时钟周期应该大于寄存器之间传递数据所需要的时间间隔(电路最大传输延迟)

- 电路最大传输延迟可以通过添加寄存器来减小,但是这会使时钟周期数增加

- 相同的时钟速度,新的处理器比旧的可以完成更多的指令,即执行一个相同的指令需要更少的周期数

系统时钟和总线时钟的关系?

系统时钟是控制CPU和其他部件的主控时钟,快于总线时钟,造成系统瓶颈

什么是超频?

使得部件的工作频率高于厂家给出的频率,这样有可能会发生时序故障(相当于改变时钟周期),可能过热,总线超频可能损坏连接的部件,工作不稳定

输入输出子系统

通常通过接口和CPU相连,接口(IO寄存器)负责信号转换,

CPU与接口(IO寄存器)的数据交换方式?

- 基于存储器来映射IO:存储器存放IO寄存器的地址,通过内存即可找到寄存器,在找到IO设备

- 基于指令的IO:CPU有输入输出专用指令,不使用内存

存储器

如何设计存储器?

分为多行,一行一个寄存器,一个寄存器有一个地址(无符号整数),按字节编址,64位系统一个时钟周期可以处理8个字节

如何编址?

- 按字编址:编址的间隔大小

- 按字节编址:大多计算器还是按字节编址的

按字寻址和按字节寻址指的是寻找的时候每次跨越的间隔,按字节就是一次8位来寻找地址,按字就是每一个字对应的大小间隔来寻找地址。

什么是内存存储里面的对齐问题?

如果是按字节编址,且计算机字长大于8(意味着可以存储多余8位的数),则读取一个32位长的字,读取的时候要确保字存储在自然对齐的边界上,并且访问从边界开始。

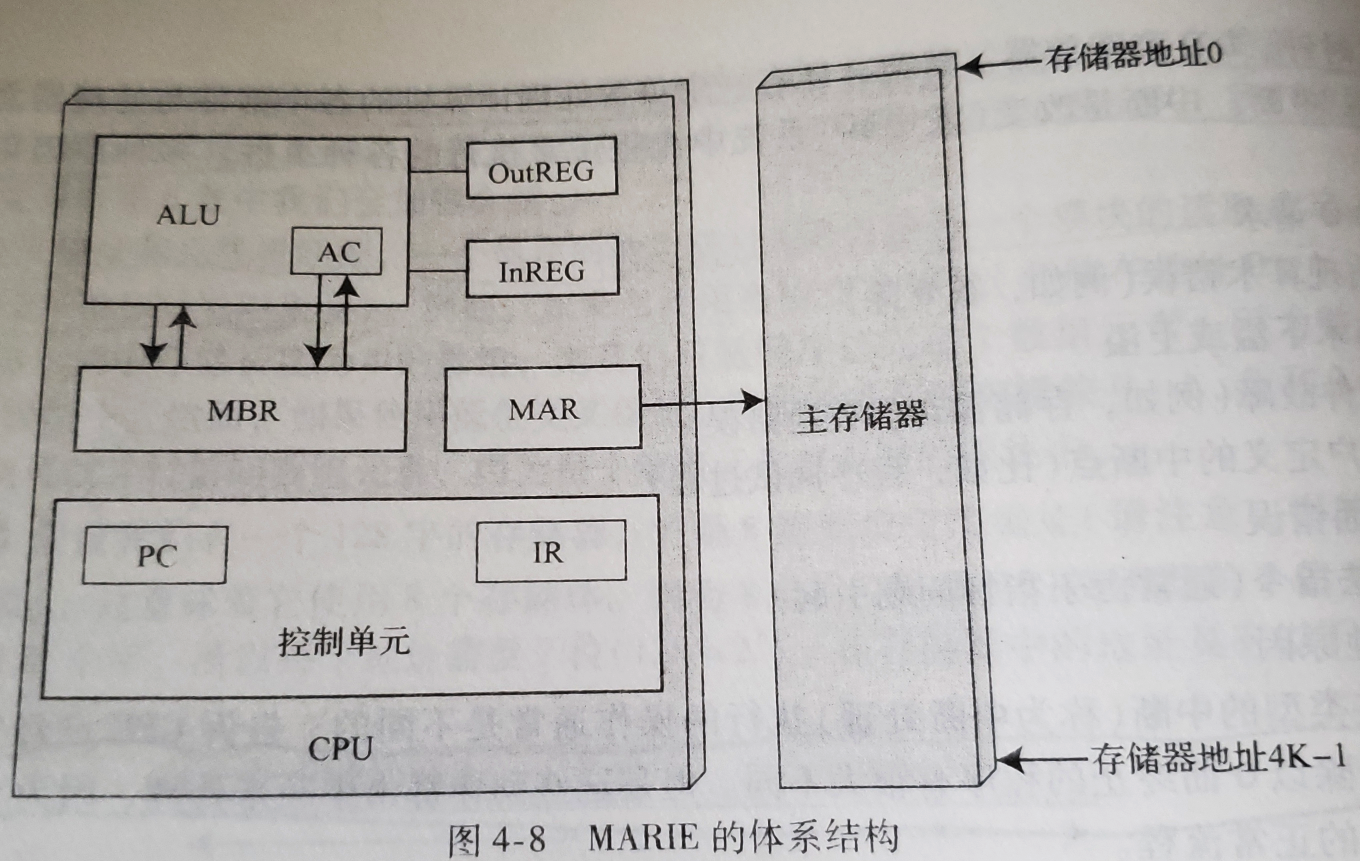

MARIE

MARIE是一个简单的计算机体系结构

MARIE中的寄存器

- AC:累加器,是通用寄存器,保存CPU需要处理的数据

- MAR:存储器地址寄存器,保存所引用数据的存储器地址

- MBR:存储器缓存寄存器,从存储器读取或要写入的数据

- PC:程序计数器,用来存放下一条执行指令的地址

- IR:指令寄存器保存将要执行的指令

- InREG:输入寄存器保存来自输入设备的数据

- OutREG:输出寄存器,保存要输出到到输出设备的数据

MARIE的指令集架构ISA?

ISA指定计算可以执行的指令以及指令的格式,ISA的本质是软件和硬件之间的接口,有些机器的指令集架构包括几百个指令,每一条指令16位

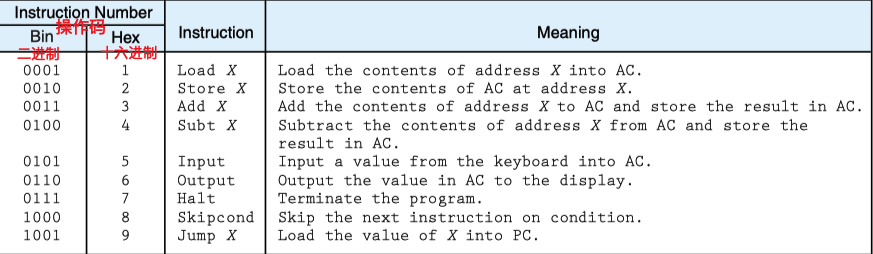

MARIE 的指令集组成

注意下面X是地址,不是要处理的值,指令中都是地址,不是待处理的值

如上图所示,二进制指令就是机器指令,相应的助记符就是汇编指令,二者之间有一一对应关系,转换需要汇编器来完成

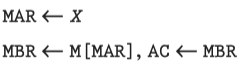

什么是微操作?

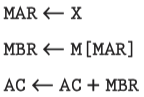

上面的汇编的代码在执行的时候还是会细分为多个步骤,这每一个步骤就是一个微操作,例如Load X,先把X放到MAR,再从存储器取回数据放到MBR,再把MBR的数据加载到AC。寄存器之间的数据传输还要依靠总线来完成。微指令规定了对寄存器中存储的数据执行的基本操作

如何表示微操作?

微操作的符号表示叫做寄存器传输表示法(RTN)或寄存器传输语言(RTL)。

M[X]表示存储在X地址的数据<-表示数据传送方向。

| Load X |  |

两个总线周期,IR将X放入MBR是一个总线周期,取回数据到MBR由于MBR与AC之间有专门线路所以合起来是一个总线周期。 |

|---|---|---|

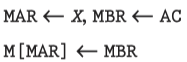

| Store X |  |

AC 的值存到存储器 |

| Add X |  |

存储器的X位置的值加到AC的值 |

| Subt X | 同理 | 同理 |

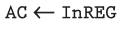

| Input |  |

输入设备的任何输入先到InREG。再到AC |

| Output |  |

|

| Halt | 不对寄存器执行操作 | 机器只是停止执行 |

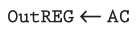

| SkipCond |  |

有条件地跳过下一条指令, 指令中的地址的第10、11位确定AC上执行何种比较,也就是,操作码的相邻两位。 指令的跳过是通过程序计数器PC+1来完成的 |

| Jump X |  |

转向地址X的无条件分支转移 |

| JnS X | MBR ← PC MAR ← X M[MAR] ← MBR MBR ← X AC ← 1 AC ← AC + MBR PC ← AC |

下一条要执行的指令放入存储器汇中X位置,程序计数器存入X地址下一条的指令 将PC内容复制到地址X处,PC调到X+1处 |

| Clear | AC ← 0 | AC清零所有位 |

| AddI X | MAR ← X MBR ← M[MAR] MAR ← MBR MBR ← M[MAR] AC ← AC + MBR |

间接寻址之后相加, 通过X来找需要处理数据的地址,之后累加 |

| JumpI X | MAR ← X MBR ← M[MAR] PC ← MBR |

间接跳转 |

MARIE顺序执行指令时的流程?

(汇编指令经过汇编器转换为机器码,)机器码在执行的时候先要译码,找出对应的操作码和要操作数据存放的地址,译码得到对应的操作根据操作将其分解为不同的微操作RTN,一步一步执行微操作,循环以上步骤即可顺序执行内存地址里面的二进制指令。

指令的执行过程是什么?

- 取指

MAR <- PCIR <- M[MAR]PC <- PC+1

- 译码

MAR <- IR[11-0]IR[15-12]

- 执行周期

MBR <- M[MAR]- 执行指令

中断是什么?

中断取指-译指-执行周期的正常流程,转去执行其他操作

为什么使用中断的方式而不是轮询的方式?

很多时候没有需要完成的任务,不断轮询会浪费资源,中断使得CPU只需在特定时刻需要注意相应的设备,无需CPU监视

中断的分类有哪些?

- 硬件中断

- 可以是任何外设产生

- 软件中断

- 常叫做陷阱或者异常,使用中断处理程序(ISR****)来支持中断。

中断的执行流程是什么?

- 把触发中断的设备ID或中断请求号作为索引去查询中断向量表(一般保存在存储空间的低地址区域)。查询中断服务的程序的入口地址,即地址向量,即中断处理程序的ISR的地址

- 将地址向量存到PC程序计数器,开始执行中断服务

译码方式该如何权衡?

- 硬连线控制(hardwired control):物理上将各条控制线与实际的机器指令连接。速度快,电路复杂,设计修改困难。

- 微编程(microprogramming):所有机器指令被放置到微程序中,将指令转换成规定的控制信号。微程序是一个用微代码编写的翻译器,被存储在计算机固件(ROM、PROM、EPROM等)中,称为控制存储器。设计灵活简单,有助于设计功能强大的指令集。每条指令都需要经过一次额外的翻译过程,会减缓整个程序执行速度。

实际的计算机体系结构

Intel体系结构(CISC复杂指令集)

- CISC机器有数目庞大、长度各异、设计复杂的指令系统,多数指令非常复杂,这些复杂指令的一个小子集就可能显著减慢CPU运行速度。

MIPS体系结构(RISC精简指令集)

- RISC机器主要目的是简化指令,对一些小的但是完整的指令硬连线,提高指令执行速度。在RISC系统中,每条指令只执行一个操作,所有指令长度相同只是格式略有差别,所有算术运算在寄存器之间执行,存储器中的数据不能用作操作数。1982年后,所有新设计的指令系统基本都属于RISC结构或CISC和RISC组合结构。

posted on 2025-10-12 19:20 chuchengzhi 阅读(25) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号