verilog语法与碰见的问题

always模块是循环执行的

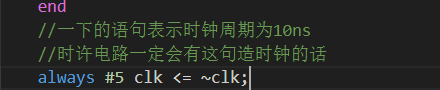

时许电路经常需要一个造时钟的语句

initial模块只会执行一次,是规定仿真开始前的东西的

wire类型只能被assign语句赋值

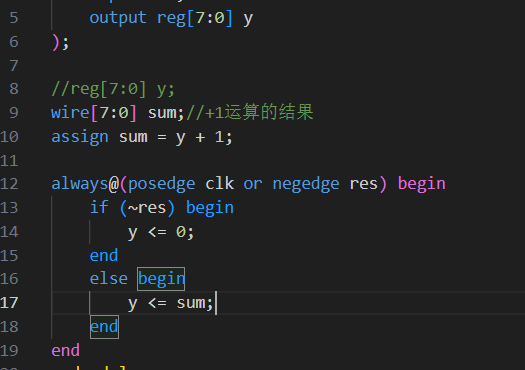

如果要在always内部给一个值赋值,那么应该给其定义为reg类型

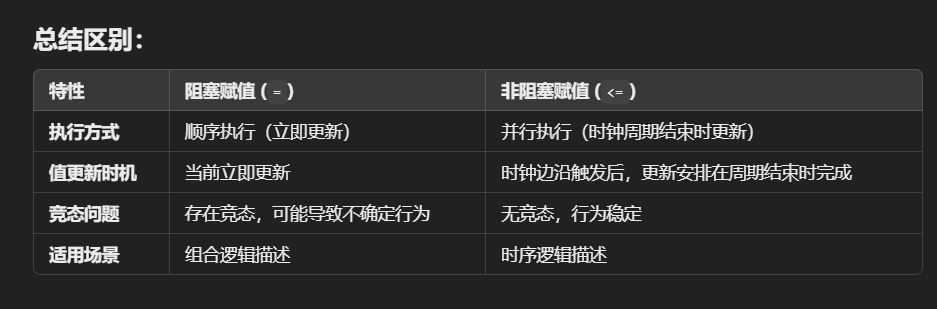

=用于组合逻辑,<=用于时序电路(也就是并行的)

reg类型一般在always内部改变,而且没有行为的时候是保持不变的

相乘和相加确定位数,相乘是两者的位数相加,相加是两者的最大值加1

注意casez的用法,可以用z代表我不关注的位

我们应当让输出处在一个确定的状态,在组合逻辑中应当尽量避免latch(锁存器)的产生,这会导致电路变复杂,而且输出不定。

时许电路不管是同步还是异步一般都是延迟一个周期的

同步和异步的区别就只有rst开始的时候是不是同步的,后面的回复都是同步的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号