ICG cell的用途和危害

数字后端在使用ICG cell带来的收益和危害

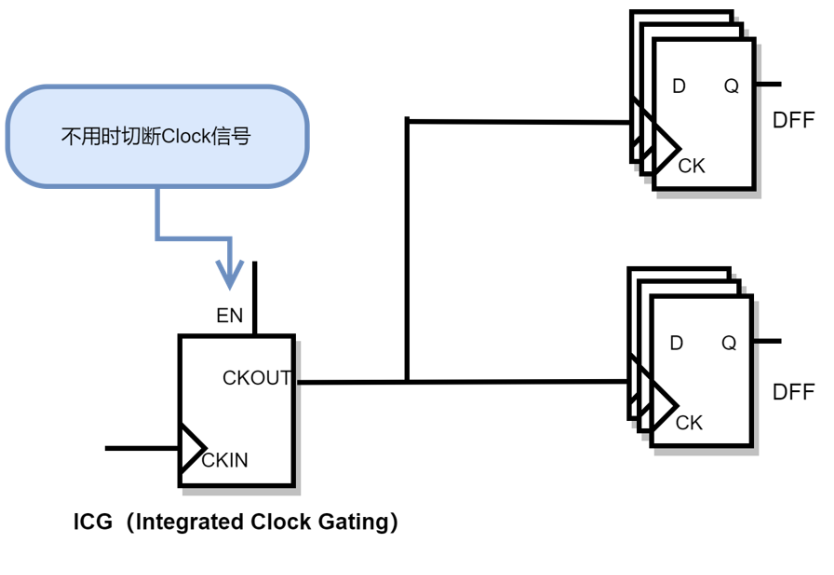

ICG :Integrated Clock Gating cell(集成时钟门控单元)

在数字后端中主要用来通过控制CLK的翻转频率降低动态功耗。

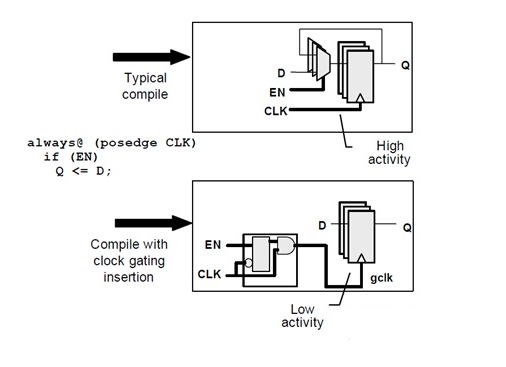

那么ICG在电路中是怎么插入使用的呢?

下图是在RTL中ICG cell的插入;

可以看到的是在原有的CLK端之前增加了一个EN端;

这个EN端就用来控制CLK信号的输出;

----分割线

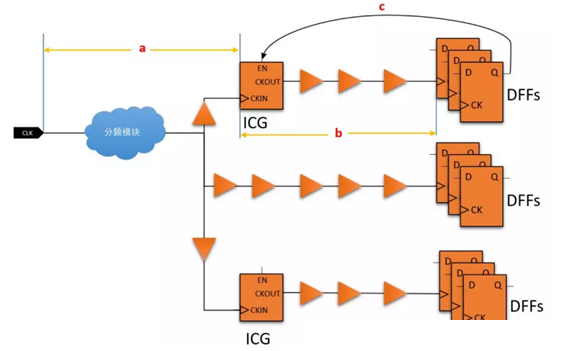

在后端设计中带有ICG的部分,主要会影响CLK tree;具体怎么影响的看下面解释:

因为ICG在CTS中不是REG和IP端口,所以tool不会把它认为是一个sink点,所以不会被balance,只是会through过去,所以会出现如下的现象:

由上图可以看出,在分析DFF到ICG的setup timing时:

launck clk delay = a + bcapture clk delay = a

因此,对于ICG的setup path,天然存在clock skew:b ,而skew的大小完全取决于ICG距离sink DFF有多远。

在出现setup violation的ICG path上,比较多见的就是因为ICG和sink DFF的clock之间存在较多逻辑或者物理上距离较远,从而导致skew较大而发生setup violation。

针对这种现象,

(1) 在实际设计中,我们可能会考虑将出现setup violation的ICG尽量放在sink DFF附近以减小skew。

(2)与此同时,EDA工具也提供命令来收紧ICG的timing constraint来迫使工具来优化这些path,比如set_clock_gating_check命令。

另外,CTS工具会对其做clone、declone操作。

ICG cell Clone:

受相同ICG cell控制的时序单元较多或者分布不均匀时,就会导致ICG cell连线过长,这时可通过clone ICG cell进行优化;

ICG cell De-Clone:

受相同ICG cell控制的时序单元较少,就会导致ICG cell数量过多,设计density增大。这时可通过De-clone ICG cell进行优化;

比如:set_clock_gating_check 命令,其实也是对data path路径的优化。

在place之前 :set_clock_gating_check

在CTS之后 :reset_clock_gating_check为default

注:CTS之前设clock gating check为了弥补clock tree, ICG cell的latency较短,所以加一些余量。CTS之后remove_clock_gating_check并不是不让tool做ICG timing check,而是用library的gating check的值。

浙公网安备 33010602011771号

浙公网安备 33010602011771号