时序逻辑

控制进来的信号、控制出去的信号

双稳态结构

D触发器组成 主从结构

setup建立时间 计算(传输延时)

hold on保持时间基本为零(主从结构)

clk-q延时 d--->q输出时间

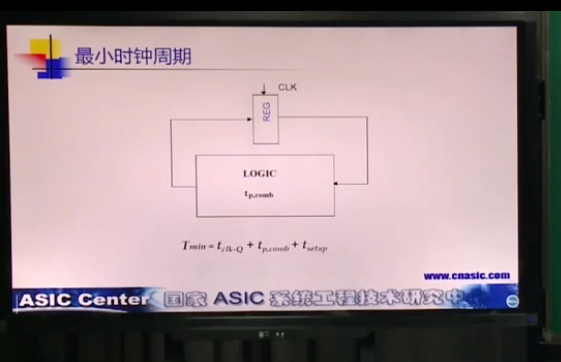

电路最小工作周期:

降低组合逻辑延时:逐级调节晶体管尺寸;调节晶体管顺序;改变逻辑结构(扇出大,延时大);隔离大扇入和大负载

降低setup时间

降低clk-q时间

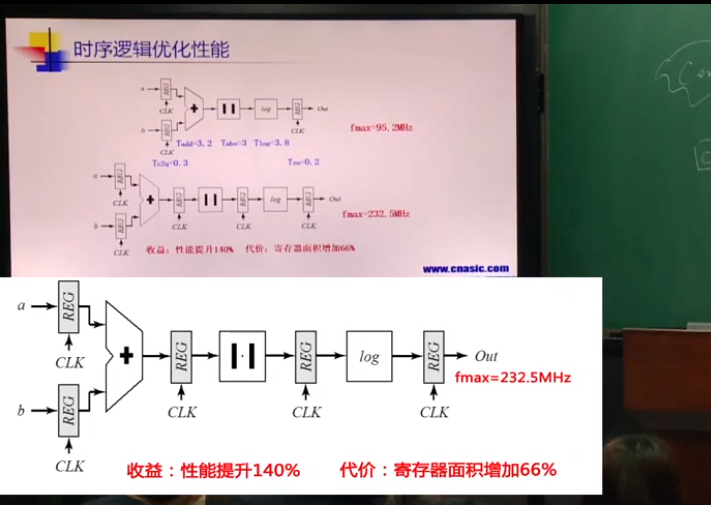

流水线,提高吞吐量

降低触发器功耗:

功耗=静态功耗+动态功耗(电容充放电)

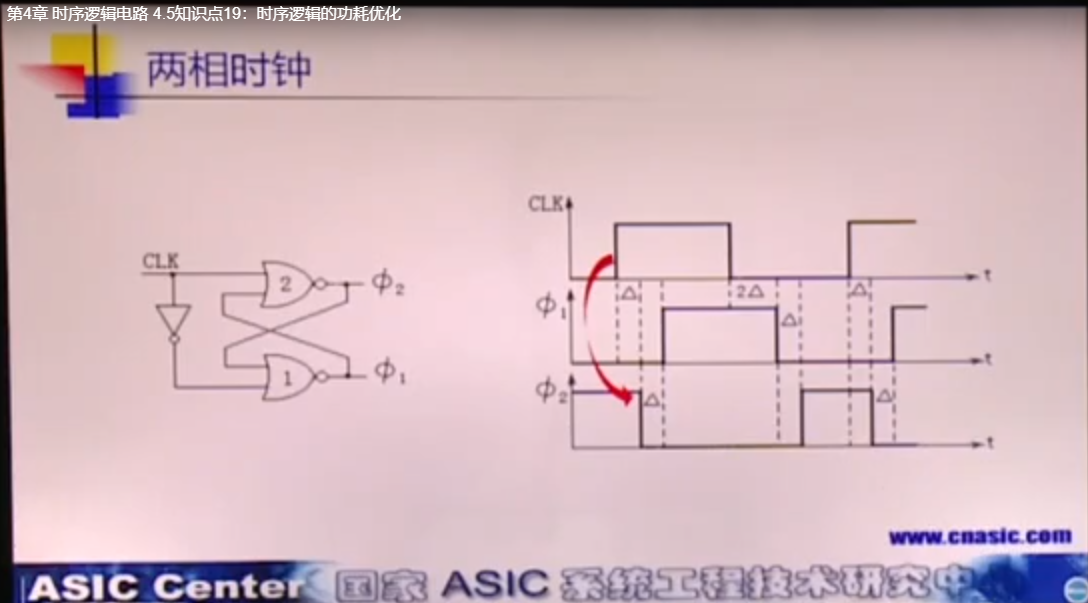

降低时钟频率

偏差和抖动对电路的影响(slew jitter)

1、时钟源有误差

2、buffer、传输门

3、连线(电容、阻)

4、温度

5、门延时不一样

6、电压突变

偏差和抖动对电路时钟周期是有影响的

如果,感到此时的自己很辛苦,那告诉自己:容易走的都是下坡路。坚持住,因为你正在走上坡路,走过去,你就一定会有进步。如果,你正在埋怨命运不眷顾,开导自己:命,是失败者的借口;运,是成功者的谦词。命运从来都是掌握在自己的手中,埋怨,只是一种懦弱的表现;努力,才是人生的态度。

浙公网安备 33010602011771号

浙公网安备 33010602011771号