PCIE背景知识学习(4)

Lane

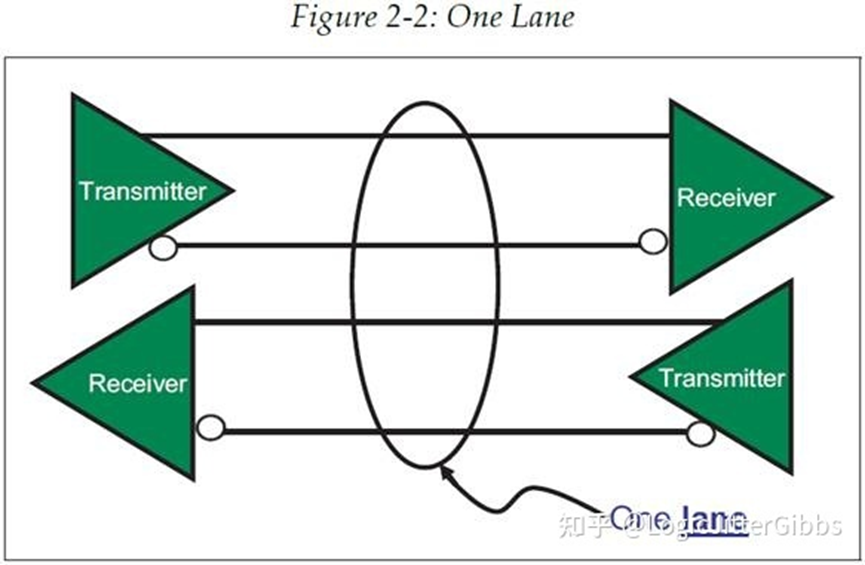

用于描述设备之间信号传输路径的术语为“链路(Link)”,它由一个或以上的接收发送对组成。这样的一对接收和发送被称为一个“通道(Lane)”,协议规范允许一条链路内有 1、2、4、8、12、16 或 32 个通道。链路内通道的数量称为链路宽度,通常用 x1、x2、x4、x8、x16 以及 x32 来进行表示。

带宽

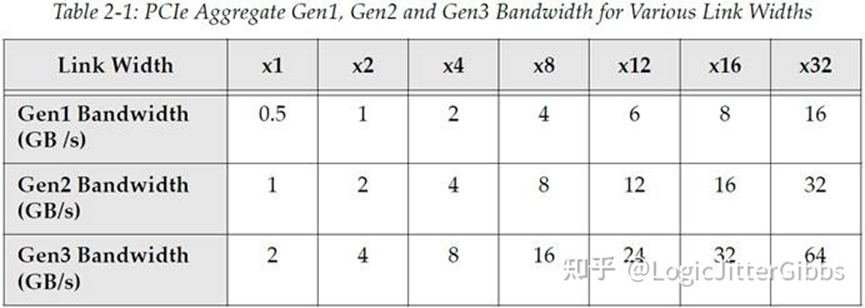

第三代 PCIe(称为 Gen3 或者 PCIe 3.0)再次让带宽翻倍,但是这次协议的制定者们并没有选择将频率翻倍。相反,出于一些原因(我们稍后将会进行讨论),他们仅将频率提升到 8GT/s(Gen2中是 5GT/s,未翻倍),并不再采用 8b/10b 的编码方式,而是采用了另一种编码机制,即 128b/130b 编码

PCIe 带宽计算方法 (PCIe Bandwidth Calculation)

要计算上述表格中的 PCIe 带宽大小,可以参照如下的计算方法。

Gen1 PCIe 带宽 =(2.5Gb/s x 2 directions)/ 10bits per symbol = 0.5GB/s

Gen2 PCIe 带宽 =(5.0Gb/s x 2 directions)/ 10bits per symbol = 1.0GB/s

需要注意,上述计算中,我们是除以 10bits 而不是 8bits,这是因为 Gen1 和 Gen2 的协议中要求将字节进行 8b/10b 编码后进行数据包的传输,因此原数据中的 1 字节在实际传输时其实是需要传输 10 比特。

Gen3 PCIe 带宽 =(8.0Gb/s x 2 directions)/ 8bits per byte = 2.0GB/s

注意到在 Gen3 速率的计算中,我们除以的是 8bits 而不再是 10bits 了,这是因为 Gen3 中不再使用 8b/10b 编码方式,而是 128b/130b 编码方式。这种编码方式每 128位 引入 2 比特开销,这个开销非常小以至于我们暂且可以将它在我们的计算中忽略。

上述三种方法计算出来的带宽只需要再乘以链路宽度即可得到整个多通道链路的链路带宽。

时钟恢复

PCIe 链路不再像 PCI 一样使用公共时钟,它使用了一个源同步模型,这意味着需要由发送端给接收端提供一个时钟来用于对输入数据进行锁存采样。对于 PCIe 链路来说,并不包括输出时钟信号。

相反地,发送端会将时钟通过 8b/10b 编码来嵌入数据流中,然后接收端将会从数据流中恢复出这个时钟,并用于对输入数据进行锁存。

在接收端中,PLL 电路(Phase-Locked Loop 锁相环,如图2‑5)将输入的比特流作为参考时钟,并将其时序或者相位与一个输出时钟相比较,这个输出时钟是 PLL 按照指定频率产生的时钟。也就是说 PLL 自身会产生一个指定频率的输出时钟,然后用比特流作为的参考时钟与自身产生的输出时钟相比较。基于比较的结果,PLL 将会升高或者降低输出时钟的频率,直到所比较的双方达到匹配。此时则可以称 PLL 已锁定,且输出时钟(恢复时钟)的频率已经精确地与发送数据的时钟相匹配。PLL 将会不断地调整恢复时钟,快速补偿修正由温度、电压因素对发送端时钟频率造成的影响。

关于时钟恢复,有一件需要注意的事情,PLL 需要输入端的信号跳变来完成相位比较。如果很长一段时间数据都没有任何跳变,那么 PLL 的恢复时钟可能会偏离正确的时钟频率。为了避免这种问题,8b/10b 编码中的设计目标之一就是要确保比特流中连续的 1 或者 0 的数量不能超过 5 个。

一旦时钟被恢复出来,就可以使用它来锁存输入数据流的比特,并将锁存到的结果给到解串器。有时候学生们可能想知道这个恢复时钟能否作为接收端的所有逻辑所使用的工作时钟,但是这个问题的答案是“不行”。一个原因是,接收端不能指望用于恢复出时钟的比特流参考时钟一直存在且活跃,因为当链路的低功耗状态就包括了停止数据传输,此时必然也就无法继续恢复时钟。因此,接收端必须要有自己本地生成的内部时钟。

浙公网安备 33010602011771号

浙公网安备 33010602011771号