FIFO

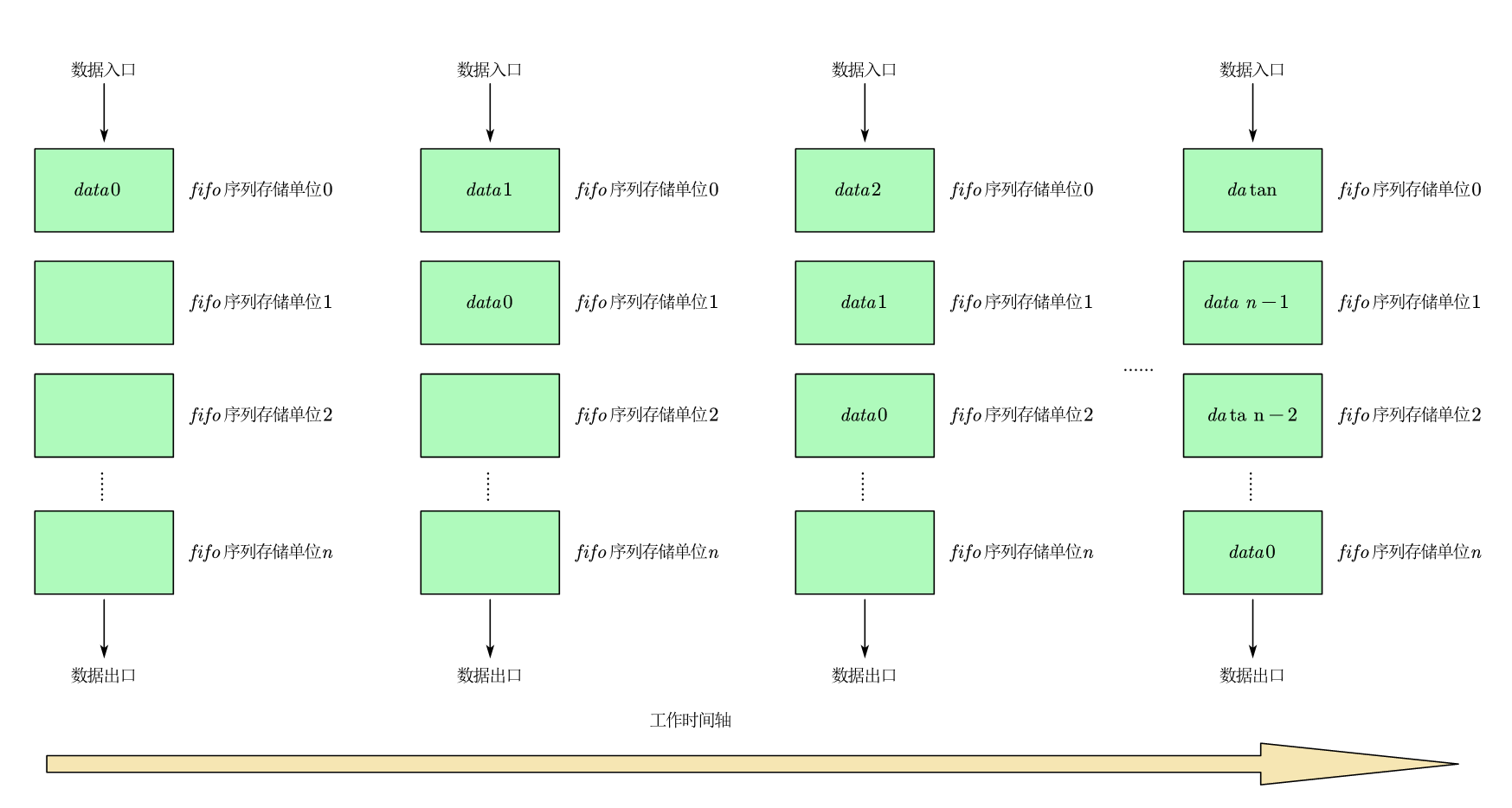

fifo(first in first out)是一种具有特殊结构的存储器,正确来讲是一种数据缓冲器。 它由位宽和深度两个参数来描述这一个存储结构。结构图,以及工作流程可以抽象成以下:

如上图所示,每次进入一个数据,上一位数据都会往下一个存储单元转移。最后,fifo被数据填满之后,读取出来的顺序是由fifo的最后一位出来(数据单向流动),实现数据的先进先出。

类似这一种结构,在软件编程中经常被使用。例如处理器获取一段时间内的采样数据或者信号进行处理,提取特征等等。fifo这一种数据存储结构能最大限度地保留了数据的时间特性。

和RAM不同,fifo是不需要知道数据存储地址的,即可读写操作。因为fifo的数据存放是按照一定顺序排队的,而RAM则是需要知道数据地址的。

FIFO种类

fifo又分为以下三种:

同步fifo

指的是fifo的读操作和写操作,均使用共同时钟源。这一种fifo的读写速率都是一样的。

异步fifo

指的是fifo的读操作和写操作,均使用了两个不同的时钟源。这一种fifo的读写速率都是不一样的。

混合fifo(时钟和位宽不同)

指的是读写速率不一样的fifo(使用了不同的时钟源),而且写入的数据位宽和读出数据位宽也不一样。

使用案例

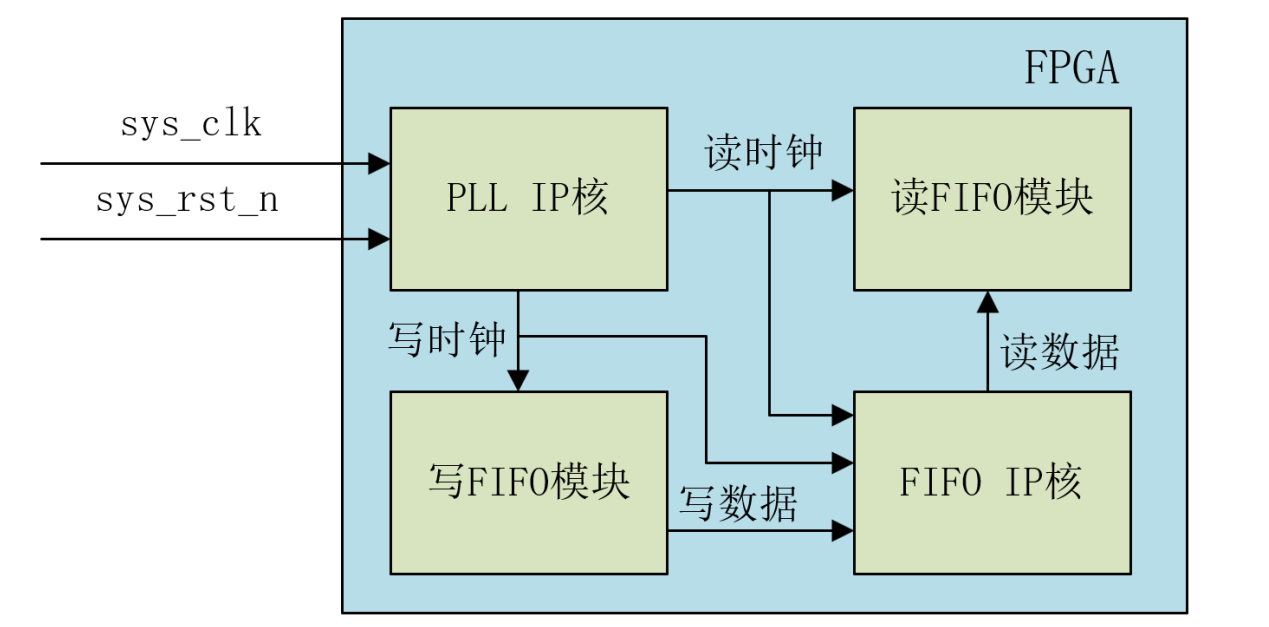

以一个异步fifo为例子,其结构在fpga中如下:

例子中采用了PLL对板子上的50MHz时钟源信号进行2和1分频,得到了25MHz和50MHz的时钟信号。其中,50MHz时钟接入了写fifo模块,25MHz时钟信号接入了读fifo模块。最后,通过fifo的IP核控制fifo的读操作和写操作模块。

作为一个IP核,同样地,此模块也可以在工程中调用出。

用途

fifo因为其特殊的存储结构,特殊的工作方式,被广泛应用在工程上。例如数据需要转化其时钟的时候(由高速率向低速率转化),可以使用fifo作为一些数据的缓冲器。在例如数据的位宽需要转换,假如输入䣌数据宽度为8位一帧,后续电路的数据位是16位,fifo可以先存储好2次收到的8位数据,然后后续电路从fifo读取两次输入的数据,并且对其进行组合成为16位数据再往后续电路进行输出。

注意

当fifo写满,再往fifo里面写数据,则会出现溢出现象,其后果不可估计,可能造成数据丢失。所以在电路设计的时候要注意添加写满防止再写入的功能。

fifo学习,结构以及工作流程原理描述。

fifo学习,结构以及工作流程原理描述。

浙公网安备 33010602011771号

浙公网安备 33010602011771号