RAM

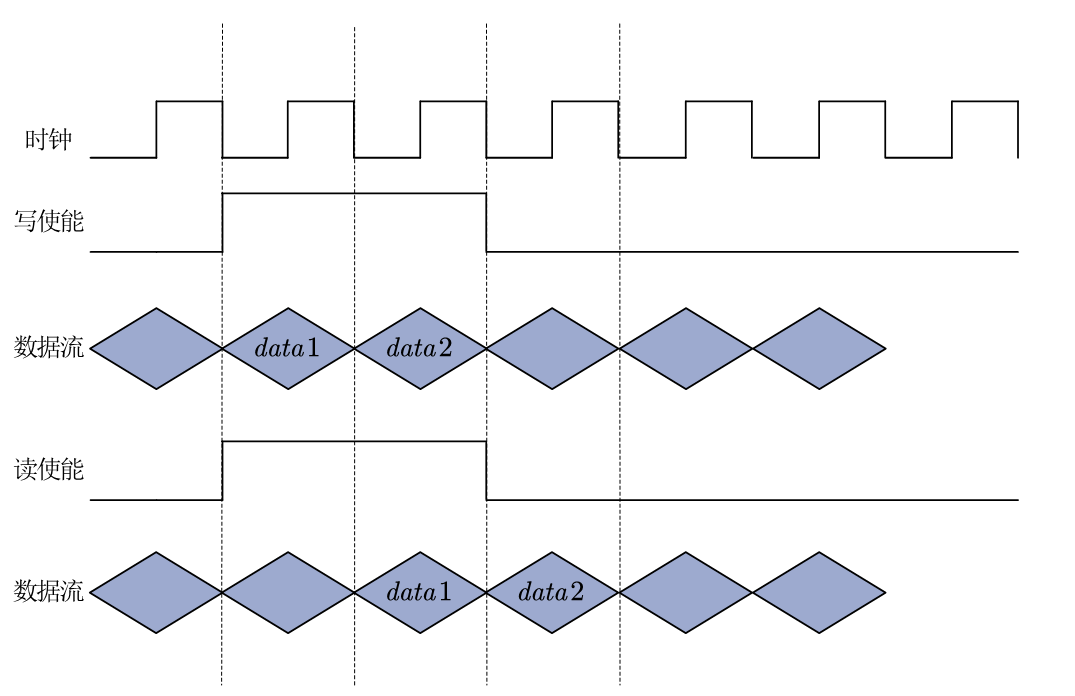

RAM(random access memory)即随机存储内存,这一种存储器在掉电后,数据不能复原,主要用于存储短期数据的电路模块。下面是RAM的读写时序示意图:

如上图所示,在写操作的过程中,当写使能为高电平时,对应的数据才会被存储到RAM里面。在读操作时,当读使能为低电平时,需要延缓一个时钟周期后才有数据输出。

对于RAM这一种存储器,要对其进行读写操作的时候,需要知道将要操作的数据存储地址。和fifo不同,fifo是不需要知道数据地址的(因为fifo的特殊存储结构,是按照顺序排列的)。

单端口RAM

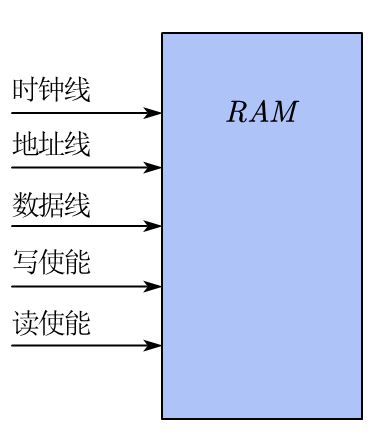

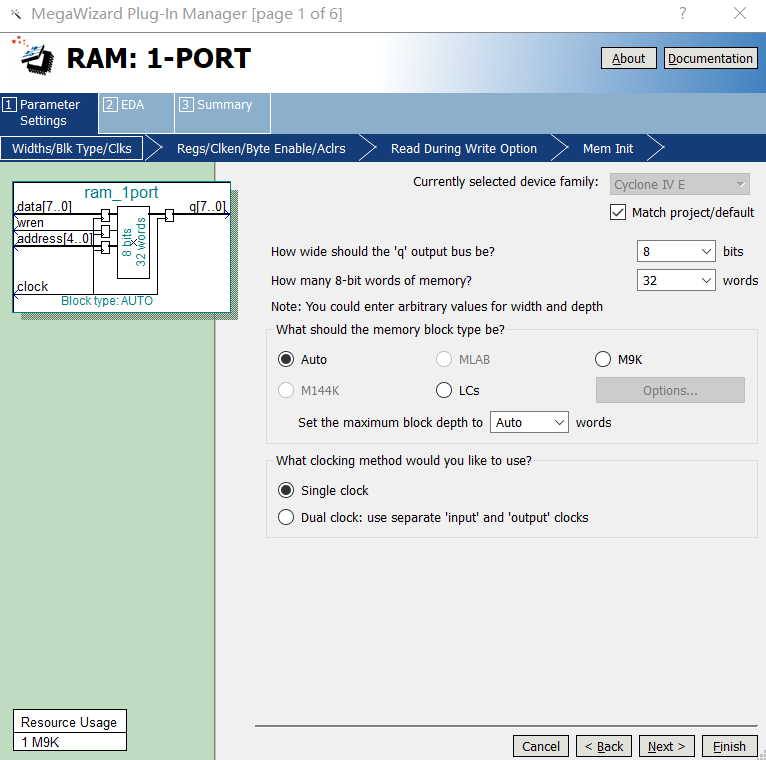

这里以单端ram为例子(只有一个读写端,读写共用一个数据接口)。它的结构如下图所示:一般地,RAM有一条时钟线、一条地址线、一条数据线、一条读使能以及一条写使能(有的读写公用一条线,高电平写,低电平读)。这一种模块的电路工作频率一般根据时钟线决定的,当时钟线频率越高,读写速度就越快。

同样,这一个IP一样可以在工程中被调用。

双端口RAM

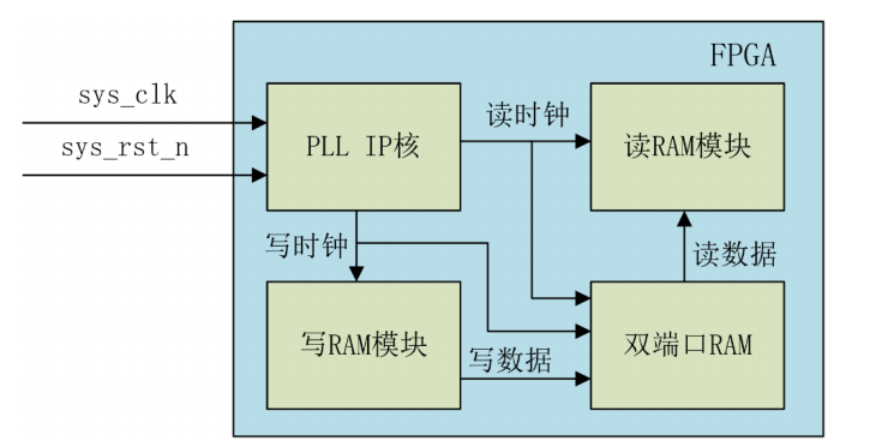

双端口RAM又分为真双端口和假双端口。假双端口(跨时钟域情况下经常使用,使用假双端口的特性,将通过的数据延时输出,使得数据时钟域发生改变以适应后续不同时钟域的电路),是一个端口用于写入数据,一个端口用于读出数据。真双端口是两个端口都可以进行读写操作。下面以假双端口为例子,因为数据写入和读出是分两个端口的。可以使用PLL使得时钟频率分为50MHz和25MHz。设置读取时钟为25MHz,写入时钟为50MHz。

框架图如下:

仿真

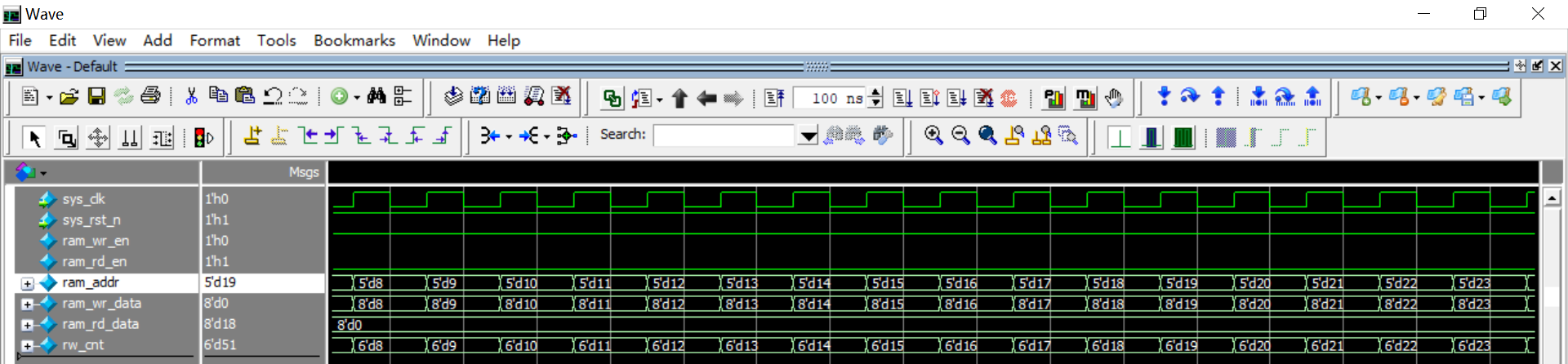

这里使用modelsim对单端口RAM代码进行仿真,仿真过程是:先对RAM写入数据再读出数据一直循环。

RAM学习

RAM学习

浙公网安备 33010602011771号

浙公网安备 33010602011771号